- •Цель работы

- •Постановка задачи

- •1 Мультиплексор 4-1

- •1.1 Таблица истинности

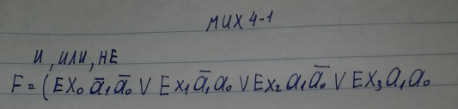

- •1.2 Формула

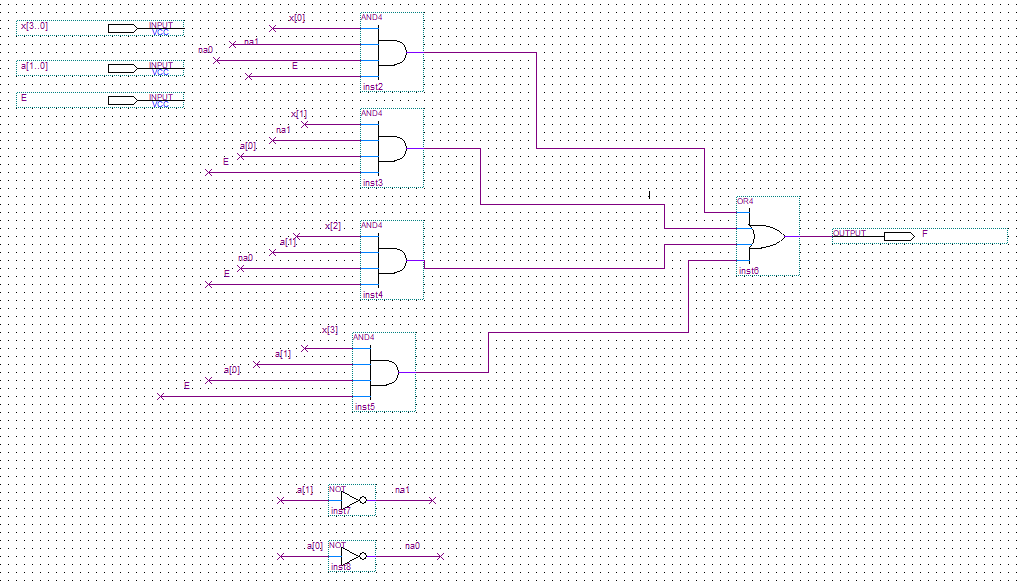

- •1.3 Функциональная схема

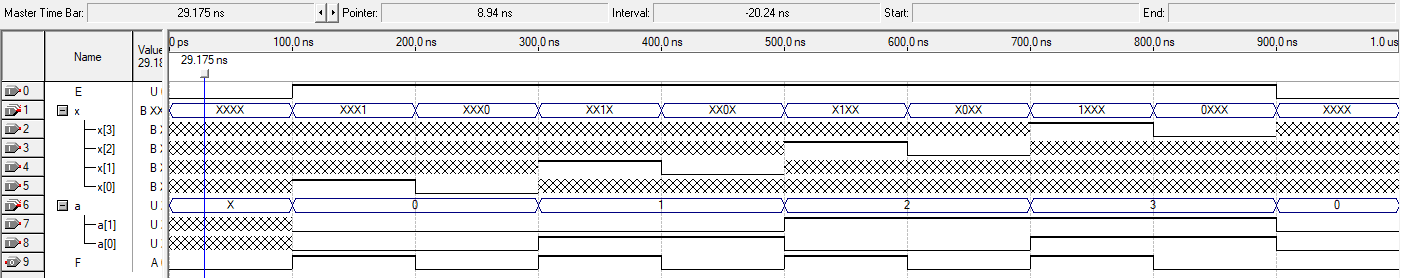

- •1.4 Моделирование функциональной схемы

- •1.6 Схема из rtl viewer для кода hdl

- •1.7 Моделирование устройства, описанного кодом hdl.

- •1.8 Таблица истинности масштабируемого устройства

- •1.9 Функциональная схема масштабируемого устройства

- •1.10 Моделирование масштабируемого устройства

- •1.11 Код на hdl масштабируемого устройства

- •1.12 Схема из rtl viewer для кода hdl масштабируемого устройства

- •1.13 Моделирование масштабируемого устройства, описанного кодом hdl

- •2 Демультиплексор 1-8

- •2.1 Таблица истинности

- •2.2 Формула

- •2.3 Функциональная схема

- •2.4 Моделирование функциональной схемы

- •2.6 Схема из rtl viewer для кода hdl

- •2.7 Моделирование устройства, описанного кодом hdl

- •2.8 Таблица истинности масштабируемого устройства

- •2.9 Функциональная схема масштабируемого устройства

- •2.10 Моделирование масштабируемого устройства

- •2.11 Код на hdl масштабируемого устройства

- •2.12 Схема из rtl viewer для кода hdl масштабируемого устройства

- •2.13 Моделирование масштабируемого устройства, описанного кодом hdl

- •3 Реализация функции на основе мультиплексора

- •3.1 Таблица истинности

- •3.2 Функциональная схема

- •3.4 Моделирование функциональной схемы

- •4 Реализация функции на основе дешифратора

- •4.1 Таблица истинности

- •4.2 Функциональная схема

- •3.4 Моделирование функциональной схемы

Министерство науки и высшего образования Российской Федерации

Федеральное государственное бюджетное образовательное учреждение высшего образования

«ТОМСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ СИСТЕМ УПРАВЛЕНИЯ И РАДИОЭЛЕКТРОНИКИ» (ТУСУР)

Кафедра комплексной информационной безопасности электронно-вычислительных систем (КИБЭВС)

МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТИПЛЕКСОРЫ

Отчет по лабораторной работе №3

по дисциплине «Электроника и схемотехника»

Вариант №7

Студент гр. 739-1

![]() Климанов

М. Д.

Климанов

М. Д.

11.04.2021

Руководитель

Доцент БИС

___________ Мальчуков А.Н.

11.04.2021

Томск 2021

Цель работы

Целью работы является обучение созданию мультиплексоров и демультиплексоров на разных базисах и реализация функции на мультиплексоре и дешифраторе.

Постановка задачи

В ходе данной лабораторной работы требуется выполнить следующие задачи:

1. Составить таблицы истинности для мультиплексора 4-1 в базисе И, ИЛИ, НЕ, демультиплексора 1-8 в базисе ИЛИ-НЕ согласно варианту 7. Написать формулы для всех выходов в СДНФ или СКНФ. Привести формулы к требуемому базису согласно 7 варианту.

2. Собрать схемы на холстах .bdf согласно полученным формулам. Создать блок согласно варианту 7 размерности 8-1 для мультиплексора и 2-16 для демультиплексора на основе полученного блока.

3.

Создать две схемы, которые реализуют

функцию F

=

:

одна схема на основе мультиплексора, а

вторая схема на основе дешифратора.

:

одна схема на основе мультиплексора, а

вторая схема на основе дешифратора.

4. Промоделировать работу всех схем в двух режимах. Сделать предположение, из-за чего возникает разница в результатах моделирования разных режимов и почему.

5. Сверьте результаты моделирования с составленными таблицами истинностями.

6. Повторить п. 2, только для описания устройств вместо схем на холстах .bdf используйте заданный вариантом 7 VHDL. При масштабировании используйте модульное подключение.

7. Написать выводы о проделанной работе.

1 Мультиплексор 4-1

1.1 Таблица истинности

В таблице 1 представлена таблица истинности мультиплексора 4-1.

Таблица 1 – Таблица истинности для мультиплексора 4-1

Мультиплексор 4-1 |

||||||||

Входы |

Выход |

|||||||

E |

x3 |

x2 |

x1 |

x0 |

a1 |

a0 |

F |

|

0 |

x |

x |

x |

x |

x |

x |

0 |

|

1 |

x |

x |

x |

b0 |

0 |

0 |

b0 |

|

1 |

x |

x |

b1 |

x |

0 |

1 |

b1 |

|

1 |

x |

b2 |

x |

x |

1 |

0 |

b2 |

|

1 |

b3 |

x |

x |

x |

1 |

1 |

b3 |

|

1.2 Формула

Ниже представлен рисунок 1 с формулой для мультиплексора 4-1, которая была составлены по таблице истинности 1, также она приведена к нужному базису И, ИЛИ, НЕ.

Рисунок 1 - Формула для мультиплексора 4-1

1.3 Функциональная схема

На рисунке 2 представлена функциональная схема мультиплексора 4-1, составленная на основе формулы из прошлого пункта.

Рисунок 2 – Функциональная схема мультиплексора 4-1

1.4 Моделирование функциональной схемы

На рисунках 3 - 4 представлены результаты временного и функционального моделирований мультиплексора 4-1.

Рисунок 3 – Результат временного моделирования мультиплексора 4-1

Рисунок 4 – Результат функционального моделирования мультиплексора 4-1

Результат временного и функционального моделирования совпадает со значениями из таблицы истинности представленной в таблицей 1.

1.5 Код на HDL

Ниже представлен код описания мультиплексора 4-1 на VHDL.

library IEEE; use IEEE.STD_LOGIC_1164.all;

use IEEE.STD_LOGIC_UNSIGNED.all;

use IEEE.NUMERIC_STD.ALL;

entity mux4_1 is

port (x: in STD_LOGIC_VECTOR (3 downto 0);

A:in STD_LOGIC_VECTOR (1 downto 0);

E: in STD_LOGIC;

F: out STD_LOGIC);

end;

architecture synth of mux4_1 is

begin

F <= x(TO_INTEGER(unsigned(A))) when E='1' else '0';

end;