берчун

.pdf

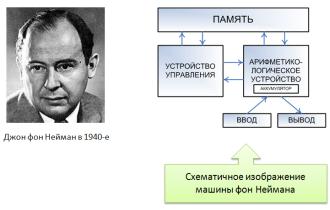

1. Каноническая функциональная структура ЭВМ Джона фон Неймана,

архитектурные принципы.

Архитектура фон Неймана (англ. Von Neumann—широкоarchitecture)известный принци совместного хранения программ и данных в памяти компьютера.такогоВычислит рода часто обозначают термином «Машина фон Неймана», однако, соотве всегда однозначно. В общем случае, когда говорят об архитектуре фон физическое отделение процессорного модуля от устройстврамми данныххранения. прог

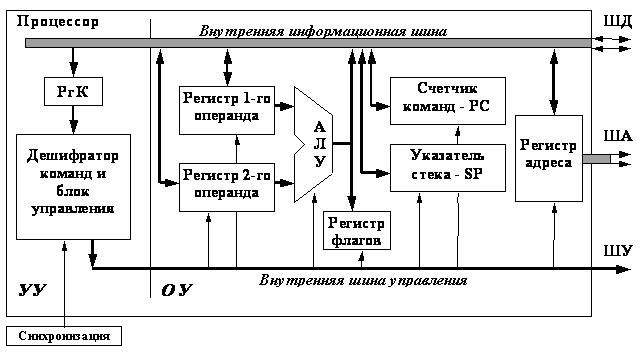

Каноническую функциональную структуру ЭВМ (выше на схеме), связыва Неймана. Структура ЭВМ включает-логарическоефметико устройство (АЛУ), пам запоминающее устройство (ЗУ), устройстваи выввода (УВынформациив) и устройство управления (УУ). Функциональное назначение устройств Э выполнения арифметических и логических операций над данными (опер словами, частности, буквенными последовательностями), ловногоатакже иопе безусловного переходов; ЗУ используется для хранения программ–для и вводапрограмм и данных, –а дляУВывывода из ЭВМ любой информации (в ч результатов); УУ координирует работу всех остальных устройстврамм. при вы Конструкция ЭВМ основывается на предложениях, выдвинутых Дж. фон Neumann, 1903 – 57). Во время разработки машины EDVAC, в середине 1945 г написал -100страничный отчет, суммирующий результаты работ етнадсталЭВМ. известен как первый “набросок” ("First Draft of a Report on the EDVA не достает многих ссылок. Однако в своем отчете Дж. фон Нейман до принципы работы и функциональную структуруprinciplesЭВМ ("theand functionalworkingstructure

of modern computers"). Главное то, что он предложил отказаться о используемых при программировании ENIAC, и хранить программу работы запоминающем устройстве (памяти)роватьи модифицпрограмму с помощью самой же м Опишем архитектурные принципы построения ЭВМ.

1.Программное управление работой ЭВМ. Программы состоят из отдельных– команд; команда осуществляет единичный акт преобразования инфор

2.Условный переход. Это возможность перехода в процессе вычислений на участок программы в зависимости от промежуточных, получаемых результатов (обычно в зависимости от знака результата арифметической операции или от результатаолнениялогическойвып операции).

3.Принцип хранимой программы предопределяет ее запоминание вместе с и данными в одной и той же оперативной памяти.

4.Использование двоичной системы счисления для представления информации в ЭВМ существенно расшириломенклатуруно физических приборов и явлений, для ЭВМ.

5.Иерархичность запоминающих устройств (ЗУ). С самого начала развития существовало несоответствие между быстродействиями АУ и опе Иерархичность ЗУ в ЭВМ является важнымомиссом компрмежду емкостью быстродействием, относительной дешевизной и надежностью.

Эти принципы Дж. фон Неймана, не смотря на свою простоту и оч фундаментальными положениями, определившими на многие годы б вычислительнойикитехни кибернетики.

1. Варианты архитектур ЭВМ: пристонская и гарвардская.

Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются:

1.Хранилище инструкций и хранилище данных представляют собой разные физические устройства.

2.Канал инструкций и канал данных также физически разделены.

Классическая гарвардская архитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий:

1.выборку двух операндов,

2.выбор инструкции и её выполнение,

3.и, наконец, сохранение результата.

Идея, реализованная Эйкеном, заключалась в физическом разделении линий передачи команд и данных. В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие компьютера.

В Гарвардской архитектуре характеристики устройств памяти для инструкций и памяти для данных не требуется иметь общими. В частности, ширина слова, тайминги, технология реализации и структура адресов памяти могут различаться. В некоторых системах инструкции могут храниться в памяти только для чтения, в то время как для сохранения данных обычно требуется память с возможностью чтения и записи. В некоторых системах требуется значительно больше памяти для инструкций, чем памяти для данных, поскольку данные обычно могут подгружатся с внешней или более медленной памяти. Такая потребность увеличивает битность (ширину) шины адреса памяти инструкций по сравнению с шиной адреса памяти данных.

Отличие от архитектуры фон Неймана

В чистой архитектуре фон Неймана процессор одномоментно может либо читать инструкцию, либо читать/записывать единицу данных из/в памяти. То и другое не может происходить одновременно, поскольку инструкции и данные используют одну и ту же системную шину.

А в компьютере с использованием гарвардской архитектуры процессор может читать инструкции и выполнять доступ к памяти данных в то же самое время, даже без кэш-памяти. Таким образом, компьютер с гарвардской архитектурой может быть быстрее (при определенной сложности схемы), поскольку доставка инструкций и доступ к данным не претендуют на один и тот же канал памяти.

Также машина гарвардской архитектуры имеет различные адресные пространства для команд и данных. Так, нулевой адрес инструкций — это не то же самое, что и нулевой адрес данных. Нулевой адрес инструкций может определяться двадцатичетырехбитным значением, в то время как нулевой адрес данных может выглядеть как восьмибитный байт, который не являются частью этого двадцатичетырехбитного значения.

Принстонская архитектура(фон Нейман)

Принстонская архитектура — архитектура микропроцессорной системы с единой шиной для

данных и команд (одношинная архитектура).

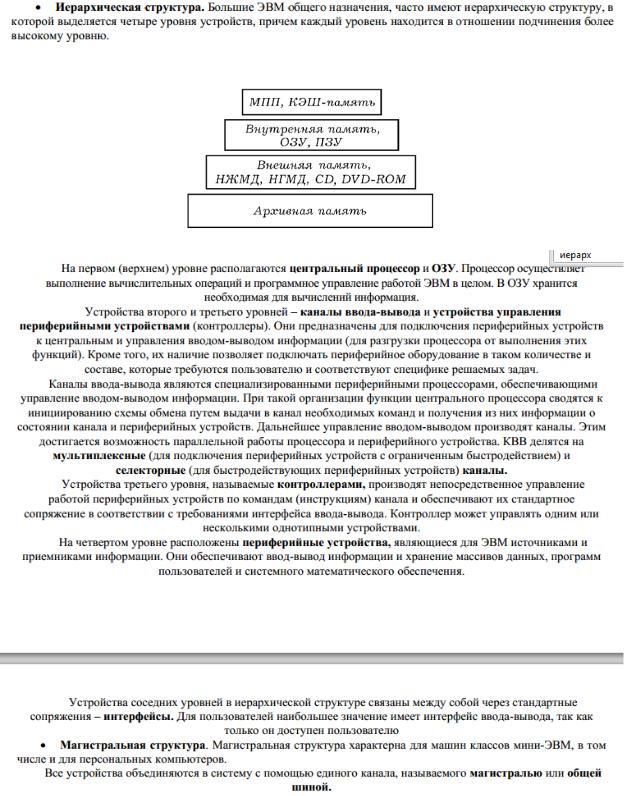

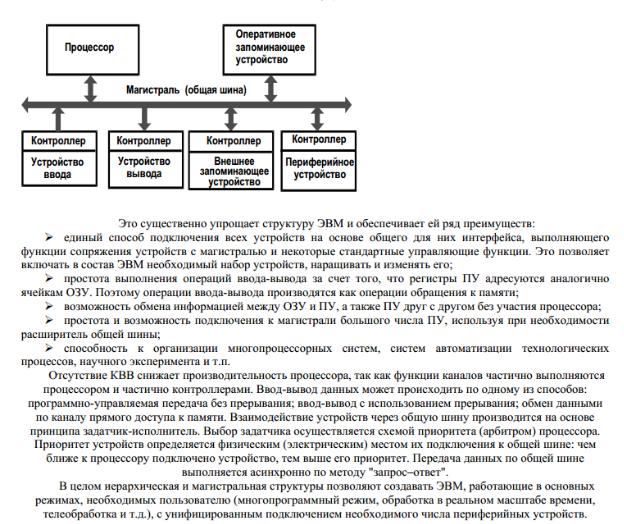

1. Варианты структур ЭВМ: иерархическая и магистральная.

4.Классификация параллельных архитектур по Флинну

Классификация по Флинну

|

|

|

|

Одиночный |

Множество |

|

поток команд |

потоков |

|

(Single |

команд |

|

Instruction) |

(Multiple |

|

|

Instruction) |

|

|

|

|

|

|

Одиночный |

SISD |

MISD |

поток данных |

(ОКОД) |

(МКОД) |

(Single Data) |

|

|

|

|

|

|

|

|

Множество |

SIMD |

MIMD |

потоков |

(ОКМД) |

(МКМД) |

данных |

|

|

(Multiple Data) |

|

|

|

|

|

|

|

|

Основная статья: Таксономия Флинна

Общая классификация архитектур ЭВМ по признакам наличия параллелизма в потоках команд и данных. Была предложена в 70-е годы Майклом Флинном (Michael Flynn). Все разнообразие архитектур ЭВМ в этой таксономии Флинна сводится к четырем классам:

ОКОД — Вычислительная система с одиночным потоком команд и одиночным потоком данных

(SISD, Single Instruction stream over a Single Data stream).

ОКМД — Вычислительная система с одиночным потоком команд и множественным потоком данных

(SIMD, Single Instruction, Multiple Data).

МКОД — Вычислительная система со множественным потоком команд и одиночным потоком данных

(MISD, Multiple Instruction Single Data).

МКМД — Вычислительная система со множественным потоком команд и множественным потоком данных

(MIMD, Multiple Instruction Multiple Data).

Типичными представителями SIMD являются векторные архитектуры. К классу MISD ряд исследователей относит конвейерные ЭВМ, однако это не нашло окончательного признания, поэтому можно считать, что реальных систем — представителей данного класса не существует. Класс MIMD включает в себя многопроцессорные системы, где процессоры обрабатывают множественные потоки данных.

Отношение конкретных машин к конкретному классу сильно зависит от точки зрения исследователя. Так, конвейерные машины могут быть отнесены и к классу SISD (конвейер — единый процессор), и к классу SIMD (векторный поток данных с конвейерным процессором) и к классу MISD (множество процессоров конвейера обрабатывают один поток данных последовательно), и к классу MIMD — как выполнение последовательности различных команд (операций ступеней конвейера) на множественным скалярным потоком данных (вектором).

6. Процессор - это функциональный блок вычислительного устройства, предназначенный для реализации обработки цифровых данных и управления ходом этой обработки. Указанные действия выполняются процессором по командам, которые он автоматически считывает из памяти вычислителя.

В обобщенном виде функционирование процессора может быть представлено как циклическое чередование двух этапов –

(1) выборки (чтения) командиз памяти и их дешифрации, и (2) выполнения команд.

Выборка (чтение) команд является автоматическим процессом, происходящим под воздействием импульсов от генератора тактовых импульсов (ГТИ), и не зависит от программиста в смысле механизма реализации, который жестко определяется аппаратной структурой процессора.

Дешифрация команды представляет собой процесс формирования последовательности управляющих сигналов для всех узлов процессора и других блоков вычислителя на основе информации (т.е. кода), содержащегося в команде.

Действия, выполняемые в соответствии с командой, могут представлять собой арифметическую или

логическую обработку данных, пересылку данных, формирование адреса следующей команды или изменение режимов работы процессора. В любом случае эти действия определяются программистом в рамках имеющейся в его распоряжении системы команд конкретного процессора. После выполнения действий, задаваемых командой, процессор автоматически переходит к выборке следующей команды из памяти.

Современные микропроцессоры существенно различаются набором функциональных блоков и связями между ними. Тем не

менее, в структуре любого процессора можно выделить основные элементы, определяющие специфику процессора как управляющего центра вычислителя. Прежде всего, речь идет о двух блоках: устройстве

управления и операционном устройстве.

Устройство управления (УУ) предназначено для реализации выборки команд, их дешифрации, и на основе этого – для управления обменом и обработкой информации путем генерации последовательности управляющих сигналов.

Операционное устройство (ОУ) служит для обработки цифровой информации (арифметические и логические операции, сдвиги, анализ чисел и т.п.).

Обобщенна структура микропроцессора показана на рис. 3.1.

Рис. 3.1. Обобщенная структура микропроцессора

Основным элементом для хранения информации внутри процессора являются регистры, которые выполняют функцию сверхоперативного ОЗУ с минимальным временем записи и считывания.

Регистр команд РгК (англ. IR - insructionregister) используется для фиксации кода команды после считывания ее из памяти. Как правило, в этом регистре фиксируется лишь код операции (КОП) - часть кода команды, определяющая выполняемое действие и способ адресации операндов (см. ниже).

Регистры операндов служат для хранения данных в процессе их обработки, позволяют избегать постоянных

обращений к памяти. В современных процессорах количество регистров операндов может достигать 10-15 штук. По сути, они образуют внутреннюю память процессора. В однокристальных микроконтроллерах количество

регистров операндов доведено до нескольких десятков, и применительно к ним вводится понятие регистрового

файла.Некоторые из регистров операндов могут использоваться также для хранения или формирования адресов других операндов, т.е. на их основе реализуется механизм косвенной адресации данных в памяти (см. ниже). Данные, размещенные в регистрах операндов, поступают на обработку в арифметико-логическое устройство (АЛУ). В

некоторых типах процессоров один из регистров операндов всегда является и приемником результата операции в АЛУ – такой регистр принято называть регистром-аккумулятором Процессоры, в которых принята схема выполнения

операций в виде:

<аккумулятор> (операция) <операнд> Þ <аккумулятор>,

называются процессорами с аккумуляторно-ориентированной структурой.

Счетчик команд (англ. PC - programmingcounter) - регистр, в котором при выборке или выполнении текущей команды формируется адрес следующей команды. Модификация содержимого регистра PC – это средство управления последовательностью выборки команд из памяти и, следовательно, управления ходом вычислительного процесса (т.е. реализация ветвлений в алгоритмах).

Указатель стека (англ. SP - stackpointer ) - регистр, в котором при выполнении программы хранится адрес границы той области памяти, для которой программист использует принцип последовательного доступа к данным (так называемый протокол работы со стеком).

Регистр адреса - регистр, в котором формируется адрес любого устройства, внешнего по отношению к процессору (ячейки памяти или порта ввода-вывода), перед обращением к этому устройству. Данный регистр необходим, поскольку источником адресной информации могут являться различные регистры процессора. При этом регистр адреса играет роль накапливающего буфера, из которого адресная информация выдается на внешнюю шину адреса.

Регистр признаков (англ. F - flags) - это элемент внутренней памяти, в котором в виде

отдельных битов фиксируются признаки, характеризующие результат операции, выполненной в АЛУ (нулевой результат, переполнение разрядной сетки и т.п.).

Арифметико-логическое устройство (АЛУ) - функциональный блок процессора, предназначенный для реализации действий по обработке данных.

Результат операции, выполненной в АЛУ, заносится в один из регистров или пересылается в память (в зависимости от команды). В регистре признаков автоматически формируются признаки, характеризующие этот результат.

Функционирование процессора всегда синхронизируется от внешнего генератора тактовых импульсов (ГТИ). Именно под влиянием импульсов от ГТИ устройство управления процессора автоматически реализует действия, связанные с выборкой команд из памяти и их дешифрацией.

Выполнение команды всегда занимает некоторое количество периодов тактовой частоты и состоит из последовательности

элементарных действий процессора (выборка команды, чтение операнда, вычисление в АЛУ). Эти элементарные действия называют машинными циклами (МЦ). В течение каждого МЦ происходит генерация строго определенной

комбинации управляющих сигналов для соответствующих узлов процессора и всей вычислительной системы.

7. Понятие операционного и управляющих автоматов.

Как показал академик В.М. Глушков в любом устройстве обработки цифровой информации можно выделить два основных блока — операционный автомат (ОА) и управляющий автомат (УА).

Операционный автомат (ОА) служит для хранения слов информации, выполнения набора микроопераций и вычисления значений логических условий, т.е. операционный автомат является структурой, организованной для выполнения действий над информацией. Микрооперации, выполняемые ОА, задаются множеством управляющих

сигналов Y={y1,....,yM}, с каждым из которых отождествляется определенная микрооперация.

Значения логических условий, вычисляемые в операционном автомате, отображаются множеством осведомительных сигналов X={x1,...,xL}, каждый из которых отождествляется с определенным логическим условием.

Управляющий автомат (УА) генерирует последовательность управляющих сигналов, предписанную микропрограммой и соответствующую значениям логическим условий. Иначе говоря, управляющий автомат задает порядок выполнения действий в ОА, вытекающий из алгоритма выполнения операций. Наименование операции, которую необходимо выполнить в устройстве, определяется кодом g операции, поступающим в УА извне. По отношению к УА

сигналы g1,...,gh, посредством которых кодируется наименование операции и осведомительные сигналы x1,...,xL, формируемые в операционном автомате, играют одинаковую роль: они влияют на порядок выработки управляющих сигналов Y. Поэтому сигналы g1,...,gh и x1,...,xL относятся к одному классу — к классу осведомительных сигналов, поступающих на вход УА.

Т.о. любое операционное устройство — процессор, канал ввода-вывода и т.д. — является композицией операционного и управляющего автоматов. Операционный автомат, реализуя действия над словами информации, является исполнительной частью устройства, работой которого управляет управляющий автомат, генерирующий необходимые последовательности управляющих сигналов.

Операционный и управляющий автоматы могут быть определены своими функциями — перечнем выполняемых ими действий.

Функция ОА определяется следующей совокупностью сведений:

1)множеством входных слов D={d1,...,dH}, вводимых в автомат в качестве операндов;

2)множеством выходных слов R={r1,...,rQ}, представляющих результаты операций;

3)множеством внутренних слов S={s1,...,sN}, используемых для представления информации в процессе выполнения операций. Можно считать, что входные и выходные слова совпадают с определенными внутренними D S, R S.

4)множеством микроопераций Y={ym}, реализующих преобразование S= m(s) над словами информации, где m — вычисляемая функция;

5)множеством логических условий X={xi}, где xi= i(si) и i — булева функция;

T.o. функция ОА задана, если заданы (определены) множества D, R, S, Y, X. Время не является аргументом функции ОА. Функция устанавливает список действий-микроопераций и логических условий, которые может выполнять автомат, но никак не определяет порядок следования этих действий во времени. Т.е. функция ОА характеризует средства, которые могут быть использованы для вычислений, но не сам вычислительный процесс.

Порядок выполнения действий во времени определяется в форме функций управляющего автомата.

Функция управляющего автомата — это операторная схема алгоритма ( микропрограммы), функциональными операторами которой являются символы у1,...,уm, отождествляемые с микрооперациями, и в качестве логических условий используются булевы переменные х1,...,хL. Операторная схема алгоритма наиболее часто представляется в виде граф-схемы алгоритма (ГСА). ГСА определяет вычислительный процесс последовательно во времени, устанавливая порядок проверки логических условий х1-хL и порядок следования микроопераций у1-уm.

8.Жопа)

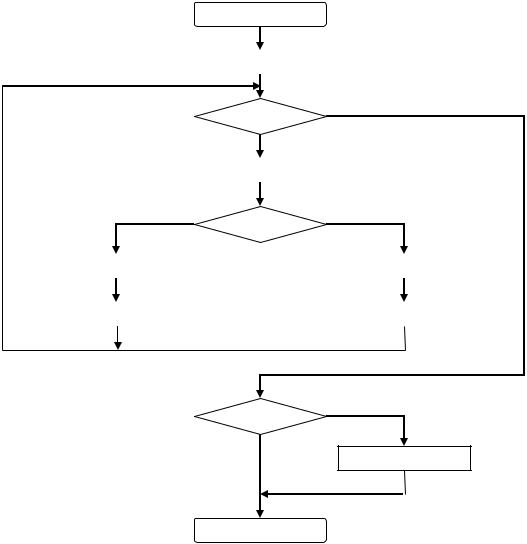

Построим содержательные графы выполнения трёх команд языка Ассемблера:

1. Команда умножения двоичных чисел без знака mul:

|

|

|

|

Начало |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C [0:31]:=000...0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C [26] |

1 |

|

||

|

|

|

|

|

|

|

||

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C [0:31]:=C [0:31] + 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

B [63] |

1 |

|

|||

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

B [33:63]:=B [32:62] |

|

|

|

|

|

B [33:63]:=B [32:62] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

B [1:32]:=B [0:31] + 000…0 |

|

|

|

B [1:32]:=B [0:31] + A [0:31] |

|||

|

|

|

|

|

|

|

|

|

1

П

0

ПП:=1

Конец

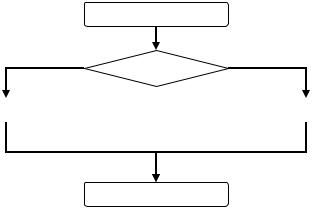

2. Команда преобразования типов cwde:

|

|

Начало |

|

|

1 |

A [0] |

0 |

||

|

|

|

|

|

|

|

|

|

|

B [0:15]:=111…1 |

|

|

|

B [0:15]:=000…0 |

|

|

|

|

|

Конец

3. Логическая команда xor: