берчун

.pdf

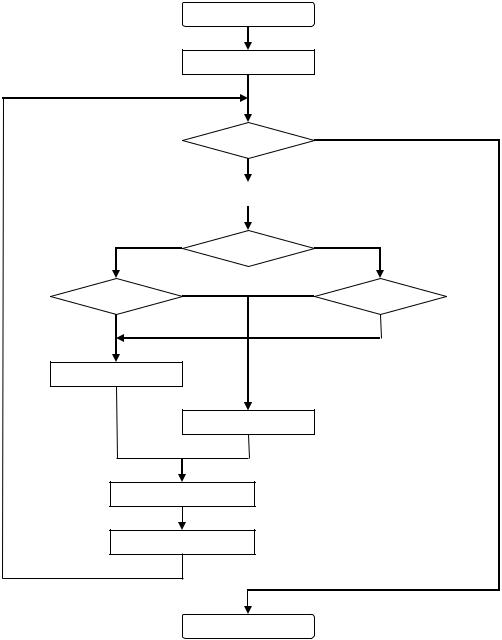

Начало

C [0:31]:=000…0

|

|

C [26] |

|

1 |

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

C [0:31]:=C [0:31] + 1 |

|

|

|

|

|

|

|

|

1 |

A [0] |

|

0 |

|

|

|

|

|

B [0] |

|

1 |

0 |

B [0] |

|

|

|

||

0 |

|

|

|

1 |

A [0]:=1

A [0]:=0

A [0:31]:=A[1:31].A[0]

B [0:31]:=B [1:31].B [0]

Конец

Синтез канонического автомата

Входные и выходные слова:

Тип слова |

Слово |

Комментарий |

|

|

|

Входное/выходное |

A [0:31] |

Первый операнд\результат операции |

|

|

|

Входное/выходное |

B [0:63] |

Второй операнд\результат операции |

|

|

|

Выходное |

С [26] |

Ограничение счётчика числом 32 |

|

|

|

Выходное |

B [63] |

Разряд, анализируемый мультиплексором |

|

|

|

Выходное |

П [0] |

Перенос из старшего разряда младшего слова |

|

|

|

Выходное |

ПП [0] |

Признак переполнения младшего слова |

|

|

|

Выходное |

A [0] |

Старший разряд первого операнда |

|

|

|

Выходное |

B [0] |

Старший разряд второго операнда |

|

|

|

Логические условия:

Обозначение |

Условие |

Комментарий |

|

|

|

X1 |

C [26] |

Ограничение счётчика числом 32 |

|

|

|

X2 |

B [63] |

Разряд, анализируемый мультиплексором |

|

|

|

X3 |

П [0] |

Перенос из старшего разряда младшего слова |

|

|

|

X4 |

ПП [0] |

Признак переполнения младшего слова |

|

|

|

X5 |

A [0] |

Анализ старшего разряда первого операнда |

|

|

|

X6 |

B [0] |

Анализ старшего разряда второго операнда |

|

|

|

Микрооперации:

Обозначение |

Микрооперация |

|

|

Y1 |

C [0:31]:=000…0 |

|

|

Y2 |

C [0:31]:=C [0:31] + 1 |

|

|

Y3 |

B [33:63]:=B [32:62] |

|

|

Y4 |

B [1:32]:=B [0:31] + 000…0 |

|

|

Y5 |

B [1:32]:=B [0:31] + A [0:31] |

|

|

Y6 |

П [0]:=1 |

|

|

Y7 |

ПП [0]:=1 |

|

|

Y8 |

B [0:15]:=111…1 |

|

|

Y9 |

B [0:15]:=000…0 |

|

|

Y10 |

A [0]:=1 |

|

|

Y11 |

A [0]:=0 |

|

|

Y12 |

A [0:31]:=A [1:31].A [0] |

|

|

Y13 |

B [0:31]:=B [1:31].B [0] |

|

|

Построим логическую схему канонического автомата:

1 операнд

1 |

Y10 |

0 |

Y11 |

A [1:31].A [0] |

Y12 |

2 операнд |

|

|

|

B [32:62] |

|

|

Y3 |

0 |

|

|

|

B [0:31] |

|

|

Y4 |

|

|

||

000…0 |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

A [0:31] |

|

|

Y5 |

|

|

||

B [0:31] |

|

|

|

|

|

|

|

|

|

|

|

111…1 |

|

|

|

|

|

|

|

111…1 |

|

|

Y8 |

000…0 |

|

|

Y9 |

B [1:31].B [0] |

|

|

Y13 |

000…0 |

Y1 |

C [0:31]

Y2

1

Y6

Y6

1

Y7

Y7

S

0

A

0

B

A [0:31]

B [0:63]

0 |

B [63] |

|

П [0] |

С

ПП [0]

A [0]

B [0]

П

ПП

S

Синтез М-автомата

Распределение регистров по шинам A1 и A2: A1 (C, B, ПП) и A2 (A).

Операторы, реализуемые М-автоматом:

Ym |

Микрооперации |

A1=Si |

A2=Sj |

Z= (A1,A2) |

Sk=Z |

|

|

|

|

|

|

Y1 |

C [0:31]:=000…0 |

A1=C |

|

Z [0:31]:=000…0 |

C [0:31]:=Z [0:31] |

|

|

|

|

|

|

Y2 |

C [0:31]:=C [0:31] + 1 |

A1=C |

|

Z [0:31]:=A1 [0:31] + 1 |

C [0:31]:=Z [0:31] |

|

|

|

|

|

|

Y3 |

B [33:63]:=B [32:62] |

A1=B |

|

Z [33:63]:=A1 [32:62] |

B [33:63]:=Z [33:63] |

|

|

|

|

|

|

Y4 |

B [1:32]:=B [0:31] + 000…0 |

A1=B |

|

Z [1:32]:=A1 [0:31] + 000…0 |

B [1:32]:=Z [1:32] |

|

|

|

|

|

|

Y5 |

B [1:32]:=B [0:31] + A [0:31] |

A1=B |

A2=A |

Z [1:32]:=A1 [0:31] + A2 [0:31] |

B [1:32]:=Z [1:32] |

|

|

|

|

|

|

Y7 |

ПП [0]:=1 |

A1=ПП |

|

Z [0]:=1 |

ПП [0]:=Z [0] |

|

|

|

|

|

|

Y8 |

B [0:15]:=111…1 |

A1=B |

|

Z [0:15]:=111…1 |

B [0:15]:=Z [0:15] |

|

|

|

|

|

|

Y9 |

B [0:15]:=000…0 |

A1=B |

|

Z [0:15]:=000…0 |

B [0:15]:=Z [0:15] |

|

|

|

|

|

|

Y10 |

A [0]:=1 |

|

A2=A |

Z [0]:=1 |

A [0]:=Z [0] |

|

|

|

|

|

|

Y11 |

A [0]:=0 |

|

A2=A |

Z [0]:=0 |

A [0]:= Z [0] |

|

|

|

|

|

|

Y12 |

A [0:31]:=A [1:31].A [0] |

|

A2=A |

Z [0:31]:=A2 [1:31].A2 [0] |

A [0:31]:= Z [0:31] |

|

|

|

|

|

|

Y13 |

B [0:31]:=B [1:31].B [0] |

A1=B |

|

Z [0:31]:=A1 [1:31].A1 [0] |

B [0:31]:= Z [0:31] |

|

|

|

|

|

|

Управляющие сигналы и микрооперации:

|

Выборка операндов |

Преобразование слов |

Загрузка результата |

||||

|

|

|

|

|

|

|

|

ai |

A1=Si |

bj |

A2=Sj |

m |

Z= m(A1,A2) |

dk |

Sk=Z |

|

|

|

|

|

|

|

|

a1 |

A1=C |

b1 |

A2=A |

1 |

Z [0:31]:=000…0 |

d1 |

C [0:31]:=Z [0:31] |

|

|

|

|

|

|

|

|

a2 |

A1=B |

|

|

2 |

Z [0:31]:=A1 [0:31] + 1 |

d2 |

B [33:63]:=Z[33:63] |

|

|

|

|

|

|

|

|

a3 |

A1=ПП |

|

|

3 |

Z [33:63]:=A1 [32:62] |

d3 |

B [1:32]:=Z [1:32] |

|

|

|

|

|

|

|

|

|

|

|

|

4 |

Z [1:32]:=A1 [0:31] + 000…0 |

d4 |

ПП [0]:=Z [0] |

|

|

|

|

|

|

|

|

|

|

|

|

5 |

Z [1:32]:=A1 [0:31] + A2 [0:31] |

d5 |

B [0:15]:=Z [0:15] |

|

|

|

|

|

|

|

|

|

|

|

|

6 |

Z [0]:=1 |

d6 |

A [0]:=Z [0] |

|

|

|

|

|

|

|

|

|

|

|

|

7 |

Z [0:15]:=111…1 |

d7 |

A [0:31]:= Z [0:31] |

|

|

|

|

|

|

|

|

|

|

|

|

8 |

Z [0:15]:=000…0 |

d8 |

B [0:31]:= Z [0:31] |

|

|

|

|

|

|

|

|

|

|

|

|

9 |

Z [0]:=0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

Z [0:31]:=A2 [1:31].A2 [0] |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

Z [0:31]:=A1 [1:31].A1 [0] |

|

|

|

|

|

|

|

|

|

|

Обобщённый оператор: Z = A3 + A4, где:

000…0; |

1, 8 |

|

A1 |

[0:31]; |

2, 4, 5 |

A1 |

[32:62]; |

3 |

1[0]; |

6 |

|

A3 = |

|

|

111…1; |

7 |

|

0 [0]; |

9 |

|

A2 [1:31].A2 [0]; 10

A1 [1:31].A1 [0]; 11

000…0; |

1, 3, 4, 6, 7, 8, 9, 10, 11 |

A4 = 1 [31]; |

2 |

A2 [0:31]; 5

Кодирование микроопераций наборами управляющих сигналов:

Y1 |

a1 |

- |

1 |

d1 |

|

|

|

|

|

Y2 |

a1 |

- |

2 |

d1 |

|

|

|

|

|

Y3 |

a2 |

- |

3 |

d2 |

|

|

|

|

|

Y4 |

a2 |

- |

4 |

d3 |

|

|

|

|

|

Y5 |

a2 |

b1 |

5 |

d3 |

|

|

|

|

|

Y7 |

a3 |

- |

6 |

d4 |

|

|

|

|

|

Y8 |

a2 |

- |

7 |

d5 |

|

|

|

|

|

Y9 |

a2 |

- |

8 |

d5 |

|

|

|

|

|

Y10 |

- |

b1 |

6 |

d6 |

|

|

|

|

|

Y11 |

- |

b1 |

9 |

d6 |

|

|

|

|

|

Y12 |

- |

b1 |

10 |

d7 |

|

|

|

|

|

Y13 |

a2 |

- |

11 |

d8 |

|

|

|

|

|

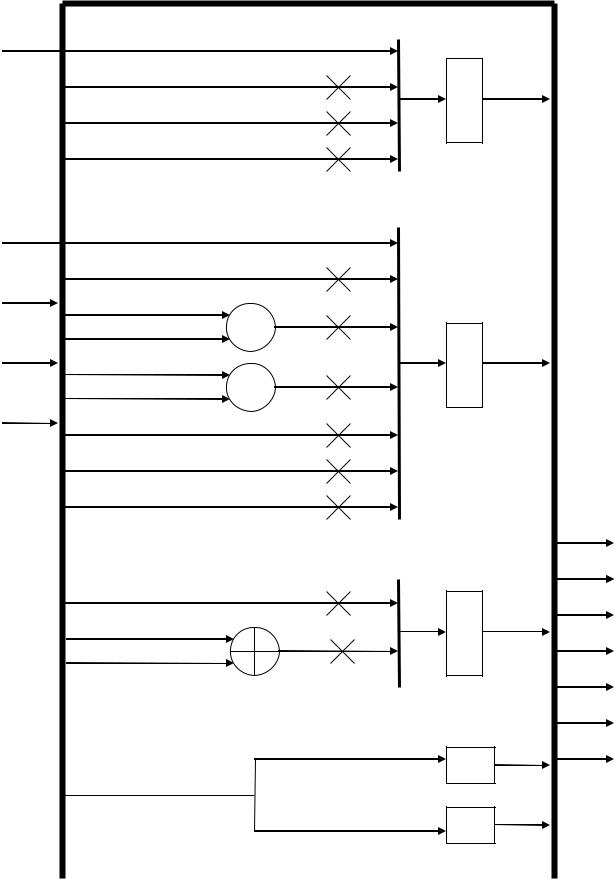

Структурная схема М-автомата:

|

|

|

|

A1 |

A2 |

1ый операнд |

|

|

|

||

|

|

|

|||

d6 [0] |

x |

|

|

b1x |

|

|

|

A |

|

|

|

d7 [0:31] |

|

|

|

||

x |

|

|

|

||

2ой операнд |

|

|

|

||

|

|

|

|||

|

|

|

|||

d2 |

[33:63] x |

|

|

|

|

d3 |

[1:32] |

x |

B |

a2 x |

|

d5 |

[0:15] |

x |

|

|

|

d8 |

[0:31] |

x |

|

|

|

|

|

|

|

|

|

d1 [0:31] x |

C |

a1 |

x |

|

|

|

|

|

|

|

|

d4

x

ПП

|

|

A3 |

|

|

|

|

000…0; |

1, 8 |

|

|

|

|

|

|

|

x |

|

|

|

|

A1 |

[0:31]; |

2, 4, 5 |

|

|

|

|

|

|

x |

|

|

|

|

A1 |

[32:62]; |

3 |

|

|

|

|

|

|

x |

|

|

|

|

A3 |

[0]; |

6 |

|

|

|

|

1 |

|

x |

|

|

|

|

111…1; |

7 |

|

|

|

|

|

|

|

x |

|

|

|

|

A3 |

[0]; |

9 |

|

П |

|

|

0 |

|

x |

|

|

|

|

A2 |

[1:31].A2 [0]; 10 |

|

|

|

|

|

|

|

x |

|

|

|

|

|

|

|

|

|

|

|

A1 |

[1:31].A1 [0]; 11 |

|

|

|

|

|

|

|

|

|

|||

|

|

x |

|

|

|

|

000…0; 1, 3, 4, 6, |

|

|

|

|

||

7, 8, 9, 10, 11 x |

|

|

|

|

||

A4 |

[31]; |

2 |

|

|

|

|

1 |

|

x |

|

|

|

|

A2 |

[0:31]; |

5 |

|

|

|

|

|

|

x |

|

|

|

|

|

|

A4 |

|

|

|

|

|

|

|

|

|

|

|

9 Представление чисел в ЭВМ

Целые числа .Прямой код. Прямой код двоичного числа совпадает по изображению с записью самого

числа. Значение знакового разряда для положительных чисел равно 0, а для отрицательных чисел 1. Обратный код. Обратный код для положительного числа совпадает с прямым кодом. Для отрицательного

числа все цифры числа заменяются на противоположные (1 на 0, 0 на 1), а в знаковый разряд заносится единица.

Дополнительный код. Дополнительный код положительного числа совпадает с прямым кодом. Для

отрицательного числа дополнительный код образуется путем получения обратного кода и добавлением к

младшему |

|

разряду |

|

|

единицы. |

||

В |

любом |

представлении |

старший |

бит |

определяет |

знак |

числа: |

0 |

|

- |

|

положительное |

|

число; |

|

1 - отрицательное число

Пример.

Для числа +1101:

Прямой код |

Обратный код |

|

|

|

|

0,0001101 |

0,0001101 |

|

|

|

Дополнительный код

0,0001101

Для числа -1101:

Прямой код |

Обратный код |

|

|

1,0001101 |

1,1110010 |

|

|

Дополнительный код

1,1110011

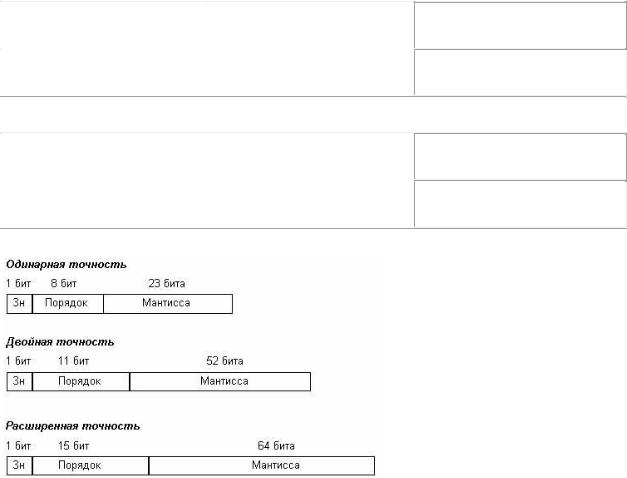

Вещественные числа (числа с плавающей точкой)

Все равные по абсолютному значению положительные и отрицательные числа отличаются только этим битом. В остальном числа с разным знаком полностью одинаковы. Для представления отрицательных чисел здесь не

используется |

|

|

дополнительный |

|

код. |

Поле |

мантиссы |

содержит |

мантиссу |

нормализованного |

числа. |

Одинарная |

|

|

|

|

точность: |

1.(цифры |

|

|

|

|

мантиссы)*2(P-127) |

Двойная |

|

|

|

|

точность: |

1.(цифры |

|

|

|

|

мантиссы)*2(P-1023) |

Расширенная |

|

|

|

|

точность: |

1.(цифры мантиссы)*2(P-16383)

11. Управляющие автоматы с жёсткой логикой

Теория управляющих абстрактных и конечных автоматов – очень обширная наука, описывающая понятие автоматов, их поведение, формализацию, различные модели и пр. Здесь не будут рассматриваться все эти теоретические аспекты, рассмотрим лишь две практических варианта УА с жёсткой логикой.

Название «автомат с жёсткой логикой» проистекает из того, что алгоритм функционирования такого автомата жёстко задан его схемой. Для внесения даже незначительных изменений в алгоритм необходимо полностью (или почти полностью) пересинтезировать всю схему автомата. «Отделаться» какими-то мелкими изменениями возможно далеко не всегда.

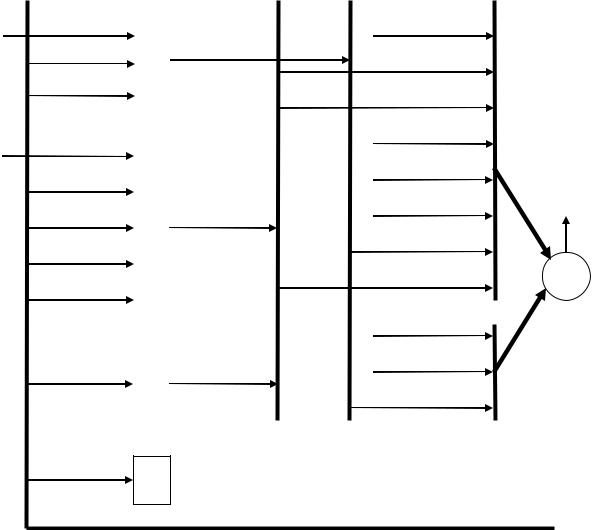

Обобщённая структурная схема УА с жёсткой логикой имеет вид – рис. 2.

Рис. 2. Обобщённая структурная схема УА с жёсткой логикой

На рис. 2: X – множество входных сигналов автомата, Y – множество выходных сигналов, D – сигналы управления памятью, T – сигналы состояния.

УА состоит из 2-х функциональных блоков:

1.КС – комбинационная схема, формирующая выходные сигналы автомата и сигналы управления памятью.

2.Память автомата – просто набор триггеров (регистр). Кол-во триггеров n определяется кол-вом k требуемых состояний автомата. k определяется по-разному для разных автоматов. k равно ближайшему целому (в большую сторону) числу из значений выражения 2n. Т.е. n=]log2k[. Например, если у нас 5 состояний, то мы должны поставить 3 триггера (23=8>5), а если 8, то 4 (24=16>8).

Функционирование УА может задаваться графом переходов либо таблицами истинности. Можно описать его поведение и формулами: Y=ƒ1(X,T), D=ƒ2(X,T).

Очевидно, что при использовании одновходовых триггеров (D и Т) КС получается проще (для каждого триггера формировать надо только один сигнал вместо 2, как для RS или JK триггеров). На практике, если, например, в наличии есть только RS-триггеры, то можно несколько «схитрить», сделав D-триггеры из RS и синтезировать КС в расчёте на D.

Следует также отметить, что всегда следует применять триггеры с синхронизацией. Если использовать триггеры без синхронизации, например, асинхронные RS-триггеры, то полученный автомат будет «перещёлкивать» все свои состояния очень быстро, со скоростью, определяемой скоростью работы элементов, входящих в КС и самих триггеров. Кроме того, на выходе могут появляться какие-то другие, случайные и «незапланированные» комбинации состояний выходов.

Если применяются D-триггеры, то можно использовать обычные регистры хранения вместо раздельных триггеров. Это может существенно упростить конечную схему.

УА с жёсткой логикой бывают 2-х видов – Мили и Мура.