- •Оглавление

- •Вопрос №3

- •Вопрос №4

- •Вопрос №5

- •Вопрос №6 Системы исчисления

- •Вопрос №7

- •Вопрос №8

- •Вопрос №9

- •Вопрос №10

- •Вопрос №11

- •Вопрос №12

- •Вопрос №13

- •Вопрос №14

- •Вопрос №15

- •Вопрос №16

- •Вопрос №17

- •Вопрос №18

- •Вопрос №19

- •Вопрос №20

- •Вопрос 21

- •Вопрос 22

- •Вопрос 23

- •Вопрос №24

- •Вопрос № 25

- •Вопрос № 26

- •Вопрос №27

- •Вопрос №28

- •1. Команда пересылки данных.

- •Вопрос №29

- •Вопрос №30

- •Вопрос №31

- •Вопрос №32

- •Вопрос №33

- •Вопрос №33(Краткая версия)

- •1) Команда вызова процедуры.

- •2) Команда возврата управления.

- •Вопросы №34

- •Вопросы №35

- •Вопрос №36

- •1) Команда организации цикла.

- •2) Команда перехода по обнуленному счетчику.

- •3) Команды организации цикла с условием.

- •Вопрос №37

- •Вопросы №38

- •Вопрос №39

- •Вопрос №40

Вопрос №14

Диапазон значений физических адресов зависит от разрядности шины адреса процессора

Для

i486 и Pentium он находится в пределах от 0 до

-1(4Гбайт)

-1(4Гбайт)

Для

процессоров Pentium II/III/4 этот диапазон

шире — от 0 до

– 1 (64 Гбайт).

– 1 (64 Гбайт).

Механизм управления памятью полностью аппаратный. Процессор аппаратно поддерживает 2 модели использования оперативной памяти.Различают:

сегментированную модель, в которой программе выделяются непрерывные области памяти (сегменты), а сама программа может обращаться только к данным, которые находятся в этих сегментах;

страничную модель можно рассматривать как надстройку над сегментированной моделью. Здесь оперативная память рассматривается как совокупность блоков фиксированного размера (4 Кбайт и более). Основное применение этой модели связано с организацией виртуальной памяти, что позволяет операционной системе привлекать для работы программ пространство памяти намного большее, чем объем физической памяти.

Сегментная модель памяти (I8086/286).

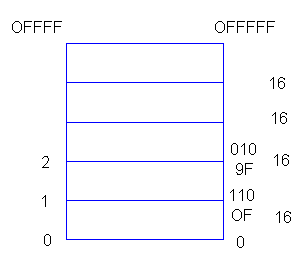

В инструкциях I8086/286 адрес данных ограничен 16-ю разрядами, т.е. значение адреса ограниченоo-offff– 64 кб. Сегментная модель позволяет адресовать 1024 кб с помощью 16-ти разрядных регистров.

Внутри сегмента блок памяти размером 64 кб. Положение сегмента в адресном пространстве 1024 кб задается от 0 до OFFFF. Начала сегментов отстоят друг от друга на 16 байт (параграф).

Сегменты, используемые процессором для адресации памяти, следующие:

Текущий сегмент кода, из которого считывается очередная инструкция по смещению заданного ip.

Текущий сегмент данных для доступа к операндам инструкций по смещению, заданному вне инструкции.

Текущий сегмент стека – для доступа к стеку по смещению, заданному SР или ВР. Текущее значение номера сегмента кода, сегмента данных и сегмента стека хранятся в регистрахCS(CodeSegment),DS(Datasegment),SS(StackSegment),ES(ExtraDataSegment).

Для считывания очередной инструкции используется пары 16разрядных регистров CS,IP, для обращения к стеку –SS,SP/BP, для обращения к данным –DP, смещение.

В сегментированной модели памяти программа никогда не знает, по каким физическим адресам будут размещены ее сегменты. Различают три основные модели сегментированной организации памяти:

1) Сегментированная модель реального режима,

2) Защищенного режима,

3) Сплошная модель памяти защищенного режима.

Под физическим адресом понимается адрес памяти, выдаваемый на шину адреса процессора.

Вопрос №15

Диапазон изменения физического адреса — от 0 до 1 Мбайт.

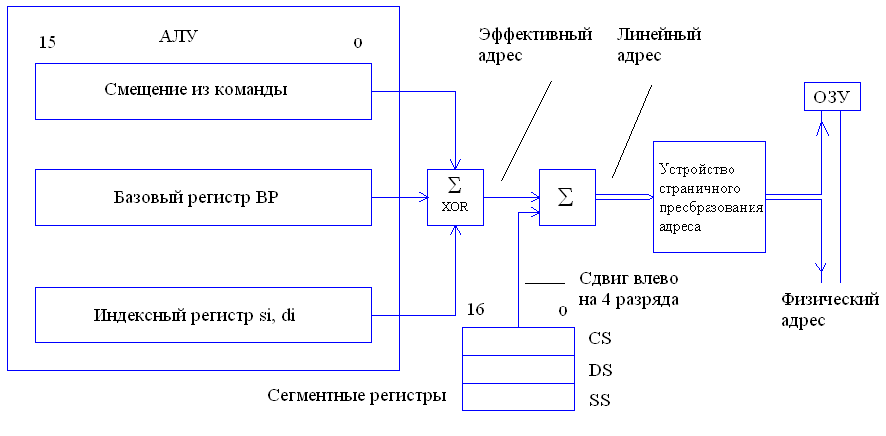

Для обращения к конкретному физическому адресу оперативной памяти необходимо определить адрес начала сегмента (сегментную составляющую) и смещение внутри сегмента.

При обращении к конкретному физическому адресу оперативной памяти необходимо определить адрес начала сегмента и смещение внутри сегмента. В процессоре эти 2 составляющие на аппаратном уровне складываются, в результате получается физический адрес памяти размерностью 20 бит. Это позволяет сделать программное обеспечение перемещаемым, то есть не зависящим от конкретных адресов загрузки в его оперативной памяти.

Сегментная часть извлекается из сегментных регистров, сдвигается на 4 разряда влево и суммируется со смещением. В архитектуре IA32 пока процессор находится в реальном режиме, старшие 12 линий шины адреса не доступны.

Недостатки формирования физического адреса в реальном режиме:

Сегменты бесконтрольно размещаются с любого адреса, кратного 16 и, как правило, программа может обращаться к любым адресам, в том числе реально не существующим.

Сегменты имеют максимальный размер 64 кб.

Сегменты могут перекрываться другими сегментами.