Микропроцессорные устройства на основе мпк серии кр580.

Микропроцессорный комплект серии КР580 содержит набор БИС для построения микропроцессорных устройств относительно невысокого быстродействия, работающих с тактовой частотой до 2,5 МГц.

Все микросхемы, входящие в состав МПК, выполнены по n - МДП – технологии, однако входные и выходные сигналы соответствуют уровням логических схем ТТЛ – технологии.

__________________________________________________________________________

Технология n – МДП предполагает, что в качестве активных элементов в полупроводниковой микросхеме используются полевые транзисторы n-типа со структурой «Металл – диэлектрик – полупроводник».

Транзисторно-транзисторная логика (ТТЛ, TTL) — разновидность цифровых микросхем, построенных на основе биполярных транзисторов и резисторов. Название транзисторно-транзисторный возникло из-за того, что транзисторы используются как для выполнения логических функций (например, И, ИЛИ), так и для усиления выходного сигнала (в отличие от резисторно - транзисторной и диодно - транзисторной логики).

Максимальное напряжение в схемах с ТТЛ может достигать 24В, однако это приводит к большому уровню паразитного сигнала. Достаточно малый уровень паразитного сигнала при сохранении достаточной эффективности достигается при напряжении 5В, поэтому данная цифра и вошла в технический регламент ТТЛ.

___________________________________________________________________________________

Микросхемы МПК КР580 характеризуются следующими параметрами: температурный диапазон – от -10 до +70 градусов; потребляемая мощность - менее 0,7 Вт; напряжение питания +5 В; допустимое отклонение напряжения - +/-5%; нагрузочная способность каждого выхода БИС – один вход элемента ТТЛ; время спада и нарастания входных напряжений на выводах БИС – менее 30 нс.

Из всего комплекта будут рассмотрены:

КР580ВИ53 – программируемый таймер

КР580ВВ51 – программируемый последовательный интерфейс;

КР580ВВ55 – программируемый параллельный интерфейс.

Программируемый таймер кр580ви53 (отечественный аналог Intel i8253)

Управление периферийными устройствами часто требует от микропроцессорной системы точного задания временных интервалов между управляющими сигналами. Сделать это программно зачастую невозможно из-за сложного временного расписания обмена данными внутри микропроцессорной системы. К тому же вставка тактов ожидания в программу тормозит работу процессора. Такие задачи поручают программируемым таймерам (ПТ). С помощью ПТ процессор может формировать временные интервалы произвольной длительности, производить синхронизацию внешних устройств, организовывать счетчики событий, вести счет текущего времени и т. д.

Программируемый таймер КР580ВИ53 содержит три независимых счетчика с максимальной частотой счета 2 МГц. Каждый из трех счетчиков может быть запрограммирован на различные режимы работы и счета (двоичный или двоично-десятичный).

Структура таймера

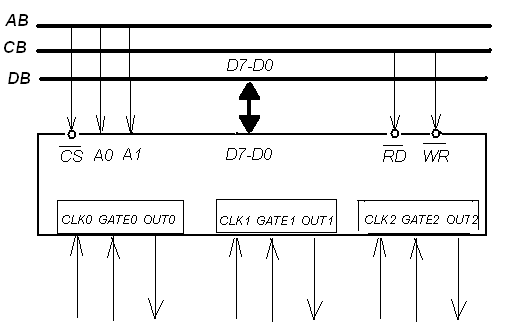

Структурная схема программируемого таймера представлена на рис. 1. Блок «Управление вводом-выводом» управляет обменом данными между тремя счетчиками и шиной данных. Регистр управления позволяет программно настроить любой из трех счетчиков на желаемый режим работы.

D0…D7 |

Двунаправленная трехстабильная шина данных, предназначенная для приема управляющих слов и данных из микропроцессора и передачи данных в виде показаний счетчиков из микросхемы в микропроцессор. D0 – младший разряд. |

/WR |

Write. Запись. Входной сигнал, разрешающий микросхеме принимать информацию из микропроцессора. По низкому уровню на этом входе микропроцессор записывает данные в ПТ. |

/RD |

Read. Чтение. Входной сигнал, разрешающий передачу информации из микросхемы в канал данных микропроцессора в виде показаний счетчиков. Низкий уровень на этом входе информирует ПТ, что процессор хочет прочитать состояние счетчика. |

/CS |

Chip Select. Выбор микросхемы. Низкий уровень инициирует обмен между процессором и ПТ. Не оказывает воздействия на работу счетчиков таймера |

A0, A1 |

Адресные входы. Позволяют выбрать один из трех счетчиков для операции чтения/записи состояния счетчиков |

CLK0...CLK2 |

Тактовые входы каждого из трех счетчиков |

GATE0…GATE2 |

Входы разрешения счетчиков. Уровень "1" - разрешение счета |

OUT0…OUT2 |

Выходы счетчиков |

Стандартно подключение таймера к шинам микропроцессора показано на рисунке.

Входы А0, А1, которые отвечают за выбор адресуемого регистра, соединяются с соответствующими линиями шины адреса. Вход CS подключается к одной из линий шины адреса, когда применяется линейный выбор, либо к выходу дешифратора адреса. Сигнал записи WR загружает байт с шины данных в адресуемый регистр, а сигнал считывания RD передает содержимое адресуемого регистра на шину данных.

Все операции, определяемые сигналами CS, WR, RD и адресными входами A0, A1 сведены в таблице.

-

CS

RD

WR

A1

A0

Операции

0

1

0

0

0

Загрузка счетчика канала 0 с шины данных

0

1

0

0

1

Загрузка счетчика канала 1 с шины данных

0

1

0

1

0

Загрузка счетчика канала 2 с шины данных

0

1

0

1

1

Загрузка регистра режима с шины данных

0

0

1

0

0

Считывание показаний счетчика канала 0

на шину данных

0

0

1

0

1

Считывание показаний счетчика канала 1

на шину данных

0

0

1

1

0

Считывание показаний счетчика канала 2

на шину данных

0

0

1

1

1

Запрет. Канал данных в высокоимпедансном состоянии.

0

1

1

*

*

Запрет. Канал данных в высокоимпедансном состоянии.

1

*

*

*

*

Запрет. Канал данных в высокоимпедансном состоянии.

Основными компонентами организации программируемого таймера являются: буфер канала данных, схема управления вводом-выводом и три независимых канала.

Каждый канал состоит из вычитающего 16-битного счетчика, регистра режима, схемы управления каналом и выходного каскада. В любой из счетчиков допускается загрузка начального значения счетчика с системной шины, а текущее содержимое можно считать, не прекращая счета. Собственно входные сигналы CLK0-CLK2 счетчиков подаются через схемы с внешними управляющими входами GATE0-GATE2. С каждым счетчиком ассоциируется выходной сигнал OUT. Остальные компоненты схемы предназначены для установки режима и интерфейса с системной шиной.

Выходной каскад выполняет функции время задающего элемента и обеспечивает согласование выхода данной микросхемы с одним входом микросхем ТТЛ.

Счетчик 16-битный вычитающий, предназначен для выполнения счетных операций в соответствии с запрограммированным режимом. Счетчик выполняет операции в двоичном или двоично-десятичном коде над однобайтными или двухбайтными числами. Возможная скорость счета от 0 до 2 МГц. Максимальная величина счета при выполнении счетных операций в двоичном коде – 216=65536, в двоично-десятичном коде – 104. Счетчики трех каналов независимы друг от друга и могут иметь различные режимы работы и различные типы счета. Разряд счетчика состоит из трех каскадов – буферного регистра, регистра хранения и счетного триггера.

Буферный регистр принимает данные, поступающие из центрального процессора, и передает их в регистр хранения или принимает информацию из счетного триггера и передает ее в центральный процессор.

В регистр хранения информация поступает из буферного регистра (обратная операция невозможна). Содержимое регистра хранения изменяется только при перезагрузке счетчика новой величиной или при перепрограммировании режима работы канала путем записи управляющего слова в регистр режима. В последнем случае регистр хранения устанавливается в нулевое состояние.

Счетный триггер принимает информацию из регистра хранения. Так как счетчик вычитающий, то число, загруженное в счетный триггер, будет декрементироваться. Загрузка во все ряды счетных триггеров информации в виде нулей позволяет получить максимально возможную величину счета. Информация из счетного триггера передается в буферный регистр и при необходимости может быть прочитана.

Регистр режима канала состоит из шести разрядов (D5-D0) и предназначен для приема и хранения кода управляющего слова. Код управляющего слова задает режим работы канала, определяет тип счета и последовательность загрузки данных в счетчик. Информацию в регистр режима можно только записывать. Прочитать содержимое этого регистра невозможно.

Для функционирования таймера процессор должен загрузить управляющие слова, определяющие режим работы каждого счетчика, и необходимые начальные значения.

Формат управляющего слова для выбора режима работы.

Таймер КР580ВИ53 может работать как:

Режим прерывания счета или программируемая задержка

Ждущий мультивибратор

Импульсный генератор частоты (делитель частоты)

Генератор меандра (генератор прямоугольных импульсов со скважностью 2)

Режим одиночного программно-формируемого строба

Режим одиночного аппаратно-формируемого строба

Режим 0 - выдача сигнала прерывания по конечному числу или программируемая задержка. В этом режиме на выходе выбранного канала таймера формируется сигнал низкого уровня с программируемой задержкой. Начало работы инициируется высоким уровнем на входе GATE. Когда содержимое счетчика достигает нуля, на выходе OUT устанавливается высокий уровень, используемый для прерывания микропроцессора и сохраняющийся до нового задания режима. Когда в процессе работы осуществляется повторная загрузка счетчика загрузка первого байта прекращает счет, а загрузка второго байта начинает новый цикл. Если в процессе счета устанавливается низкий уровень GATE=0, содержимое счетчика сохраняется и после восстановления высокого уровня счет продолжается от запомненного значения. Отметим, что N=0 соответствует значению 216 в двоичном коде.

Рис. Режим программируемой задержки

Режим 1

- ждущий мультивибратор с

программно-устанавливаемой длительностью

сигнала. Если в счетчик загружено

начальное значение N,

то после первого сигнала CLK,

следующего за установлением высокого

уровня GATE,

на выходе OUT

формируется отрицательный импульс

продолжительностью N

периодов

![]() сигналов

CLK.

Загрузка нового значения N

при низком уровне OUT

не влияет на длительность импульса до

последующего запуска. Мультивибратор

является «перезапускаемым», т.е.

отрицательный импульс на выходе OUT

сохраняет продолжительность

сигналов

CLK.

Загрузка нового значения N

при низком уровне OUT

не влияет на длительность импульса до

последующего запуска. Мультивибратор

является «перезапускаемым», т.е.

отрицательный импульс на выходе OUT

сохраняет продолжительность

![]() от любого фронта на входе GATE.

от любого фронта на входе GATE.

Рис. Режим программируемого мультивибратора

Режим 2 – генератор программируемой частоты, или счетчик с коэффициентом деления N. После установки высокого уровня GATE на выходе OUT формируется периодический сигнал, продолжительность высокого уровня которого составляет (N-1)τ, а низкого τ. Когда производится перезагрузка счетчика, текущий период не изменяется, а следующий будет соответствовать новому значению N. Вход GATE используется для аппаратной синхронизации, так как низкий уровень GATE устанавливает высокий уровень OUT, а с последующим переходом GATE к высокому уровню счет инициируется с начального значения. При задании режима 2 высокий уровень OUT сохраняется до загрузки N, чем обеспечивается программная синхронизация генератора.

Рис. Режим программируемого генератора тактовых импульсов

Режим 3

- генератор прямоугольных сигналов со

скважностью 2 (меандр). Данный режим

напоминает предыдущий, так как период

выходного сигнала равен

![]() ,

но выход OUT

имеет высокий уровень в течение

,

но выход OUT

имеет высокий уровень в течение

![]() ,

если N

четное, или

,

если N

четное, или

![]() ,

если N

нечетное. При перезагрузке счетчика

новое значение N

учитывается в следующем периоде выходного

сигнала.

,

если N

нечетное. При перезагрузке счетчика

новое значение N

учитывается в следующем периоде выходного

сигнала.

Рис. Генератор прямоугольных импульсов (меандр)

Режим 4 - программно-управляемый строб. После задания режима на выходе OUT формируется высокий уровень и инициирование счета осуществляется загрузкой в счетчик значения N. При достижении счетчиком нуля на выходе OUT формируется отрицательный импульс длительностью τ. Если производится перезагрузка счетчика между выходными импульсами, текущий период не изменяется, а следующий соответствует новому значению N. Низкий уровень GATE запрещает работу счетчика; если при действии его происходит перезагрузка счетчика, счет начинается с нового значения N.

Режим 5 – аппаратно-формируемый строб. Начало счета инициируется фронтом сигнала GATE. При достижении нулевого состояния счетчика на выходе OUT формируется отрицательный импульс длительностью τ. Как и мультивибратор, в режиме 1, счетчик является перезапускаемым, то есть любой фронт сигнала GATE инициирует полный цикл работы.

Существуют задачи, в которых процессор должен периодически считывать содержимое счетчиков каналов. Примером такой задачи может служить счет событий. Во время работы счетчика его текущее содержимое может быть передано в буферный и прочитано двумя способами: при помощи обычной операции чтения или с помощью специальной схемы "чтения на лету", активизируемой вводом специального управляющего слова.

При первом способе для обеспечения стабилизации показаний счета работа счетчика должна быть приостановлена подачей на управляющий вход уровня "0" (в режимах 0, 2, 3, 4) или с помощью внешней логической схемы, приостанавливающей подачу импульсов на тактовый вход канала.

Второй способ позволяет процессору считывать содержимое счетчика, не прерывая процесса счета. Для этого в ПТ по адресу A0=1, A1=1 осуществляется запись управляющего слово, определяющего в соответствии с табл. 3 режим чтения на лету (D4=0, D5=0). Разряды D6 и D7 определяют номер канала, состояние разрядов D0...D3 произвольно. По этой команде в буферном регистре защелкивается текущая величина счета, далее следует обычная операция чтения содержимого счетчика. Отметим, что данная команда не изменяет содержимого регистра режима. При этом способе чтения нельзя предварительно по каждому каналу производить запись управляющих слов и лишь затем производить чтение счетчиков каналов.

Особенность построения внутренней схемы таймера требует, чтобы операция чтения содержимого счетчика была выполнена до конца, т. е. если запрограммирована загрузка двух байтов, то нельзя, прочитав один младший байт, перегружать счетчик новой величиной.