- •Стандартні розміри системних плат

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Контрольні запитання

- •Практична робота №4 Опис найпростіших логічних схем на мові vhdl. Тріггери. Регістри. Лічильники.

- •Теоретичні відомості.

- •Variable список змінних;

- •Завдання до практичної роботи

- •Практична робота №5 Опис найпростіших логічних схем на мові vhdl. Мультиплексори, суматори, помножувачі.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №6 Побудова схем з пам'яттю. Ramb, srl, rom, fifo.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №7 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №8 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

- •Теоретичні відомості.

- •Завдання до практичної роботи

Завдання до практичної роботи

Завдання: ознайомитися з теоретичними відомостями про опис регістрів, тригерів та лічильників на мові VHDL, скласти опис схеми з памяттю згідно свого варіанту.

Варіант |

Розрядність |

Розмір стеку |

Початкова адреса |

Кінцева адреса |

1 |

5 |

15 |

10 |

60 |

2 |

6 |

13 |

30 |

55 |

3 |

7 |

11 |

15 |

50 |

4 |

8 |

9 |

10 |

60 |

5 |

9 |

16 |

30 |

55 |

6 |

10 |

14 |

15 |

50 |

7 |

11 |

12 |

10 |

60 |

8 |

12 |

10 |

15 |

55 |

9 |

5 |

18 |

30 |

50 |

10 |

6 |

20 |

10 |

55 |

11 |

7 |

15 |

10 |

70 |

12 |

8 |

13 |

30 |

75 |

13 |

9 |

11 |

15 |

70 |

14 |

10 |

9 |

10 |

70 |

15 |

11 |

16 |

30 |

75 |

16 |

12 |

14 |

15 |

70 |

17 |

5 |

12 |

10 |

70 |

18 |

6 |

10 |

15 |

75 |

19 |

7 |

18 |

30 |

70 |

20 |

8 |

20 |

10 |

75 |

21 |

9 |

15 |

10 |

50 |

22 |

10 |

13 |

30 |

55 |

23 |

11 |

11 |

15 |

50 |

24 |

12 |

9 |

10 |

50 |

25 |

5 |

16 |

30 |

55 |

Практична робота №7 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

Мета: ознайомитися з особливостями проектування на мові VHDL конвеєрних ОП.

Теоретичні відомості.

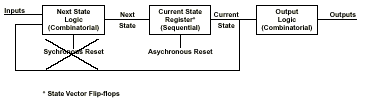

У ряді випадків автоматна модель (опис) пристрої дозволяють отримати швидку і ефективну реалізацію послідовних пристроїв. Зазвичай обчислювальний пристрій (ОП) складається з трьох основних частин (рис. 7.1):

Рис. 7.1 Струткура ОП

Регістр поточного стану (Sequential Current State Register). Цей регістр являє собою набір тактовані D-тригерів синхронізуються одним синхросигналом і використовується для зберігання коду поточного стану автомата. Очевидно, що для автомата з n станами потрібно log 2 (n) тригерів.

Логіка переходів (Combinational Next State Logic). Як відомо, кінцевий автомат може перебувати в кожен конкретний момент часу тільки в одному стані. Кожен тактовий імпульс викликає перехід пристрою з одного стану в інший. Правила переходу і визначаються комбінаційної схемою, званої логікою переходів. Наступне стан визначається як функція поточного стану і вхідного впливу.

Логіка формування виходу (Combinational Output Logic). Вихід цифрового автомата зазвичай визначається як функція поточного стану та вихідної установки (у випадку автомата Мілі). Формування вихідного сигналу пристрою визначається за допомогою логіки формування виходу.

Для забезпечення стабільної і безвідмовної роботи використовується скидання прострою в початковий стан. Таким чином завжди забезпечується ініціалізація пристрою в заздалегідь предорпеделенном сотоянии при першому тактовом імпульсі. У разі, якщо скид не передбачений, неможливо передбачити з якого початкового стану почне функціонування, що може привести до збоїв в роботі всієї системи. Особливо ця ситуація актуальна при включенні живлення системи. Тому ми настійно рекоммендуем використовувати схеми скидання і початкової установки при проектуванні пристроїв на ПЛІС. Зазвичай застосовують асинхронні схеми скидання, через те, що не потрібно використовувати дешифратор невикористовуваних (надлишкових) станів, що спрощує логіку переходів.

З іншого боку, через те, що ПЛІС, виконані по архітектурі FPGA мають достатнє число регістрів (тригерів), використання автоматних моделей дозволяє отримати досить швидкодіючу і, в той же час наочну реалізацію при пріємлімих витратах ресурсів.

Приклад інтегратора на VHDL

library ieee;

use ieee.std_logic_1164. all;

entity mealy is

port (clock, reset: in std_logic;

data_out: out std_logic;

data_in: in std_logic_vector (1 downto 0));

end mealy;

architecture behave of mealy is

type state_values is (st0, st1, st2, st3, st4);

signal pres_state, next_state: state_values;

begin

- FSM register

statereg: process (clock, reset)

begin

if (reset = '0 ') then

pres_state <= st0;

elsif (clock'event and clock = '1 ') then

pres_state <= next_state;

end i f;

end process statereg;

- FSM combinational block

fsm: process (pres_state, data_in)

begin

case pres_state is

when st0 =>

case data_in is

when "00" => next_state <= st0;

when "01" => next_state <= st4;

when "10" => next_state <= st1;

when "11" => next_state <= st2;

when others => next_state <= (others <= 'x');

end case;

when st1 =>

case data_in is

when "00" => next_state <= st0;

when "10" => next_state <= st2;

when others => next_state <= st1;

end case;

when st2 =>

case data_in is

when "00" => next_state <= st1;

when "01" => next_state <= st1;

when "10" => next_state <= st3;

when "11" => next_state <= st3;

when others => next_state <= (others <= 'x');

end case;

when st3 =>

case data_in is

when "01" => next_state <= st4;

when "11" => next_state <= st4;

when others => next_state <= st3;

end cas e;

when st4 =>

case data_in is

when "11" => next_state <= st4;

when others => next_state <= st0;

end cas e;

when others => next_state <= st0;

end cas e;

end process fsm;

outputs: process (pres_state, data_in)

begin

case pres_state is

when st0 =>

case data_in is

when "00" => data_out <= '0 ';

when others => data_out <= '1 ';

end cas e;

when st1 => data_out <= '0 ';

when st2 =>

case data_in is

when "00" => data_out <= '0 ';

when "01" => data_out <= '0 ';

when others => data_out <= '1 ';

end cas e;

when st3 => data_out <= '1 ';

when st4 =>

case data_in is

when "10" => data_out <= '1 ';

when "11" => data_out <= '1 ';

when others => data_out <= '0 ';

end cas e;

when others => data_out <= '0 ';

end cas e;

end process outputs;

end behave;

Приклад декодера переходів має вигляд.

library ieee;

use ieee.std_logic_1164. al l;

entity moore is

port (clock, reset: in std_logic;

data_out: out std_logic;

data_in: in std_logic_vector (1 downto 0));

end moore;

architecture behave of moore is

type state_values is (st0, st1, st2, st3, st4);

signal pres_state, next_state: state_values;

begin

- FSM register

statereg: process (clock, reset)

begin

if (reset = '0 ') then

pres_state <= st0;

elsif (clock = '1 'and clock'event) then

pres_state <= next_state;

end i f;

end process statereg;

- FSM combinational block

fsm: process (pres_state, data_in)

begin

case pres_state is

when st0 =>

case data_in is

when "00" => next_state <= st0;

when "01" => next_state <= st4;

when "10" => next_state <= st1;

when "11" => next_state <= st2;

when others => next_state <= (others <= 'x');

end cas e;

when st1 =>

case data_in is

when "00" => next_state <= st0;

when "10" => next_state <= st2;

when others => next_state <= st1;

end cas e;

when st2 =>

case data_in is

when "00" => next_state <= st1;

when "01" => next_state <= st1;

when "10" => next_state <= st3;

when "11" => next_state <= st3;

when others => next_state <= (others <= 'x');

end cas e;

when st3 =>

case data_in is

when "01" => next_state <= st4;

when "11" => next_state <= st4;

when others => next_state <= st3;

end cas e;

when st4 =>

case data_in is

when "11" => next_state <= st4;

when others => next_state <= st0;

end cas e;

when others => next_state <= st0;

end cas e;

end process fsm;

outputs: process (pres_state)

begin

case pres_state is

when st0 => data_out <= '1 ';

when st1 => data_out <= '0 ';

when st2 => data_out <= '1 ';

when st3 => data_out <= '0 ';

when st4 => data_out <= '1 ';

when others => data_out <= '0 ';

end cas e;

end process outputs;

end behave;