- •Стандартні розміри системних плат

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Контрольні запитання

- •Практична робота №4 Опис найпростіших логічних схем на мові vhdl. Тріггери. Регістри. Лічильники.

- •Теоретичні відомості.

- •Variable список змінних;

- •Завдання до практичної роботи

- •Практична робота №5 Опис найпростіших логічних схем на мові vhdl. Мультиплексори, суматори, помножувачі.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №6 Побудова схем з пам'яттю. Ramb, srl, rom, fifo.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №7 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

- •Теоретичні відомості.

- •Завдання до практичної роботи

- •Практична робота №8 Проектування конвеєрних оп на vhdl. Цифрові фільтри. Декодери. Інтегратори.

- •Теоретичні відомості.

- •Завдання до практичної роботи

Завдання до практичної роботи

Завдання: ознайомитися з теоретичними відомостями про опис регістрів, тригерів та лічильників на мові VHDL, скласти опис пристрою згідно свого варіанту.

Варіант |

Тип пристрою |

Розрядність |

Виконувані дії |

1 |

мультиплексор |

12/1 |

- |

2 |

шифратор |

7/2 |

- |

3 |

дешифратор |

4/9 |

- |

4 |

суматор |

5/1 |

- |

5 |

- |

3/1 |

додавання з логічним зсувом вправо |

6 |

- |

4/1 |

додавання з арифметичним зсувом вправо |

7 |

- |

5/1 |

додавання з циклічним зсувом вправо |

8 |

- |

6/1 |

віднімання з логічним зсувом вправо |

9 |

- |

2/1 |

віднімання з арифметичним зсувом вправо |

10 |

- |

3/1 |

віднімання з циклічним зсувом вправо |

11 |

- |

2/1 |

додавання та порівняння |

12 |

- |

4/1 |

віднімання та порівняння |

13 |

- |

2/1 |

множення та порівняння |

14 |

- |

3/1 |

ділення та порівняння |

15 |

мультиплексор |

8/1 |

- |

16 |

шифратор |

12/5 |

- |

17 |

дешифратор |

3/10 |

- |

18 |

суматор |

15/1 |

- |

19 |

мультиплексор |

8/1 |

- |

20 |

шифратор |

16/6 |

- |

21 |

дешифратор |

6/16 |

- |

22 |

суматор |

20/1 |

- |

23 |

мультиплексор |

12/1 |

- |

24 |

шифратор |

5/2 |

- |

25 |

дешифратор |

2/5 |

- |

Практична робота №6 Побудова схем з пам'яттю. Ramb, srl, rom, fifo.

Мета роботи: набуття практичних навичок в реалізації та тестуванні схем з пам’яттю на мові VHDL.

Теоретичні відомості.

Моделювання пам'яті з довільним доступом. (RAM - Random Access Memory)

Пам'ять з довільним доступом дозволяє здійснювати читання/запис даних по будь-якою адресою в довільному порядку. Пам'ять з довільним доступом містить:

шину адреси.

шину даних.

керуючі лінії:

вибір мікросхеми.

дозвіл запису.

вхід тактування.

Використання блокової пам'яті.

Блокова пам'ять створена як додаток до розподіленої пам'яті, яка має невелику ємність.

Загальний обсяг блокової пам'яті залежить від числа блоків Block Select RAM на кристалі.

Кожен блок пам'яті - це повністю синхронна двопортова RAM з незалежним управлінням для кожного порту. Розмірність шини даних для обох портів може бути налаштована незалежно. Кожен порт пам'яті може бути використаний як окрема однопортова пам'ять.

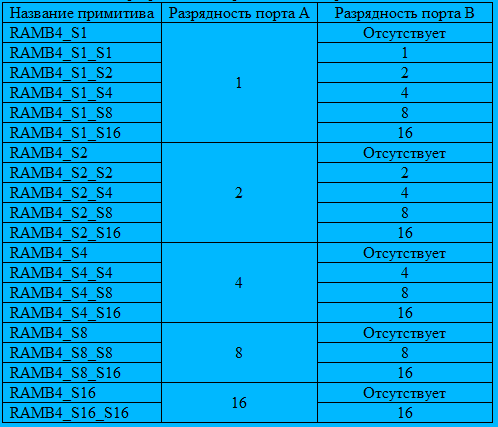

У стандартних бібліотеках існує набір примітивів, що дозволяють звертатися до блокової пам'яті рис. 6.1 та рис 6.2.

Рис. 6.1 Графічне позначення інтерфейсу примітиву двухпортової блокової пам'яті.

Рис. 6.2 Графічне позначення інтерфейсу примітиву однопортової блокової пам'яті.

На графічних схемах позначені наступні входи-виходи:

CLK - тактування пам'яті

EN - дозвіл роботи пам'яті. Якщо на цьому вході встановлено неактивний сигнал, то запис в пам'ять не може виконуватися, а на вихідних лініях даних зберігається попередній стан.

WE - дозвіл запису.

RST - скидання.

ADDR - шина адреси.

DI - вхідна шина даних. Призначена для запису даних в пам'ять.

DO - вихідна шина даних. Призначена для читання даних з пам'яті.

Існують різні примітиви пам'яті, застосування яких залежить від необхідної розрядності шин адреси і даних. Основною характеристикою примітиву пам'яті є розрядність порту пам'яті, яка фактично є розрядністю шини даних примітиву. Нижче в таблиці 6.1 наведені можливі значення розрядності і відповідні їм визначення шини адреси і шини даних:

Таблиця 6.1 - Можливі значення розрядності.

Розрядність |

Кількість комірок |

Шина адреси |

Шина даних |

1 |

4096 |

ADDR <11:0> |

DATA <0> |

2 |

2048 |

ADDR <10:0> |

DATA <1:0> |

4 |

1024 |

ADDR <9:0> |

DATA <3:0> |

8 |

512 |

ADDR <8:0> |

DATA <7:0> |

16 |

256 |

ADDR <7:0> |

DATA <15:0> |

В залежності від розрядності портів можна визначити назву необхідного примітиву пам'яті (рис. 6.3):

Рис. 6.3 Різновиди примітивів пам'яті

Найпростішим випадком використання примітиву блокової пам'яті, є відображення його портів на порти користувацького модуля. Використання блокової пам'яті в такому варіанті включає в себе наступні кроки:

підключення бібліотеки, в якій знаходяться примітиви блокової пам'яті:

library unisim;

Опис компоненту використовуваного примітиву блокової пам'яті:

component ramb4_s8

port (

DI: in std_logic_vector (7 downto 0);

EN: in std_ulogic;

WE: in std_ulogic;

RST: in std_ulogic;

CLK: in std_ulogic;

ADDR: in std_logic_vector (8 downto 0);

DO: out std_logic_vector (7 downto 0));

end component;

Опис користувальницького модуля, який використовує блокову пам'ять

entity ram is

port

(address: in std_logic_vector (2 downto 0);

data: inout std_logic_vector (7 downto 0): = "ZZZZZZZZ";

cs, we, clk: in std_logic);

end;

Відображення портів на компонент блокової пам'яті. Слід звернути увагу, що не використовувані розряди шини адреси і / або даних повинні бути відображені на константні значення. В іншому випадку відбудеться помилка компіляції.

U_RAMD: ramb4_s8

port map

(EN => cs,

WE => we,

ADDR (8 downto 3) => "000000",

ADDR (2 downto 0) => address,

DO => data_out,

DI => data_in,

RST => '0 ',

CLK => clk);