- •Содержание:

- •1 Задания и пояснения к элик 01.Ин том 1

- •1 Задания и пояснения к элик 01.Ин том 1

- •1.1 Индикаторы и клавиатура (к заданию 2.1)

- •1.1.1 Семисегментный индикатор

- •1.1.2 Клавиатура

- •1.1.3 Калькулятор

- •1.2 Счетчик команд (к заданию 2.2)

- •1.3 Генератор тактовых импульсов (к заданию 2.3)

- •1.4 Память двоичных кодов (к заданию 2.4)

- •1.4.1 Считывание информации с rg1

- •1.4.2 Запись информации в ram

- •1.5 Мультиплексор (к заданию 2.5)

1.3 Генератор тактовых импульсов (к заданию 2.3)

На НП генератор тактовых импульсов (ГТИ) представляет собой круговой переключатель частоты и индикатор работы.

Рис. 15. Генератор тактовых импульсов на НП.

Входные гнезда установки “0” (R) PC и ГТИ объединены. Поэтому, если выход переключателя SA2 подан на вход R, то, передвинув движок SA2 вниз (логический “0) мы одновременно разрешаем работу PC и ГТИ. Входы ГТИ подтянуты к “1”.

Кнопку SA4 можно использовать для запуска ГТИ (вход “Пуск”). Для дополнительного контроля сигналов с ГТИ можно использовать звуковой сигнализатор (ЗС). Тональностью сигнала управляет любой вход: 1, 2, 4, 8.

Входы ЗС подтянуты к “1”. При “1111” ЗС “молчит”.

Для остановки ГТИ используют входы ОСТ 1 и ОСТ 2.

Рис. 16. Схема ГТИ.

В схеме ГТИ делитель частоты (ДЧ) представлен упрощенно. Реальное исполнение ДЧ представлено на рис. 17.

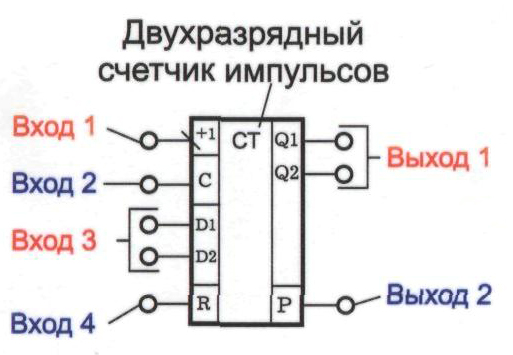

Рис. 17. Двухразрядный счетчик импульсов.

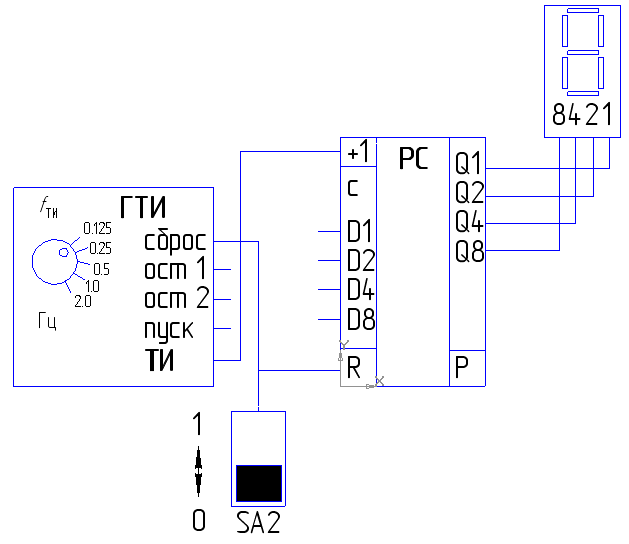

Чтобы наглядно увидеть и понять работу генератора тактовых импульсов, соберем схему циклического счетчика команд (рис.18).

Рис.18 Схема циклического счетчика команд с подключенным генератором тактовых импульсов.

На схеме видно, что на вход «сброс» ГТИ и вход «R» PC подан на выход переключателя SA2. Это сделано для того, чтобы управлять работой ГТИ и PC, при переключении движка SA2 вниз (логический “0”) мы разрешаем работу ГТИ и PC, т.к. по умолчанию на всех входах “1”. С выхода ГТИ «ТИ» на вход PC «+1» идут импульсы. По этим импульсам счетчик будет считать. Текущее значение счетчика выводится на семисегментный индикатор. Частоту импульсов можно задать при помощи движка переключателя ƒти (0,125; 0,25; 0,5; 1,0; 2,0 Гц)

Такой счетчик при ГТИ будет считать от “0” до “9” в цикле.

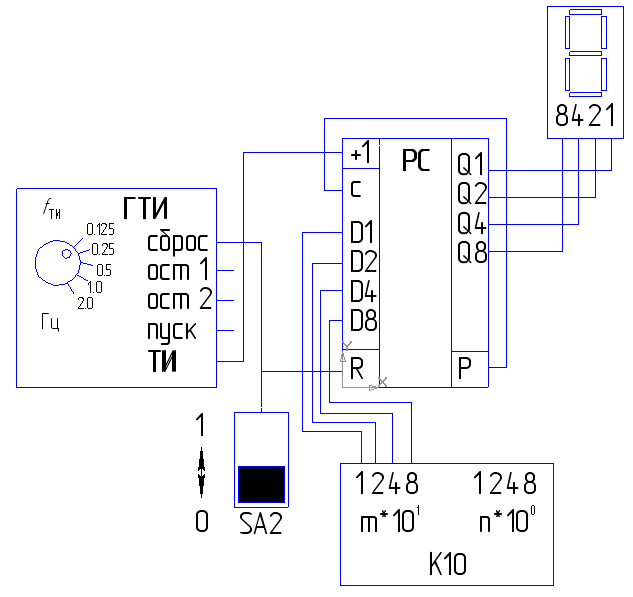

Можно модернизировать данную схему так, чтобы счетчик считал например с 4 до 9 в цикле (или начиная с любого другого числа от 0 до 8). Для этого будем использовать входы PC «D1», «D2», «D4» и «D8» для ввода значения начала счета. Выход «P» - переполнение счетчика, мы будем подавать на вход «С» счетчика для занесения начального числа отсчета. Пример такого счетчика показан на рис.19.

В этом примере начальное число устанавливается клавиатурой К10.

Рис.19. Схема циклического счетчика команд с подключенным генератором тактовых импульсов и с вводом начального значения отсчета (с предустановкой).

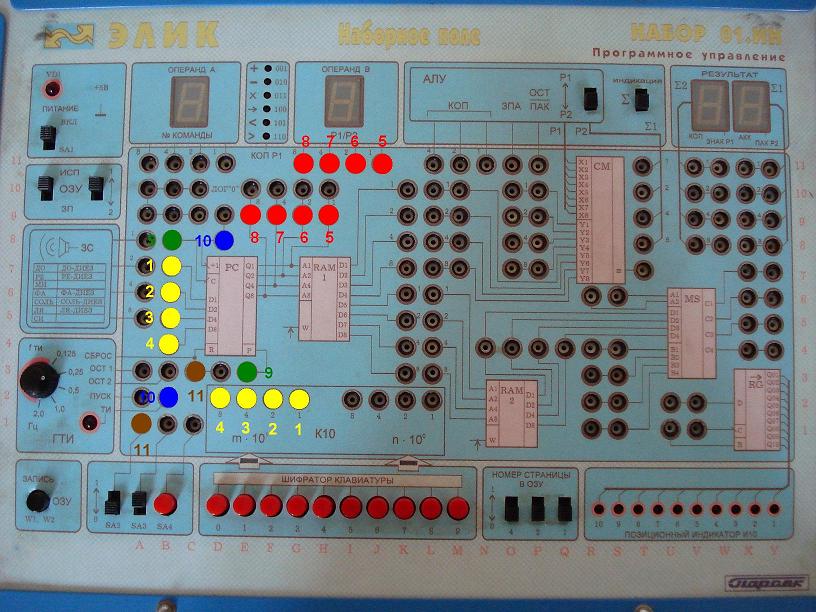

Рис. 20. Схема подключения контактов циклического счетчика команд с подключенным генератором тактовых импульсов и с вводом начального значения отсчета.

● (1-4) – Подключение клавиатуры к счетчику команд.

● (5-8) – Вывод на индикатор.

● 9 – Подключение выхода «P» - переполнение счетчика к входу «С».

● 10 – Подключение PC к ГТИ “ТИ”.

● 11 – Подключение «сброс» ГТИ и «R» PC к переключателю SA2.

1.4 Память двоичных кодов (к заданию 2.4)

В компьютерной технике для хранения информации используют:

оперативные запоминающие устройства (ОЗУ), которые содержат наборы регистров на RS-триггерах – ячейки памяти; эти ОЗУ (RAM) формируются на основе сверхбольших интегральных схем (СБИС);

долговременные запоминающие устройства (ДЗУ) на специальных носителях информации.

ОЗУ более быстродействующие, чем ДЗУ, но имеют меньший информационный объем.

ДЗУ хранят информацию, как правило, на оптических и магнитных дисках, постоянно работающих в составе устройства или сменных накопителях.

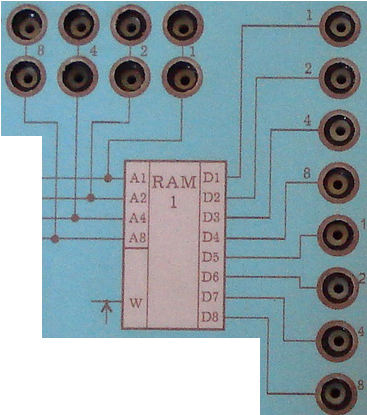

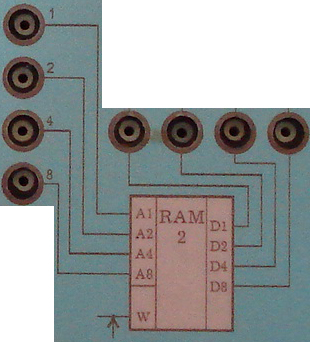

На НП имеются две такие СБИС. Они представлены на рис. 21 и рис. 22.

Рис. 21. RAM1 на НП. Рис. 22. RAM2 на НП.

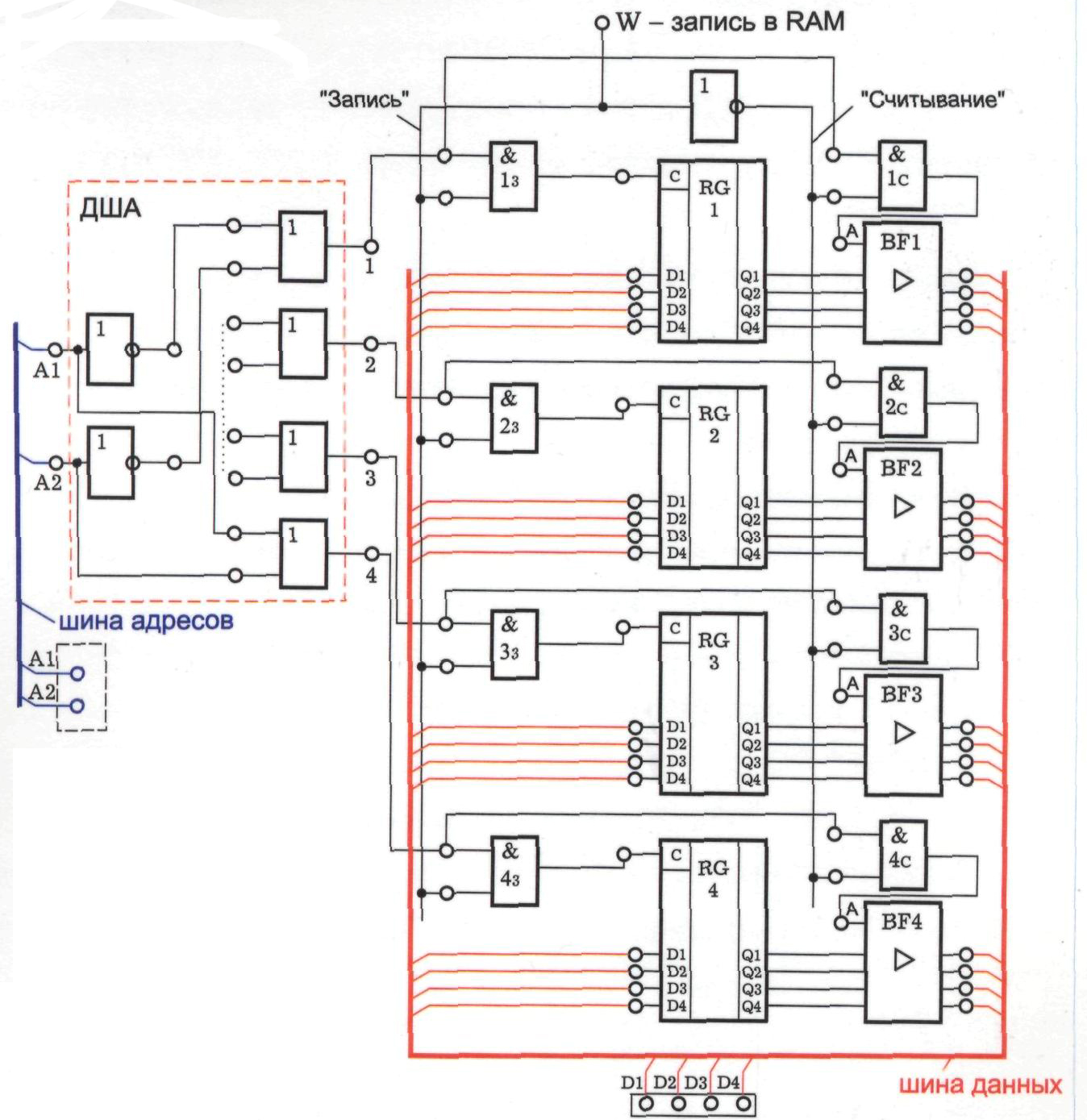

На рис. 21 ячейки памяти – регистры RG1..RG4, содержащие по четыре D триггера. Номер регистра – адрес ячейки памяти. Обеспечивают работу регистров элементы “И”, ”ИЛИ”, ”НЕ” и логические ключи BF (буфер).

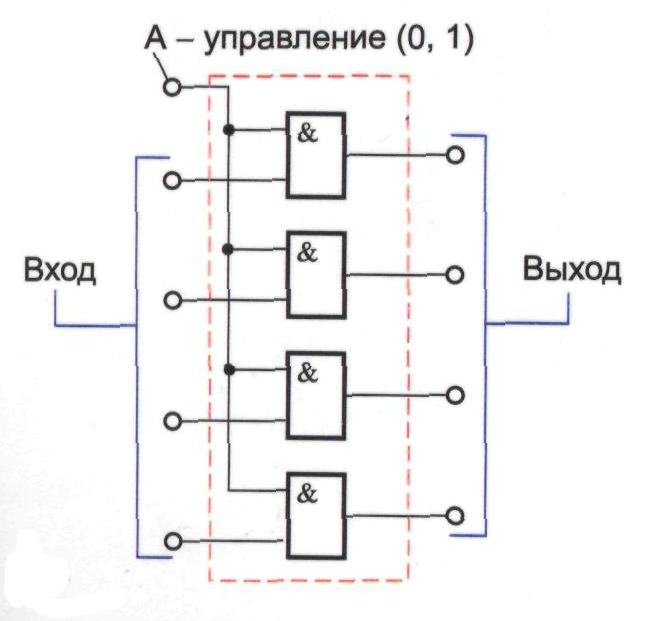

Схема буфера для четырехразрядной шины – на рис. 24. Сигнал А = 1 разрешает прохождение входных логических переменных на выход. При А = 0 на выходе буфера – нули.

Чтобы считать информацию с RG нужно подключить Q-выходы этого RG к шине данных RAM (D1..D4).

Выбор нужной ячейки памяти производится указанием ее адреса. Два двоичных разряда (А1, А2) позволяют задать один из четырех адресов.

Рис. 23. Структура СБИС.

00 – RG1, 01 – RG2, 10 – RG3, 11 – RG4

Преобразователь кода в сигнал управления на линии, соответствующей номеру ячейки – дешифратор адреса (ДША).

Рис. 24. Схема буфера для четырехразрядной шины.