- •Формализация требований к системе

- •Разработка аппаратных и программных средств

- •Локальная шина

- •Системная шина

- •3. 36 Разрядный

- •В ячейку памяти с наибольшим адресом

- •Программатор

- •3. Быстродействием ппзу

- •Режим 0 – режим основного ввода-вывода

- •Режим 2 – двунаправленный стробируемый ввод-вывод

- •Режим 0 – режим основного ввода-вывода

- •Для обмена 8-разрядными данными между внешним устройством и памятью

- •Для каскадного объединения контроллеров

- •Для обмена словами блоками по 128 Кбайт.

- •Для каскадного объединения контроллеров

- •Для обмена 8-разрядными данными между внешним устройством и памятью

- •1. Локальная шина;

- •2.Шина памяти;

- •4.Системная шина;

- •3. Нет верного ответа

- •2. Раздельный

- •3. 16 Мбайт

- •3. От 2 до 8 и даже более.

- •3. Оба ответа верны

- •3. Процессор переходит в режим обработки немаскируемого прерывания nmi

- •3. Оба ответа верны

- •2. Для регенерации динамической памяти компьютера

- •3. Информация нигде не используется

1. Локальная шина;

2.Шина памяти;

3.Шина Х;

4.Системная шина;

5.Внешняя шина.

Через какой регистр осуществляется управление УАПП:

1.SYSREG;

2.REGSYSTEM;

3TREG;

4.SCON;

5.CONFR.

Для чего в стандарте RS-232Cиспользуется бит четности:

1.Узнать, четный ли стандарт;

2.Не используется;

3.Контроль качества передачи;

4.Команда обрыва соединения;

5.Определения соединения типа модем.

Максимальный адресуемый объем памяти для шины ATBus:

гигабайт;

2. 128 килобайт;

лобайт;

мегабайт;

5. 64 мегабайта.

Количество IRQ у системной платы PCAT:

1. 3;

2. 7;

3. 15;

4. 16;

5. 8.

247. Микросхема i82385 – это:

Сопроцессор;

Микропроцессор;

Контроллер кэш-памяти;

Графический чип;

Контроллер клавиатуры.

248. Микросхема ALS245A – это:

1.Часы реального времени;

Шинный формирователь;

Контроллер прерываний;

Стабилизирующий элемент;

Контроллер прямого доступа.

249. Батарейка на системной плате используется для:

Питания сопроцессора;

Дополнительного питания внешних накопителей;

Стабилизации напряжения;

Питания памяти CMOS;

Резервный источник питания процессора.

250. Какой активный сигнал выставляется 16-разрядным внешним устройством для сообщения задатчику шины о том, что устройство, к которому он обращается, имеет 16-ти разрядную организацию и ему следует выполнить 16-ти разрядный цикл доступа:

1. I/O CH16

2. -DACK

3. RESET DRV

251. Если этот сигнал не активен, то может быть выполнен только 8-ми разрядный цикл доступа к внешнему устройству:

1. BALE

2. I/O CH16

3. –DACK

252. Сигнал системного сброса. Вырабатывается процессором для начальной установки всех ресурсов на шине при включении или сбое питания, а также при нажатии на кнопку RESET компьютера:

1.AEN

2.-DACK

3. RESET DRV

253. Минимальное время длительности сигнала RESET DRV:

1. 1 мс

2. 0,1 мс

3. 0,01 мс

254. Максимальная длина печатного проводника от контакта разъема шины до вывода микросхемы:

1.не более 100 мм

2. не более 65 мм

3. не более 500 мм

255. Максимальная емкость относительно земли по каждому контакту разъема:

1. не более 30 пФ

2. не более 50 пФ

3. не более 20 пФ

256. Выработкой этого сигнала центральный процессор начинает цикл Доступа к Ресурсу, сообщающего всем ресурсам об истинности адреса на линиях SA<19...0>, а также для фиксации ресурсами адреса по линиям LA<23...17>:

1. BALE

2. AEN

3. –DACK

257. Наиболее короткий цикл из всех возможных на шине:

1. Цикл Захвата Шины

2. Цикл доступа с 0 тактов ожидания

3. Цикл Регенерации

258. По истечении какого времени с последнего цикла контроллер регенерации пытается захватить шину:

1. 10 мкс

2. 5 мкс

3. 15 мкс

259. После разрешения какого сигнала контроллером ПДП запускаются циклы ПДП:

1. -DACK

2. AEN

3. I/O CH16

260. Программируются один раз непосредственно их потребителем:

1. прожигаемые ПЗУ

2. масочные ПЗУ

3. репрограммируемые ПЗУ

261. ПЗУ, информация в которые записывается непосредственно в процессе их изготовления:

1. прожигаемые ПЗУ

2. масочные ПЗУ

3. репрограммируемые ПЗУ

262. При программировании прожигаемых ПЗУ через транзистор достаточно пропустить импульс тока в:

1.10 .. 20 мА

2. 5 .. 10 мА

3. 20 .. 30 мА

263. Какие ячейки ПЗУ обладают возможностью электрического стирания информации:

1. ячейки на МНОП – транзисторах

2. ячейки на транзисторах с плавающим затвором

3. А и Б

264. Вид адресации, применяемый в ПЗУ:

1. двумерная

2. одномерная

3. трехмерная

265. Информация в ПЗУ представляется в виде наличия или отсутствия соединения между:

1. шинами адреса и данных

2. шинами адреса и системной шиной

3. А и Б

266. Чем ПЗУ принципиально отличаются от ОЗУ:

1. в ОЗУ информация не исчезает при снятии напряжения питания

2. в ПЗУ информация исчезает при снятии напряжения питания

3. в ПЗУ информация не исчезает при снятии напряжения питания

267. Самый дешевый вид ПЗУ:

1. прожигаемые ПЗУ

2. масочные ПЗУ

3. репрограммируемые ПЗУ

268. Недостатки пережигаемых ПЗУ:

1. пережженный контакт со временем может восстановиться, искажая записанную информацию

2. под действием солнечного излучение возможно стирание информации

3. А и Б

269. Недостатки масочных ПЗУ:

1. пережженный контакт со временем может восстановиться, искажая записанную информацию

2. под действием солнечного излучение возможно стирание информации

3. А и Б

270. Какой конфигурации локальной сети не существует:

Звезда

Кольцо

Круг

Шина

271. В процедуре записи в контроллер сети на ASSEMBLER в регистр СХ помещается…

Длина пакета

Начало источника

Начало приемника

Конец источника

В процедуре записи в контроллер сети на ASSEMBLER в регистр DI помещается…

Длина пакета

Начало источника

Начало приемника

Конец источника

В процедуре записи в контроллер сети на ASSEMBLER в регистр SI помещается…

1. Длина пакета

2. Начало источника

Начало приемника

Конец источника.

274.В рассмотренном примере сигнал задержки это?

1.STR

2.-SMEMW

3.I/O СН RDY

4.-SMEMR

275. Максимальное значение счета для ПТ при работе в двоичном коде:

216

28

232

24

276. Сколько каналов имеет ПТ?

2

4

3

277. Выдача сигнала прерывания по конечному числу соответствует режиму работы:

1. 0 – прерывание терминального счета

1 – ждущий мультивибратор

2 – генератор тактовых импульсов

278. В режиме 5 сигнал GATE может выполнять следующие функции:

1.Запрещает счет

Начинает счет

Устанавливает уровень «1» сигнала на выходе

279.Во время работы счетчика его текущее содержимое может быть передано в буферный регистр и прочитано:

при помощи обычной операции чтения

с помощью специальной операции "чтения на лету"

не может быть прочитано никаким образом

280.Ревизия – это:

1.одна из модификаций ядра, крайне незначительно отличающаяся от предыдущей

2.частота процессора

3.технология виртуализации

281.Сигналы DACK0…DACK7

сигналы запроса ПДП.

сигналы предоставления ПДП.

сигнал выбора устройства, запросившего ПДП

сигналы запроса радиальных прерываний

282. По каким сигналам производится пересылка данных из памяти в устройство ввода-вывода?

1)

![]()

2)

![]()

3)

![]()

4)

![]()

283. Cигнал –MASTER

меняет направление передачи адреса

устанавливает в 1 состояния

внутренний сигнал интерфейсной платы

подтверждение захвата и управления системной шиной (сигнал передается ЦП)

импульс подтверждения приема байта (запрос на прием следующего)

284.Сигнал -MEMW

1. строб чтения данных в памяти(вырабатывается только при обращении к адресам, не превышающим FFFFF)

2.строб чтения данных из памяти(при обращении ко всем адресам памяти)

3.строб чтения данных в памяти(при обращении ко всем адресам памяти)

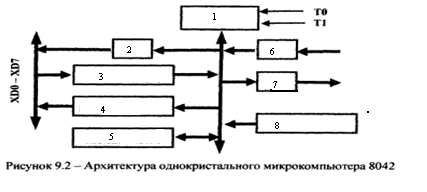

285.На рисунке 9.2 «Архитектура подсистемы клавиатуры» блок 2…

1.регистр состояния

2. входной порт

3.выходной порт

4.входной буфер

5.выходной буфер

6.RAM (внутреннее ОЗУ – 128 Б)

7.ROM (внутреннее ПЗУ)

285.На рисунке 9.2 «Архитектура подсистемы клавиатуры» блок 1…

1.выходной буфер

2.регистр состояния

3.выходной порт

4.входной буфер

5.RAM (внутреннее ОЗУ – 128 Б)

6.микропроцессор

7.ROM (внутреннее ПЗУ)

286.На рисунке 9.2 «Архитектура подсистемы клавиатуры» блок 5…

1.ROM (внутреннее ПЗУ)

2.RAM (внутреннее ОЗУ – 128 Б)

3.выходной буфер

4.входной порт

5.выходной порт

6.регистр состояния

7.входной буфер

287.На рисунке 9.2 «Архитектура подсистемы клавиатуры» блок 8…

1.входной буфер

2.ROM (внутреннее ПЗУ)

3.регистр состояния

4.выходной порт

5.входной буфер

6.RAM (внутреннее ОЗУ – 128 Б)

7.входной порт

288.На рисунке 9.2 «Архитектура подсистемы клавиатуры» блок 3…

1.регистр состояния

2.ROM (внутреннее ПЗУ)

3.RAM (внутреннее ОЗУ – 128 Б)

4.входной порт

5.выходной буфер

6.входной буфер

7.выходной порт

289.На рисунке 9.2 «Архитектура подсистемы клавиатуры» блок 7…

1.выходной порт

2.регистр состояния

3.выходной буфер

4.ROM (внутреннее ПЗУ)

5.входной порт

6.RAM (внутреннее ОЗУ – 128 Б)

7.входной порт

290.На рисунке 9.2 «Архитектура подсистемы клавиатуры» блок 4…

1.ROM (внутреннее ПЗУ)

2.входной буфер

3.выходной порт

4.RAM (внутреннее ОЗУ – 128Б)

5.регистр состояния

6.выходной буфер

7.входной порт

291.На рисунке 9.2 «Архитектура подсистемы клавиатуры» блок 6…

1.регистр состояния

2.ROM (внутреннее ПЗУ)

3.входной порт

4.RAM (внутреннее ОЗУ – 128 Б)

5.выходной порт

6.выходной буфер

7.входной буфер

292. На рисунке 9.2 «Архитектура подсистемы клавиатуры» Т0…

линия чтения сигнала

линия чтения данных из клавиатуры в последовательном коде

линия чтения сигнала синхронизации

293. На рисунке 9.2 «Архитектура подсистемы клавиатуры» Т1…

вход тестирования последовательных данных из клавиатуры

линия чтения данных из клавиатуры в последовательном коде

линия чтения сигнала синхронизации

294.В структурной схеме RTC и CMOS памяти блок 1…

1) делитель на 2

2) выходной генератор

3) генератор

4) управление делителем

295.В структурной схеме RTC и CMOS памяти блок 2…

1) делитель на 2

2) выходной генератор

3) генератор

4) интерфейс шины

296. В структурной схеме RTC и CMOS памяти блок 8…

1) делитель на 2

2) выходной генератор

3) генератор

4) интерфейс шины

297. В структурной схеме RTC и CMOS памяти блок 7…

1) делитель на 2

2) выходной генератор

3) формирователь выходных сигналов

4) часы, будильник, календарь

298. В структурной схеме RTC и CMOS памяти блок 5…

1) селектор периода прерываний и выходных сигналов

2) выходной генератор

3) формирователь выходных сигналов

4) часы, будильник, календарь

299. В структурной схеме RTC и CMOS памяти блок 4…

1) селектор периода прерываний и выходных сигналов

2) выходной генератор

3) управление делителем

4) часы, будильник, календарь

300. В структурной схеме RTC и CMOS памяти блок 3…

1) селектор периода прерываний и выходных сигналов

2) выходной генератор

3) управление делителем

4) часы, будильник, календарь

301. В структурной схеме RTC и CMOS памяти блок 9…

1) селектор периода прерываний и выходных сигналов

2) часы, календарь

3) управление делителем

4) часы, будильник, календарь

302. В структурной схеме RTC и CMOS памяти блок 11…

1) селектор периода прерываний и выходных сигналов

2) часы, календарь

3) управление делителем

4) регистры A, B, C, D

303. В структурной схеме RTC и CMOS памяти блок 12…

1) селектор периода прерываний и выходных сигналов

2) часы, календарь

3) часы, будильник, календарь

4) регистры A, B, C, D

304. В структурной схеме RTC и CMOS памяти блок 13…

1) CMOS пользователя

2) часы, календарь

3) часы, будильник, календарь

4) регистры A, B, C, D

305. На рисунке соединению логических элементов МС14069 соответствует схема…

только 1

только 2

3 и 1

2 и 1

только 3

все соответствуют

306. Режим процессора, обработки немаскируемого прерывания?

1.NMI

2.SBHE

3.SYSCLK

4.СН RDY

5.IOR

307. Буфер данных в цикле чтения должен выдавать данные на магистраль не более чем за ?

1.91 нс

2.110 нс

3.70 нс

4.16 нс

5.8 нс

308. При циклах программного обмена с памятью используются те же самые сигналы, только вместо строба чтения -IOR применяются стробы чтения ?

1.-MEMR

2.-SMEMR,

3.-SYSCLK

4.-СН RDY

5.-IOR

309. Для определения байтового или словного формата данных применяется сигнал ?

1.-SMEMW

2.-МЕМ CS16

3.-SYSCLK

4.-СН RDY

5.-IOR

310. Цикл регенерации включает в себя выставление сигнала………., сигналов кода адреса SA0...$А7 и строба чтения из памяти -MEMR. В случае необходимости может использоваться сигнал I/О СН RDY, обеспечивающий асинхронный обмен.

1.-SYSCLK

2.-REFRESH

3.-СН RDY

4.-IOR

5.-SMEMW

311.Системная шина разработана для…

1. IBM PC AT

2. IBM PC XT

3. все ответы верны

312. К 62-контактному разъему прежней магистрали был добавлен…

1. 36-контактный новый разъем

2. 64-контактный новый разъем.

3. 16-контактный новый разъем.

313.Магистраль ISA относится к…

1. немультиплексированным

2.мультиплексированным