- •«Цифровые системы коммутации»

- •Характеристика эатс, используемых на телефонных сетях рк

- •Глава 1

- •1.1. Классификация систем передачи и методов коммутации

- •1.2. Аналоговый, дискретный, цифровой сигналы

- •1.3. Импульсно-кодовая модуляция

- •1.4. Разделение и объединение цифровых сигналов

- •1.5. Плезиохронные цифровые системы передачи

- •Глава 2

- •2.1. Координаты коммутации

- •2.2. Ступень временной коммутации

- •2.3. Ступень пространственной коммутации

- •2.4. Ступень пространственно-временной коммутации

- •2. Использование мультиплексоров и демультиплексоров

- •2.5. Кольцевые соединители

- •Глава 3

- •3.1. Принципы построения цифровых коммутационных полей

- •2. Классификация цкп

- •3.2. Классификация цифровых кп

- •3.3. Цифровые кп первого класса

- •3.4. Цифровые кп второго класса

- •3. Цифровое поле mux-t- ssss-t-dmvx.

- •3.5. Цифровые кп третьего класса

- •3.6. Цифровые кп четвертого класса

- •3.7. Кольцевые цифровые кп

- •3.8. Особенности функционирования и сравнительные характеристики цифровых кп

- •Глава 4

- •4.1. Понятие стыка цифровых атс

- •4.2. Аналоговый абонентский стык

- •4.3. Цифровой абонентский стык

- •4.4. Абонентский стык isdn

- •4.5. Сетевые стыки цифровых атс

- •Глава 5

- •5.1. Принципы построения и функционирования концентраторов

- •5.2. Особенности использования концентраторов

- •Глава 6

- •6. Современные цифровые атс

- •6.1 Цифровая электронная атс фирмы “Huiawey Technologies” - c&c08

- •6.1.1 Общая характеристика

- •6.1.2 Функциональные узлы и компоненты ам/см

- •6.1.3 Структура аппаратных средств c&c08

- •6.1.4 Структура программного обеспечения станции c&c08

- •6.1.5 Конфигурация системы c&c08

- •6.1.6 Конфигурация системы с модулями spm и sm

- •6.1.7 Интерфейсы isdn

- •6.1.8 Обеспечение надежности станции c&c08

- •6.2. Коммутационная система Alcatel 1000 s12

- •Построение коммутационной системы s12

- •Системный Адрес.

- •6.2. Коммутационная система dts3100

- •Большие возможности

- •Структура мультипроцессора

- •Параллельная операционная система

- •Язык программирования chill/sdl

- •Система управления базой данных

- •Структуры системы

- •Общая структура системы

- •Физическая структура

- •6.3. Коммутационная система ахе-10

- •6.4. Коммутационная система si-2000

- •Цифровые атс малой и средней емкости

- •6.6 Цифровая коммутационная система drx-4

- •Характеристика управляющих модулей

- •Цифровая сельская атс м-200

- •Характеристики надёжности атс м-200

- •6.6. Цифровые учрежденческие атс

- •Общая архитектура сети ngn

- •1.1. Общая архитектура

- •1.2. Трехуровневая модель ngn

- •1.2.1. Транспортный уровень

- •1.2.2. Уровень управления коммутацией и обслуживанием вызова

- •1.2.3. Уровень услуг и управления услугами

- •Функциональная структура

- •2.1. Классификация оборудования

- •2.2. Построение транспортных пакетных сетей

- •12. Аналоговая сигнализация 1vf-slmdo

- •13. Аналоговая сигнализация 1vf-slmmo

- •14. Аналоговая сигнализация 1vf-zsld

- •15. Аналоговая сигнализация 1vf-zsldi

- •16. Аналоговая сигнализация 1vf-mgm

- •17. Аналоговая сигнализация mruslm

- •18. Аналоговая сигнализация dsud

- •19. Аналоговая сигнализация esud

- •31. Цифровая сигнализация d-mgm

- •32. Цифровая сигнализация dund

- •33. Цифровая сигнализация eund

- •34. Цифровая сигнализация r2

- •«Цифровые системы коммутации»

- •480043, Г. Алматы, ул. Рыскулбекова, 28

2. Использование мультиплексоров и демультиплексоров

Примером такого подхода в построении 5/Г-ступени является БИС, разработанная итальянскими специалистами для цифровой системы PROTEL UT и получившая название интегрального коммутационного элемента (ECI).

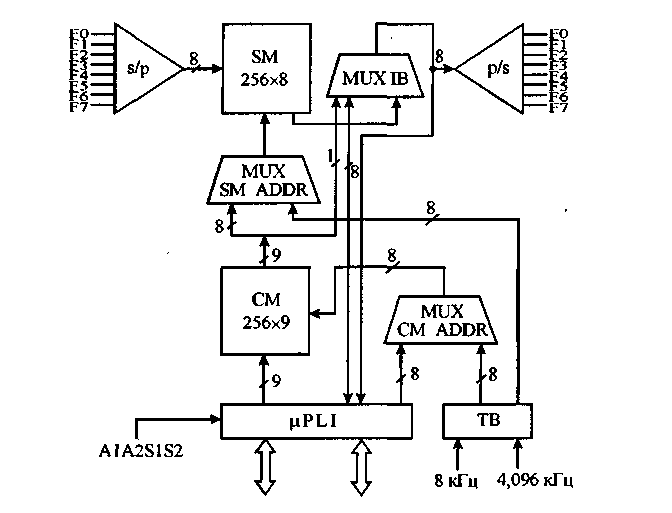

ECI является S/Т-ступенью с параметрами S/T: (8/32)х(8/32). Микросхема ЕС1 может прямо подключаться к шине 8-битового процессора и является для него стандартным периферийным устройством. На рис. 2.20 показана ее структурная схема.

В схеме ECI можно выделить следующие функциональные блоки: синхронизирующее устройство (ТВ); преобразователи последовательного кода ИКМ кодового слова в параллельный и наоборот (s/p и p/s); речевое ЗУ (SM); управляющее ЗУ (СМ); логический интерфейс микропроцессора; мультиплексоры (мультиплексор адреса управляющей памяти - MUX SM ADDR, мультиплексор внутренней ИКМ шины - MUX IB, мультиплексор адреса речевой памяти - MUX CM ADDR).

Синхронизирующее устройство ТВ генерирует и формирует все необходимые синхронизирующие сигналы, используя два внешних сигнала - 4 кГц и 4,096 МГц. В частности, устройство задает два счетчика (входной и выходной) для преобразователей s/p и p/s. Кроме того, из синхросигнала 4 кГц схема ТВ задает три счетчика: CTl, CT2 и СТЗ.

Рис. 2.20. Структурная схема ECI

Первый счетчик (СТ1) формирует отсчет длительности одного канального интервала (примерно 4 мкс). Второй и третий счетчики (СТ2 и СТЗ) работают синхронно со счетчиком СТ1 и вырабатывают последовательные канальные адреса для чтения из управляющего ЗУ и записи в речевое ЗУ соответственно.

Речевое ЗУ организовано в виде 8 полей по 32 строки и 8 столбцов. Каждое поле соответствует номеру бита в кодовом слове, каждая строка — номеру канального интервала в структуре цикла ИКМ-30, а каждый столбец - номеру входящей ИКМ линии. Рабочий цикл ЗУ (около 4 мкс) - разделен на два подинтервала по 2 мкс каждый.

Первый подинтервал содержит восемь циклов длительностью 250 не каждый. В первом цикле в речевое ЗУ записываются по соответствующим адресам 8 бит из каждой линии ИКМ-30. Остальные циклы используются для связи с логическим интерфейсом микропроцессора и приема адреса считывания из управляющего ЗУ. Во втором подинтервале осуществляется считывание 8 бит кодовых слов согласно адресам, полученным из управляющего ЗУ.

Управляющее ЗУ имеет 9 полей по 32 строки и 8 столбцов. Каждое поле соответствует номеру канального интервала в структуре цикла ИКМ-30 (одно поле для проверочных бит). Адреса записаны в управляющем ЗУ так же, как и в речевом.

Рабочий цикл управляющего ЗУ организован аналогично рабочему циклу речевого ЗУ. Во время первого подинтервала ЗУ связано с микропроцессором для получения управляющих сигналов. Во втором подинтервале по сигналам счетчиков СТ1 и СТ2 восемь раз производится считывание адресов для управления речевым ЗУ, которые состоят из адресов считывания в речевом ЗУ ((1...8)-й биты) и одного проверочного бита для управления работой внутренней ИКМ линии.

Логический интерфейс микропроцессора обеспечивает связь ECI с микропроцессором THnaZ-80, из которого приходят сигналы для записи и считывания информации в ECI.

Входы А1, S1, A2, S2 (рис. 2.20) позволяют включить в единую коммутационную схему несколько ECI. Например, для получения емкости ступени 1024x1024 канальных интервалов необходимо объединить восемь ECI.

Следует отметить, что в последнее время несколько фирм объявили о создании специализированных БИС для ступеней коммутации, что объясняется возможностью построения коммутационного поля с меньшими значениями величины блокировок, чем при реализации на интегральных схемах (ИС) общего пользования, а также повышением надежности благодаря реализации оборудования коммутационного поля с помощью меньшего числа элементов и их взаимных связей, и дальнейшим снижением стоимости оборудования коммутационного поля, обусловленным большими объемами выпуска специализированных БИС ограниченного числа типов.

Использование для построения S/T-ступени кольцевых соединителей основано на несколько иных принципах, поэтому такие решения рассмотрим отдельно.