МИКРОАРХИТЕКТУРНЫЙ УРОВЕНЬ 2

ТРАКТ ДАННЫХ 2

РЕГИСТРЫ ТРАКТА ДАННЫХ 2

УСТРОЙСТВО УПРАВЛЕНИЯ (МИКРОПРОГРАММНОЕ) 3

РЕАЛИЗАЦИЯ УСЛОВНЫХ ПЕРЕХОДОВ 4

АРХИТЕКТУРЫ УСТРОЙСТВ УПРАВЛЕНИЯ (ПРОЦЕССОРОВ) 5

МЕТОДЫ ПОВЫШЕНИЯ ПРОИЗВОДИТЕЛЬНОСТИ 6

ОБЗОР 6

ПАРАЛЛЕЛЬНАЯ ОБРАБОТКА ДАННЫХ 6

КОНВЕЙЕРИЗАЦИЯ 7

ИЗМЕНЕНИЕ ПОСЛЕДОВАТЕЛЬНОСТИ ВЫПОЛНЕНИЯ КОМАНД И ПОДМЕНА РЕГИСТРОВ 7

ПРОБЛЕМА ПЕРЕХОДОВ 8

ПРОГНОЗИРОВАНИЕ ПЕРЕХОДОВ 8

УСЛОВНОЕ ИСПОЛНЕНИЕ 8

АРХИТЕКТУРА КОМАНД 9

ОБЗОР УРОВНЯ АРХИТЕКТУРЫ КОМАНД 9

МЕТОДЫ АДРЕСАЦИИ 9

СПОСОБЫ АДРЕСАЦИИ 9

СТЕКОВАЯ АДРЕСАЦИЯ 9

ТИПЫ КОМАНД 10

ТИПЫ ДАННЫХ 10

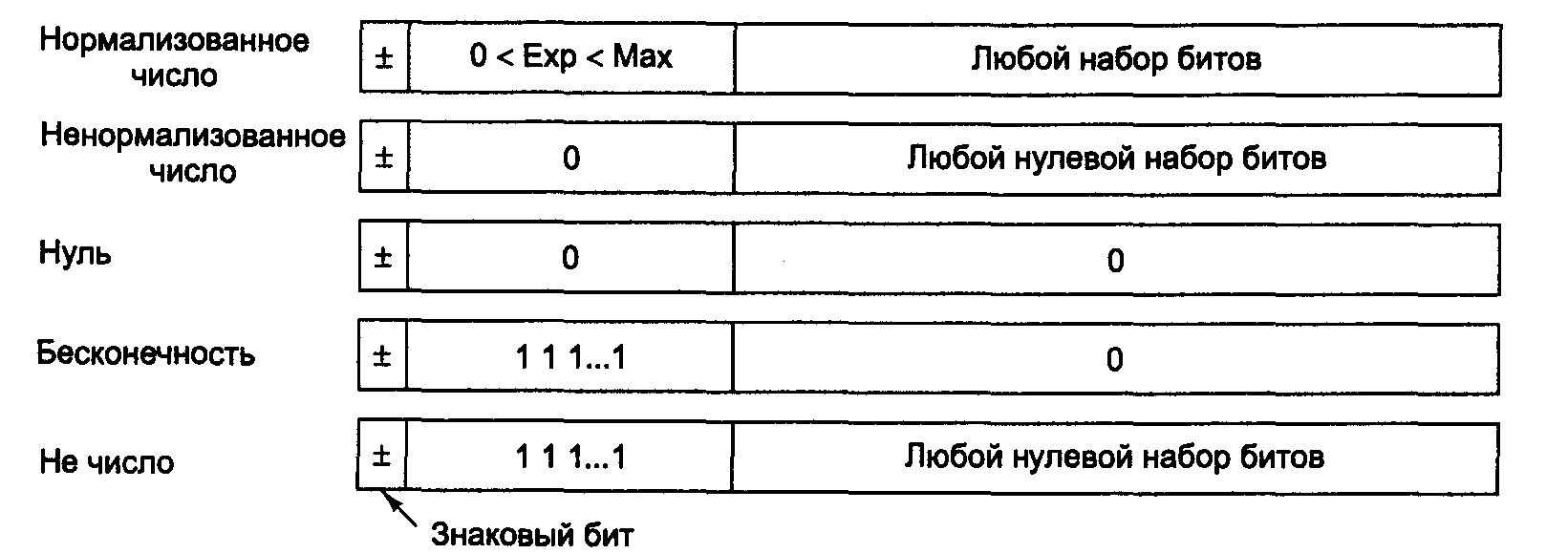

СТАНДАРТ IEEE 754 ДЛЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ 11

ДОПОЛНИТЕЛЬНЫЙ КОД 12

ДРОБНЫЕ ЧИСЛА С ФИКСИРОВАННОЙ ЗАПЯТОЙ 12

КОМПЛЕКСНЫЕ ЧИСЛА 12

МОДЕЛИ ПАМЯТИ 13

УРОВЕНЬ ОПЕРАЦИОННОЙ СИСТЕМЫ 14

ОБЗОР 14

ВИРТУАЛЬНАЯ ПАМЯТЬ 14

ПРОБЛЕМЫ ВИРТУАЛЬНОЙ ПАМЯТИ 14

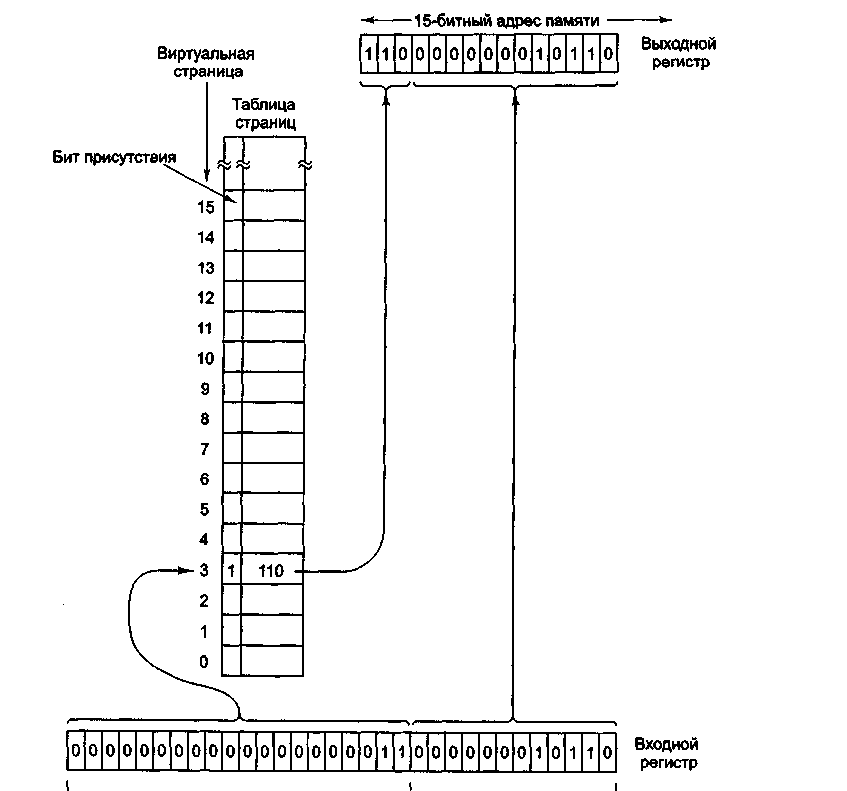

СТРАНИЧНАЯ ОРГАНИЗАЦИЯ ПАМЯТИ 15

ПРЕРЫВАНИЯ И ИСКЛЮЧЕНИЯ 16

УРОВЕНЬ ЯЗЫКА АССЕМБЛЕРА 17

ОБЗОР 17

ПРИМЕР ПРОГРАММЫ НА ЯЗЫКЕ АССЕМБЛЕР 17

ПРОЦЕСС АССЕМБЛИРОВАНИЯ 17

КОМПОНОВКА МОДУЛЕЙ 18

СВЯЗЬ С БИБЛИОТЕЧНЫМИ ФУНКЦИЯМИ 18

МИКРОАРХИТЕКТУРНЫЙ УРОВЕНЬ

ТРАКТ ДАННЫХ

1 – установка управляющих сигналов

2 – регистры выставляют данные на шины

3 – АЛУ выполняет операцию

4 – сохранение результатов

РЕГИСТРЫ ТРАКТА ДАННЫХ

РгАД – регистр адреса данных

РгАК – регистр адреса команд

РгД – регистр данных

РгК – регистр команд

Дополнительные регистры: флаговый, указатель стека и т.д.

УСТРОЙСТВО УПРАВЛЕНИЯ (МИКРОПРОГРАММНОЕ)

РЕАЛИЗАЦИЯ УСЛОВНЫХ ПЕРЕХОДОВ

АРХИТЕКТУРЫ УСТРОЙСТВ УПРАВЛЕНИЯ (ПРОЦЕССОРОВ)

RISC

CISC

VLIW

Современные x86

МЕТОДЫ ПОВЫШЕНИЯ ПРОИЗВОДИТЕЛЬНОСТИ

ОБЗОР

Технологические

Схемотехнические

Архитектурные

ПАРАЛЛЕЛЬНАЯ ОБРАБОТКА ДАННЫХ

|

|

Add Р1, Р2: 1. РN = R1; 3. Р1=RN+Р1; 4. РгАК=РгАК+1; 5. READ РгАК. |

Add Р1, Р2: 0. РгАК=РгАК+1; 1. Р1=Р1+Р2, READ РгАК, РгАК=РгАК+1; |

Суперскалярные процессоры

КОНВЕЙЕРИЗАЦИЯ

Такты |

Add Р1, Р2 |

Add Р3, Р4 |

Add Р5, Р6 |

1 |

B=Р1, C=Р2 |

|

|

2 |

A=B+C |

B=Р3, C=Р4 |

|

3 |

Р1=A |

A=B+C |

B=Р5, C=Р6 |

4 |

|

Р3=A |

A=B+C |

5 |

|

|

Р5=A |

Конвейеризованные процессоры

Изменение последовательности выполнения команд и подмена регистров

Изменение последовательности выполнения команд

Программа |

Реальный порядок команд |

Р1=Р2+Р3 |

Р1=Р2+Р3 |

Р4=Р1+Р5 |

Р6=Р7+Р8 |

Р6=Р7+Р8 |

Р4=Р1+Р5 |

Подмена регистров

Программа |

Реальный порядок команд и регистры |

Р1=Р2+Р3 |

Р1=Р2+Р3 |

Р4=Р1+Р5 |

Р5’=Р6+Р7 |

Р5=Р6+Р7 |

Р4=Р1+Р5 |

Некая команда |

Некая команда, Р5=Р5’ |

Проблема переходов

Безусловный переход

Стадии конвейера |

1 |

|

|

|

|

|

Выборка команды |

Код 1 |

Код 2 |

Код 3 |

??? |

Код X |

|

Декодирование |

|

INC |

JMP |

|

|

|

Выборка операндов |

|

|

А |

X |

|

|

Исполнение |

|

|

|

A+1 |

- |

|

Сохранение результатов |

|

|

|

|

! |

|

Условный переход

Стадии конвейера |

1 |

|

|

|

|

|

Выборка команды |

Код 1 |

Код 2 |

Код 3 |

??? |

??? |

Код X |

Декодирование |

|

INC |

JE |

|

|

|

Выборка операндов |

|

|

А |

X |

|

|

Исполнение |

|

|

|

A+1 |

|

|

Сохранение результатов |

|

|

|

|

! |

|

ПРОГНОЗИРОВАНИЕ ПЕРЕХОДОВ

Динамическое прогнозирование

Статическое прогнозирование

Двойное исполнение

УСЛОВНОЕ ИСПОЛНЕНИЕ

АРХИТЕКТУРА КОМАНД

ОБЗОР УРОВНЯ АРХИТЕКТУРЫ КОМАНД

МЕТОДЫ АДРЕСАЦИИ

Трехадресная |

ADD R1, R2, R3 |

R1 = R2 + R3 |

Двухадресная |

ADD R1, R2 |

R1 = R1 + R2 |

Одноадресная |

ADD R1 |

A = A+R1 |

Безадресная |

ADD |

A = A + B |

СПОСОБЫ АДРЕСАЦИИ

Непосредственная |

MOV R1, 4 |

Прямая |

MOV R1, [10] |

Регистровая |

MOV R1, R2 |

Косвенная регистровая |

MOV R1, [R2] |

Индексная |

MOV R1, 10+[R2] |

Относительная индексная |

MOV R1, [R2+R3] |

СТЕКОВАЯ АДРЕСАЦИЯ

ТИПЫ КОМАНД

Перемещения данных

Бинарные операции

Арифметические

Логические

Унарные операции

Сдвиги

Арифметические и логические

Сравнения и условные переходы

Вызова процедур

Управления циклом

Ввода-вывода

ТИПЫ ДАННЫХ

Числовые

Целые

Дробные

Вещественные

Комплексные

Нечисловые

Символьные (ASCII, UNICODE)

Логические (булевые)

Указатели и массивы

Битовые

СТАНДАРТ IEEE 754 ДЛЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ

ДОПОЛНИТЕЛЬНЫЙ КОД

510 = 0000 01012

-510 = 1111 10112

ДРОБНЫЕ ЧИСЛА С ФИКСИРОВАННОЙ ЗАПЯТОЙ

510 = 0000 01012

410 = 0000 01002

2010 = 0001 01002

1/410 = 0.010 00002

1/810 = 0.001 00002

1/3210 = 0.000 01002

КОМПЛЕКСНЫЕ ЧИСЛА

Порядок: Real-Imag.

МОДЕЛИ ПАМЯТИ

Байт

Слово

Выровненные данные:

|

0 |

1 |

2 |

3 |

0 |

dword |

|||

4 |

word |

|

|

|

8 |

char |

|

|

|

16 |

dword |

|||

Не выровненные данные:

|

0 |

1 |

2 |

3 |

0 |

dword |

|||

4 |

word |

char |

dword_начало |

|

8 |

dword_продолжение |

|

||

16 |

|

|

|

|

Порядок байтов:

Число: 0xA1B2C3D4

Порядок от младшего к старшему (little-endian) |

0xD4 |

0xC3 |

0xB2 |

0xA1 |

Порядок от старшего к младшему (big-endian) |

0xA1 |

0xB2 |

0xC3 |

0xD4 |

УРОВЕНЬ ОПЕРАЦИОННОЙ СИСТЕМЫ

ОБЗОР

Виртуальная память

Управление процессами

Драйвера устройств

ВИРТУАЛЬНАЯ ПАМЯТЬ

Проблемы работы с физической памятью:

Виртуальная память предоставляет свое адресное пространство (4Гб для современных процессоров) для каждого процесса.

ПРОБЛЕМЫ ВИРТУАЛЬНОЙ ПАМЯТИ

Загрузка и выгрузка страниц

Проблема фрагментации

Сегментация

СТРАНИЧНАЯ ОРГАНИЗАЦИЯ ПАМЯТИ

ПРЕРЫВАНИЯ И ИСКЛЮЧЕНИЯ

Источники прерываний

Источники исключений

Вектор обработки прерывания

Процедуры обработки прерываний

Использование прерываний для многозадачных систем

УРОВЕНЬ ЯЗЫКА АССЕМБЛЕРА

ОБЗОР

ПРИМЕР ПРОГРАММЫ НА ЯЗЫКЕ АССЕМБЛЕР

Метка

|

Код операции |

Операнды |

Комментарии |

FORMULA: |

MOV |

EAX, I |

; регистр ЕАХ=1 |

|

ADD |

EAX, J |

; регистр EAX=I+J |

|

MOV |

N, EAX |

; N=I+J |

I |

DW |

3 |

; резервируем 4 байта и устанавливаем значение 3 |

J |

DW |

4 |

; резервируем 4 байта и устанавливаем значение 4 |

N |

DW |

0 |

; резервируем 4 байта и устанавливаем значение 0 |