Сумматор

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов.

В отличие от полусумматора сумматор учитывает перенос из предыдущего разряда, поэтому имеет не два, а три входа.

Чтобы учесть перенос приходится схему усложнять. По-сути она получается, состоящей из двух полусумматоров.

Рассмотрим один из случаев. Требуется сложить 0 и 1, а также 1 из переноса. Сначала определяем сумму текущего разряда. Судя по левой схеме ИСКЛЮЧАЮЩЕЕ ИЛИ, куда входят a и b, на выходе получаем единицу. В следующее ИСКЛЮЧАЮЩЕЕ ИЛИ уже входят две единицы. Следовательно, сумма будет равна 0.

Теперь смотрим, что происходит с переносом. В один вентиль И входят 0 и 1 (a и b). Получаем 0. Во второй вентиль (правее) заходят две единицы, что дает 1. Проход через вентиль ИЛИ нуля от первого И и единицы от второго И дает нам 1.

Проверим работу схемы простым сложением 0 + 1 + 1 = 10. Т.е. 0 остается в текущем разряде, и единица переходит в старший. Следовательно, логическая схема работает верно.

Работу данной схемы при всех возможных входных значениях можно описать следующей таблицей истинности.

Структурная схема и принцип работы параллельного сумматора ( 3-х разрядный)

В параллельном сумматоре все разряды операндов суммируются одновременно, но быстродействие снижается за счет времени передачи цифры переноса из младшего разряда.

Структурная схема и принцип работы последовательного сумматора ( 3-х разрядный)

Последовательный сумматор осуществляет суммирование слагаемых и цифр переноса поразрядно, начиная с младшего разряда. Основой его схемы является одноразрядный сумматор. Суммирование производится в одноразрядном сумматоре SM. Цифры i-того разряда слагаемого и цифра переноса из младшего разряда передаются на вход сумматора одновременно с приходом тактового импульса. Регистры 1 и 2 используются для приема и хранения цифр i-того разряда слагаемых. В D - триггере хранится цифра переноса из младшего разряда. Регистр 3 принимает и хранит цифру i-того суммы. С приходом тактового импульса из регистров 1, 2 и D - триггера разряда слагаемых и цифра переноса поступает на вход одноразрядного сумматора. Одновременно регистр 3 освобождается для приема цифры суммы.

Арифметические устройства. Полувычитатель.

Арифметические устройства. Полный вычитатель.

Структурная схема и принцип работы параллельного полувычитателя ( 3-х разрядный)

Структурная схема и принцип работы параллельного вычитателя на сумматорах ( 3-х разрядный)

Компараторы

Цифровые компараторы (от лат. сотраrо — сравниваю) производят сравнение двух чисел с тем, чтобы выяснить, равны ли они или какое из них больше. Начнем с наиболее простого однораз-рядного компаратора. Из таблицы истинности (табл. 11.1) следуют аналитические выражения функций, реализуемых такими компараторами:

![]()

Приведенные формулы определяют два варианта схемы одно-разрядного компаратора, показанных на рис. 11.1. Для обоих вариантов схемы характерны равенства:

В первой схеме (см. рис. 11.1, а) устройство, реализующее функцию равнозначности, представлено в соответствии с рис. 6.14.

Рис. 11.1. Два варианта (а, б) схемы одноразрядного компаратора

Во второй схеме (см. рис. 11.1, б) вместо элемента И—ИЛИ—НЕ используются два конъюнктора и один элемент ИЛИ—НЕ, что позволяет несколько упростить компаратор (за счет применения одних и тех же конъюнкторов для формирования всех реализуемых функций).

Многоразрядные компараторы обычно выполняют на базе одноразрядных. При этом используется принцип последовательного сравнения разрядов многоразрядных чисел, начиная с их старших разрядов, так как уже на этом этапе, если x1m 4>№ x2m, задача может быть решена однозначно, и сравнение следующих за старшими разрядов не потребуется.

Таблицы истинности. Переключательные функции

Таблица истинности — это таблица, описывающая логическую функцию.

Под

«логической функцией» в данном случае

понимается функция, у которой значения

переменных (параметров функции) и

значение самой функции выражают

логическую истинность. Например, в

двузначной логике они могут принимать

значения «истина» либо «ложь» (![]() либо

либо

![]() ,

,

![]() либо

либо

![]() ).

).

Табличное задание функций встречается не только в логике, но для логических функций таблицы оказались особенно удобными, и с начала XX века за ними закрепилось это специальное название. Особенно часто таблицы истинности применяются в булевой алгебре и в аналогичных системах многозначной логики.

Переключательной функцией называется такая функция от нескольких аргументов, все аргументы которой являются высказываниями, и значение которой также является высказыванием.(Иначе говоря, это логическая функция от логических аргументов).

Мультиплексор. Переключательные функции и схема 4-х ходового мультиплексора.

Мультиплексор

(от англ, multiplexer) операционный узел ЦВМ,

осуществляющий микрооперацию передачи

сигнала с любого информационного входа

на один выход. Мультиплексор осуществляет

функцию, обратную функции демультиплексора.

При помощи k адресных входов ![]() в

мультиплексоре можно выбирать один из

n = 2k информационных сигналов

в

мультиплексоре можно выбирать один из

n = 2k информационных сигналов ![]() для

передачи его на один выход. С выходом

соединяется тот вход, индекс i которого

равен десятичному значению двоичного

числа, определяемого адресными

переменными.

для

передачи его на один выход. С выходом

соединяется тот вход, индекс i которого

равен десятичному значению двоичного

числа, определяемого адресными

переменными.

Рис. 4.48.

Например, мультиплексор на 4 входа имеет переключательную функцию

![]() (4.6.)

(4.6.)

При а1 = 1, a0 = 0

![]()

Мультиплексор применяют: для преобразования параллельных цифровых кодов в последовательные с целью экономии числа контактов и линий связи; на выходах блоков при считывании информации по одной разрядной шине; в многоразрядных сдвигателях информации; для реализации различных булевых функций.

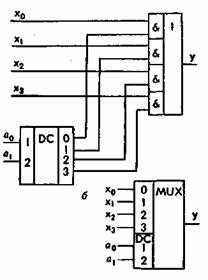

В соответствии с булевой функцией (4.6) на рис. 4.49, а, приведена функциональная схема мультиплексора на 4 канала со стробированием, а на рис. 4.49, б — его УГО.

При ![]() =

0 мультиплексор функционирует в

соответствии с выражением (4.6), при

=

1 y = 0 независимо от входов xi и аj.

=

0 мультиплексор функционирует в

соответствии с выражением (4.6), при

=

1 y = 0 независимо от входов xi и аj.

Для мультиплексора со стробированием (рис. 4.49, а)

![]()

Выражение (4.6) можно записать следующим образом:

![]() (4.7.)

(4.7.)

где ![]() ,

, ![]() ,

, ![]() ,

, ![]() —

выходы двухразрядного двоичного

дешифратора. С учетом (4.7) функциональная

схема мультиплексора приведена на рис.

4.50, а, его УГО — на рис. 4.50, б.

—

выходы двухразрядного двоичного

дешифратора. С учетом (4.7) функциональная

схема мультиплексора приведена на рис.

4.50, а, его УГО — на рис. 4.50, б.

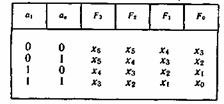

На

рис. 4.51 показан пример построения

комбинационного устройства сдвига на

четырех мультипликаторах МUX 4—1, а в

табл. 4.10 — закон его функционирования.

При изменении адреса, например

с ![]() ,

, ![]() на

на ![]() ,

, ![]() на

выходах F3 — F0 появляется сдвинутый

на один разряд влево код X.

на

выходах F3 — F0 появляется сдвинутый

на один разряд влево код X.

Рис. 4.49.

Рис. 4.50.

С помощью мультиплексора можно реализовать любые булевы функции адресных переменных. Закон функционирования MUX 4—1 (рис. 4.50) отражен в табл. 4.11. Там же приведены значения функции у1сложения по модулю 2 адресных переменных. Для реализации функции у1 необходимо на входы мультиплексора подать сигналы x0 = х3 = 0, х1 = x2 = 1 (рис. 4.52).

Таблица 4.10.

Таблица 4.11.

При необходимости увеличения числа входов xi мультиплексора можно применить, например, каскадное соединение. На рис. 4.53 приведен пример построения MUX 16—1 из MUX 4—1.

Рис. 4.51.

Рис. 4.52.

Рис. 4.53.

М

Рис. 7 Модель мультиплексора в середовищі Multisim

ультиплексори (англійське Multiplexer) призначені для почергової передачі на один вихід одного з декількох вхідних сигналів, тобто для їх мультиплексування. Кількість мультиплексованих входів називається кількістю каналів мультиплексора, а кількість виходів називається числом розрядів мультиплексора.Керування роботою мультиплексора (вибір номеру каналу) здійснюється за допомогою вхідного коду, що подається на адресні входи. Наприклад, для 4-канального мультиплексора необхідний 2-розрядний код, управляючий код, а для 16-канального — 4-розрядний код. Розряди коду можуть позначаються як 1, 2, 4, 8 або А0, А1, А2, А3.

Деякі мікросхеми мультиплексорів мають вхід дозволу (заборони) «G», який при подачі на нього активного сигналу відключає виходи. На рис. 7 Зображено 4 канальний, однорозрядний мультиплексор із входом заборони.

Мікросхеми мультиплексорів можна об'єднувати для збільшення кількості каналів. Наприклад, два 4-канальних мультиплексора легко об'єднуються в 8-канальний за допомогою інвертора на входах дозволу і елементу І-НІ для об’єднання вихідних сигналів мультплексорів в один (рис. 8). Старший розряд коду при цьому вибиратиме один з двох мультиплексорів. Так само з двох 16-канальних мультиплексорів можна зробити 32-канальний. Якщо потрібне більше число каналів, то необхідно замість інвертора включати дешифратор, на який подаються старші розряди коду. Вихідні сигнали дешифратора вибиратимуть один з мультиплексорів. На рис. 8 Зображено одно розрядний, восьми канальний мультиплексом побудований на основі двох чотириканальних. Принцип роботи схеми полягає в наступному: при появі на адресній лінії А2 активного сигналу він відключає мультиплексом першого каскаду U1 який відповідає за молодші канали. Далі сигнал лінії А2 поступає на інвертор та дозволяє роботу мультиплексору U2. Адресні лінії молодших розрядів подаються на обидва мультиплексори паралельно, так як працює лише один з них на виході з’являється сигнал з входу, що відповідає коду.

Рис. 8 Мультиплексор на побудований на основі схем з меншою кількістю входів

Мультиплексор можна використовувати як основу для синтезу комбінаційних схем із довільною таблицею істинності. В цьому випадку виходячи з таблиці істинності на вхідні канали мультиплексора подаються активні сигнали. При подачі різних комбінацій сигналів на адресні входи мультиплексора на його виході буде з’являтися або зникати активний сигнал перетворюючи його на комбінаційну схему.

Нехай дано наступну таблицю істинності:

X1 |

X2 |

X3 |

Y |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Як видно, при комбінації вхідних сигналів, що відповідають 0, 2, 3, 5, 6, 7 вихідний сигнал повинен становити логічну 1. Схема, що реалізує представлену таблицю істинності наведено на рис. 9

Рис 9. Комбінаційна схема реалізована на мультиплексорі

Мультиплексор. Реализация. Переключающиеся функции на мультиплексоре.

Мультиплексор – это комбинационная многовходовая схема с одним выходом. Входы мультиплексора подразделяются на информационные Д0, Д1, …, Дn-1 и управляющие (адресные) А0, А1, …, Аk-1. Обычно 2k = n, где k и n – число адресных и информационных входов соответственно. Двоичный код, поступающий на адресные входы, определяет (выбирает) один из информационных входов, значение переменной с которого передается на выход y, т.е. мультиплексор реализует функцию:

,

если

,

если

(1)

(1)

Таблица функционирования, описывающая работу мультиплексора, имеющего, например, n = 4 информационных (Д0, Д1, Д2, Д3) и k = 2 адресных (А0, А1) входов, представлена в табл. 1.

Вариант схемной реализации мультиплексора “4-1” (“четыре в один”, т.е. коммутирующего данные от одного из четырех входов на единственный выход) и его условное графическое изображение представлены на рис. 1.

Здесь мультиплексор построен как совокупность двухвходовых конъюкторов данных (их число равно числу информационных входов), управляемых выходными сигналами дешифратора, дешифрирующего двоичный адресный код. Выходы конъюкторов объединены схемой ИЛИ.

Рис. 1. Схема мультиплексора с дешифратором (а)

и и его условное графическоеизображение

В интегральном исполнении применяется более простая схема, в которой конъюкторы дешифратора одновременно выполняют и функцию конъюкторов данных. Работа мультиплексора при этом описывается соотношением

(2)

(2)

Из (2) следует, что при любом значении адресного кода все слагаемые, кроме одного равны нулю. Ненулевое слагаемое равно Дi, где i – значение текущего адресного кода.

В соответствии с этим соотношением

строятся реальные схемы мультиплексоров,

одна из которых для мультиплексора

“четыре в один” приведена на рис. 2. Как

правило, схема дополняется входом

разрешения работы – Е (показан пунктирной

линией). При отсутствии разрешения

работы (Е=0) выход у становится нулевым

и не зависит от комбинации сигналов на

информационных и адресных входах

мультиплексора.

соответствии с этим соотношением

строятся реальные схемы мультиплексоров,

одна из которых для мультиплексора

“четыре в один” приведена на рис. 2. Как

правило, схема дополняется входом

разрешения работы – Е (показан пунктирной

линией). При отсутствии разрешения

работы (Е=0) выход у становится нулевым

и не зависит от комбинации сигналов на

информационных и адресных входах

мультиплексора.

Мультиплексоры 4-1, 8-1, 16-1 выпускаются в составе многих серий цифровых интегральных схем и имеют буквенный код КП. Например, К555КП1 – мультиплексор 2-1 (в данном корпусе размещаются четыре мультиплексора), К555КП12 – мультиплексор 4-1 (в одном корпусе размещаются два мультиплексора) и т.д.

В тех случаях, когда функциональные возможности ИС мультиплексоров не удовлетворяют разработчиков по числу информационных входов, прибегают к их каскадированию с целью наращивания числа входов до требуемого значения. Наиболее универсальный способ наращивания размерности мультиплексора состоит в построении пирамидальной структуры, состоящей из нескольких мультиплексоров. При этом первый ярус схемы представляет собой столбец, содержащий столько мультиплексоров, сколько необходимо для получения нужного числа информационных входов. Все мультиплексоры этого столбца коммутируются одним и тем же адресным кодом, составленным из соответствующего числа младших разрядов общего адресного кода. Старшие разряды адресного кода используются во втором ярусе, мультиплексор которого обеспечивает поочередную работу мультиплексоров первого яруса на общий выход.

П

Де-мультиплексор. Структурная схема и переключающиеся функции 3-х разрядного Де-мультиплексора

Дешифраторы. Линейный дешифратор. Реализация переключающийся функции на дешифраторе.

Дешифраторы. Параллельный дешифратор. Реализация переключающейся функции на дешифраторе.

Цифровые счетчики. Асинхронный суммирующий.

Цифровые счетчики. Асинхронный вычитающий.

Цифровые счетчики. Синхронные счетчики. Этапы синтеза счетчика.

Синхронные счетчики с произвольным коэффициентом счета. Этапы синтеза счетчика.

RS-тригер. Таблицы переходов. Синтез. А-синхронный и синхронный RS-тригер.

JS-тригер. Таблицы переходов. Синтез. А-синхронный и синхронный JS-тригер.

D-тригер .Таблицы переходов. Синтез. А-синхронный и синхронный D-тригер.

Переключающиеся функции. Представление функции с помощью дизъюнктивной нормальной формы.

Переключающиеся функции. Представление функции с помощью конъюнктивной нормальной формы.

Вычислительные правила булевой алгебры. Теорема Де-Моргана.

Цифровые ЗУ. Постоянные (ROM) и программируемые (PROM) запоминающие устройства. Общая структура. Структура ячеек.

Цифровые ЗУ. Постоянные перепрограммируемые. Общая структура и структура ячеек.

Цифровые ЗУ. Оперативные ЗУ статического типа. Общая структура.

Алгоритм синтеза комбинационных схем. Функционально полные базисы.