Приоритетные триггеры

Триггеры, у которых одни входы имеют преимущество над другими в установлении сигналов на выходе, называются приоритетными.

К таким устройствам относятся разновидности RS–триггера, а именно: R, S, E-триггеры (рис. 10, таблица истинности табл. 8).

Последняя строка этой таблицы определяет приоритет соответствующего входа.

Таблица истинности RS -триггеров Таблица 8

R -триггер |

|

S -триггер |

|

E -триггер |

||||||

R |

S |

Qn+1 |

|

R |

S |

Qn+1 |

|

R |

S |

Qn+1 |

0 |

0 |

Q n |

|

0 |

0 |

Q n |

|

0 |

0 |

Q n |

0 |

1 |

1 |

|

0 |

1 |

1 |

|

0 |

1 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

1 |

1 |

1 |

|

1 |

1 |

Q n |

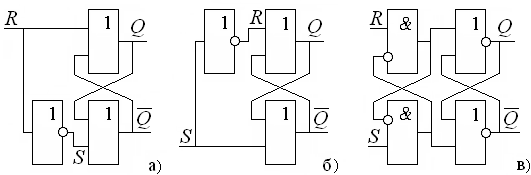

Схема E-триггера устанавливает преимущество входного сигнала R или S, который появился на входе первым с помощью логической операции Импликация.

Пришедший первым сигнал (логическая единица) инвертируется и устанавливает запрет на поступление сигнала на второй вход.

Рис. Приоритетные триггеры на основе RS-триггера:

а – R-триггер; б – S-триггер; в – E-триггер

Пример E-триггер исключает зажигание сигналов светофора одинакового цвета для различных направлений движения транспорта.

При одновременном ошибочном нажатии двух клавиш клавиатуры, данный триггер вводит в компьютер код только одной из них.

Приоритетные триггеры позволяют предотвратить сбои и ошибки в работе различных устройств.

JK-триггер

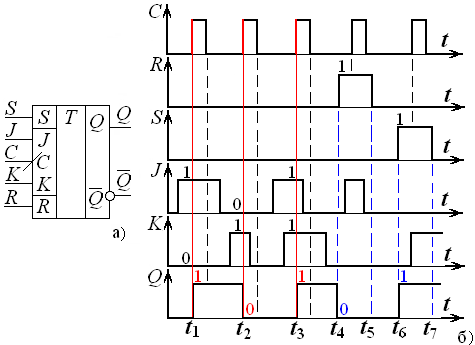

JK-триггер имеет два информационных входа J и K, тактовый динамический вход C, и два приоритетных асинхронных входа установки S и сброса R (рис. ).

Рис. JK-триггер:

а – принципиальная схема;

б – временные диаграммы работы

В таблице истинности триггера (табл. 9) значком «Х» обозначаются произвольные значения переменных J, K и C, которые не оказывают влияния на результат вследствие приоритета входов R, S (моменты времени t4, t5, t6, t7). Этим же определяется нестабильность при R = S = 1, т.к. схема работает как асинхронный RS-триггер.

В случае если R = S = 0, асинхронный триггер переходит в режим хранения и разрешается работа синхронного динамического JK-триггера. Запись информации происходит, для данной схемы триггера, по переднему фронту (0-1) сигнала на входе C (моменты времени t1, t2, t3).

Когда на входах J=K=1, происходит инверсия предыдущего значения на выходах триггера (момент времени t3).

Таблица истинности JK-триггера Таблица 9

№ |

R |

S |

C |

J |

K |

Q n+1 |

1 |

0 |

0 |

0-1 |

0 |

0 |

Q n |

2 |

0 |

0 |

0-1 |

0 |

1 |

0 |

3 |

0 |

0 |

0-1 |

1 |

0 |

1 |

4 |

0 |

0 |

0-1 |

1 |

1 |

Q n’ |

5 |

0 |

0 |

1-0 |

X |

X |

Q n |

6 |

0 |

0 |

0 |

X |

X |

Q n |

7 |

0 |

1 |

X |

X |

X |

1 |

8 |

1 |

0 |

X |

X |

X |

0 |

9 |

1 |

1 |

X |

X |

X |

– |

Если построить полную таблицу истинности JK-триггера, то можно получить аналитическое выражение его работы:

![]()