Лекция 13. Триггеры. Основные теоретические положения

Триггер (защелка) – импульсное устройство с двумя устойчивыми состояниями.

Переход из одного состояния в другое происходит в результате воздействия сигналов управления.

Выходной сигнал триггера зависит не только от входных сигналов, но и от его внутреннего состояния, то есть от значений входных переменных, которые действовали в предыдущие моменты времени.

Следовательно, триггеры являются элементами памяти.

Электронные приборы с такими свойствами называются последовательными логическими устройствами.

Кроме устойчивых состояний, которые могут сохраняться неограниченно долго, имеются неустойчивые, они существуют короткое время, соизмеримое с длительностью процессов переключения в схеме.

Пример. Простейшим триггером является выключатель освещения. Он имеет два устойчивых состояния и переключается кратковременным внешним воздействием.

Пример. Использование кнопок без фиксации состояния для операций включения – выключения электрооборудования позволяет управлять объектами из различных мест.

При этом нет необходимости, для выключения какой либо установки, выявлять и отключать включенные кнопки. Достаточно выработать соответствующий сигнал управления силовым выключателем установки, который работает в режиме триггера (самоблокировка).

Простейшие триггеры на основе реле и инверторов представлены на рисунке 1.

Рис. 1 Триггеры на основе:

а – инверторов; б – реле; в – реле и кнопок управления

Устройство (рис. 1, а) может находиться в двух устойчивых состояниях входов – выходов, соответственно 1–0–0–1 и 0–1–1–0. Такая ячейка памяти называется бистабильной. Она может быть реализована на основе реле K1, K2 с нормально замкнутыми контактами K1, K2 по схеме рис. 1, б. При подаче напряжения Uп одно из реле сработает быстрее и разомкнет цепи питания другого реле.

Однако таким устройством нельзя управлять.

Для управления триггером используются дополнительные элементы, позволяющие перевести его в то или иное положение, например, кнопки SB1 и SB2 (рис. 1, в). Ими можно вручную перевести триггер из одного состояния в другое.

Указанные логические элементы, выполненные на основе реле, используются, в схемах релейной защиты, автоматики, для коммутации и развязки по напряжению в силовых исполнительных элементах.

Классификация триггеров

Обычно триггер имеет два выхода: Q – прямой выход, Q’ – инверсный, если Q =1, то Q’=0 и наоборот.

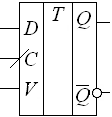

На схемах триггеры обозначаются символом D и порядковым номером на схеме (рис. 2).

Входы обозначаются в соответствии с видом и назначением триггера (на рисунке не указаны).

Рис. 2 Обозначение триггера

Триггеры можно классифицировать по способам записи информации и управления, принципам построения, функциональным возможностям.

По способу записи информации различают асинхронные и синхронные триггеры.

Асинхронный триггер изменяет свое состояние в момент прихода сигнала на его информационные входы.

Синхронные триггеры меняют свое состояние под действием входных сигналов, только в момент прихода тактового сигнала на синхронизирующий вход С.

Они могут использоваться в сложных цифровых устройствах, где разделение работы на временные такты, когда выполняются определенные операции, исключает путаницу и сбои.

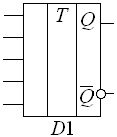

По способу записи информации входы триггеров разделяются на статические и динамические.

Первые реагируют на состояния входов (обозначение на рис. 2) и переключаются при наличии соответствующего потенциала (уровня напряжения). Динамические входы реагируют на изменения состояния на входах и управляются переходом между потенциалами.

Передним фронтом импульса из 0 в 1 (варианты обозначения на рис. 3, а) или задним фронтом из 1 в 0 (рис. 3, б).

Рис. 3 Обозначения динамических входов, а:

переключение по переднему фронту,

б: переключение по заднему фронту

По функциональным возможностям различают триггеры: RS-триггер, D-триггер, T-триггер, JK-триггер, VD и VT-триггеры, а также NV-триггеры, которые после выключения напряжения питания сохраняют записанную в них информацию (энергетическая независимость).

Асинхронный RS-триггер

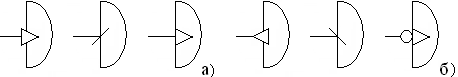

Асинхронный RS-триггер может быть реализован с помощью элементов 2ИЛИ-НЕ (рис. 4, а), таблица истинности (табл. 1). Он имеет два входа: S(et) установка (Q =1) и R(eset) сброс (Q =0).

Согласно временной диаграмме (рис. 4, б) и табл. 1, выход триггера переходит в состояние Q n+1 =1, если поступают сигналы S =1, R =0 (интервал времени t1 – t2) независимо от предшествующего состояния Q n.

При S =0, R = 1 выход триггера переходит в состояние Q n+1 = 0 (интервал t3 – t4). Когда S =0, R =0 триггер сохраняет прежнее значение Q n (интервалы t2 – t3; t4 – t5).

Комбинация сигналов S =1, R =1 запрещена, т.к. на прямом Q и инверсном Q’ выходе устанавливаются одинаковые значения, которые при переходе в режим хранения не удерживаются (интервал t6 – t7).

Рис. 4 Асинхронный RS-триггер на элементах 2ИЛИ-НЕ:

а – принципиальная схема;

б – временные диаграммы работы

Таблица истинности RS-триггера Таблица 1

№ |

R |

S |

Q n+1 |

Q’ n+1 |

Название режима работы |

1 |

0 |

0 |

Q n |

Q’ n |

Хранение информации |

2 |

0 |

1 |

1 |

0 |

Установка в 1 |

3 |

1 |

0 |

0 |

1 |

Установка в 0 |

4 |

1 |

1 |

– |

– |

Запрещенное состояние |

Для получения аналитического выражения при разработке схемы асинхронного RS-триггера необходимо составить полную таблицу истинности (табл. 2).

Полная таблица истинности RS-триггера Таблица 2

№ |

R |

S |

Q n |

Q n+1 |

1 |

0 |

0 |

0 |

0 |

2 |

0 |

0 |

1 |

1 |

3 |

0 |

1 |

0 |

1 |

4 |

0 |

1 |

1 |

1 |

5 |

1 |

0 |

0 |

0 |

6 |

1 |

0 |

1 |

0 |

7 |

1 |

1 |

0 |

– |

8 |

1 |

1 |

1 |

– |

Наборам, где Q n+1 = 1, соответствует характеристическое уравнение:

В наборах 7, 8, где значение выхода не определено, можно указать 0 или 1 исходя из соображений простоты реализации схемы (рис. 4, а), которая составлена согласно полученному аналитическому выражению.

Асинхронный RS-триггер может быть собран на элементах 2И-НЕ (рис. 5, а), таблица истинности (табл. 3). В отличие от предыдущей схемы, триггер имеет инверсные входы.

Рис. 5 Асинхронный RS-триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности RS-триггера Таблица 3

№ |

R’ |

S’ |

Q n+1 |

Q’ n+1 |

1 |

1 |

1 |

Q n |

Q’ n |

2 |

1 |

0 |

1 |

0 |

3 |

0 |

1 |

0 |

1 |

4 |

0 |

0 |

– |

– |

Анализ работы триггера (рисунки 4, а; 5, а) выполняется по следующему алгоритму:

- задать исходные значения выходов, например, Q n =0, Q’ n =1;

- выбирать значения входных сигналов R, S в соответствии с таблицей истинности;

- выполнить логические операции c заданными Q n и выбранными значениями R, S;

- новые (полученные) значения выходов Q n+1 подать на входы и еще раз выполнить логические операции из-за возможности появления неустойчивых состояний.

На основе RS-триггера получен ряд триггеров с различными функциональными возможностями.

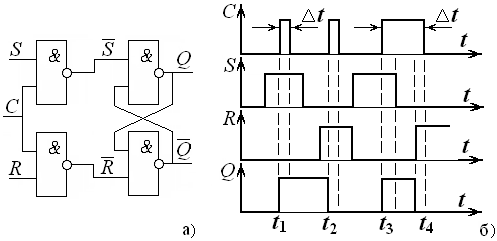

Например, синхронный RS-триггер (рис. 6), его таблица истинности табл. 4.

Рис. 6 Синхронный RS-триггер на элементах 2И-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности синхронного RS-триггера Таблица 4

№ |

C |

R |

S |

Q n+1 |

Q’ n+1 |

1 |

1 |

0 |

0 |

Q n |

Q’ n |

2 |

1 |

0 |

1 |

1 |

0 |

3 |

1 |

1 |

0 |

0 |

1 |

4 |

1 |

1 |

1 |

– |

– |

5 |

0 |

X |

X |

Q n |

Q’ n |

X – любое значение переменной, которая не оказывает влияния на результат.

Считывание сигналов с информационных входов R, S происходит при наличии тактового сигнала C на интервале времени t, когда триггер работает как статическое устройство. Если в течение этого интервала по какой-либо причине происходит изменение входных сигналов R, S, то оно оказывает влияние на состояние выходов (интервал времени t3 – t4).

Чтобы сократить время считывания (приблизительно до пяти наносекунд) и таким образом повысить помехозащищенность триггера, тактовый вход C делают динамическим.

D-триггер

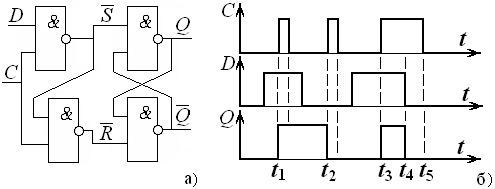

Схема D-триггера (рис. 7) имеет один информационный вход D и тактовый вход C, его таблица истинности табл. 5.

Триггер является простейшей ячейкой памяти и применяется только как синхронный элемент.

Рис. 7 D-триггер на элементах 2И-НЕ:

а – принципиальная схема;

б – временные диаграммы работы

Таблица истинности D-триггера Таблица 5

№ |

C |

D |

Q n+1 |

1 |

1 |

0 |

0 |

2 |

1 |

1 |

1 |

3 |

0 |

X |

Q n |

На рисунке 7 представлен синхронный потенциальный D-триггер. Если при наличии тактового сигнала C (интервал t3 – t5), происходит изменение входного сигнала D (в момент времени t4), то это оказывает влияние на состояние выходов.

Чтобы повысить помехозащищенность триггера, тактовый вход C делают динамическим.

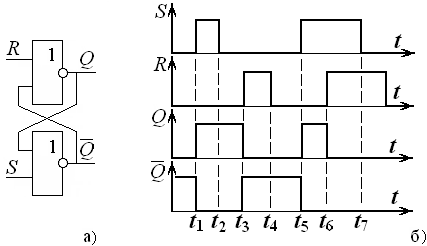

Если в схему D-триггера добавить разрешающий вход V, то такое устройство называется DV-триггером (рис. 8), таблица истинности табл. 6.

Таблица истинности DV-триггера Таблица 6 |

|

||||

№ |

V |

C |

D |

Q n+1 |

|

1 |

1 |

1 |

0 |

0 |

|

2 |

1 |

1 |

1 |

1 |

|

3 |

0 |

0 |

X |

Q n |

|

4 |

0 |

1 |

X |

Q n |

|

5 |

1 |

0 |

X |

Q n |

|

Рис. 8 DV-триггер

Данные триггеры применяются:

- для задержки прохождения сигнала до появления тактового импульса;

- в регистрах и счетчиках;

- в запоминающих устройствах, требующих большого числа простых ячеек памяти.

T-триггер

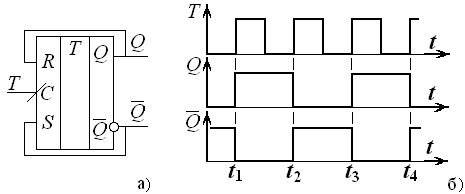

Схема T-триггера (рис. 9) имеет один информационный динамический вход T, его таблица истинности табл. 7. Если в схему T-триггера добавить разрешающий вход V, то такое устройство называется TV-триггером (по аналогии с DV-триггером).

Таблица истинности T-триггера Таблица 7

№ |

T |

Q n |

Q n+1 |

1 |

1 |

0 |

1 |

2 |

1 |

1 |

0 |

Рис. T-триггер на основе RS-триггера:

а – принципиальная схема;

б – временные диаграммы работы

Согласно временной диаграмме, в исходном состоянии Q =0, Q’ =1, на входе R =0, S=1.

По переднему фронту тактового импульса T=1 сигналы с выходов запишутся в триггер и установятся новые значения Q =1, Q’ =0 (в момент времени t1). Очередной тактовый импульс запишет их в триггер и в момент времени t2 установятся значения Q =0, Q’ =1.

Данный триггер применяется:

- для изменения знака двоичного числа в арифметико-логическом устройстве;

- в счетчиках, делителях частоты;

- в регистрах.