- •Лекция. Процессоры Core i7 (Nehalem) фирмы Intel

- •Подсистема кэширования

- •Технология Turbo Boost

- •Считывание и декодирование инструкций

- •Предсказание ветвлений

- •Возвращение Hyper–Threading

- •Соединения QuickPath.

- •Процессоры Intel Core i5 и Core i7 с ядром Lynnfield

- •Процессоры Intel новой архитектуры Sandy Bridge («песчаный мост»)

- •Intel ivy bridge: подробности о микроархитектуре

Лекция. Процессоры Core i7 (Nehalem) фирмы Intel

(ядро Bloomfield, Socket LGA1366).

6 ноября 2008 года корпорация Intel официально представила Core i7 – первые процессоры архитектуры Nehalem. Новая линейка CPU принимает эстафету у суперуспешной разработки Intel Core. Оба поколения процессоров будут продаваться параллельно, вплоть до анонса двухъядерников Havendale, использующих микроархитектуру Intel Nehalem и разъем LGA1366.

Выпуск четырехъядерников Core i7 должен закрепить подавляющее преимущество Intel в секторе наиболее производительных решений. Кроме того, с анонсом Core i7 возвращается подзабытая технология Hyper-Threading, обеспечивающая многопоточную обработку данных в пределах одного физического ядра. Этот факт должен побудить разработчиков ПО к дальнейшей оптимизации софта для процессоров с числом ядер больше двух.

Выход Nehalem полностью согласуется с фирменной концепцией Intel: появление новой архитектуры один раз в два года. Так, эра Intel Core 2 началась в июле 2006-го с выпуском процессоров Conroe. Далее последовал переход на 45-нм технологическую норму (семейство Penryn). И вот, с сегодняшнего дня, мы имеем дело с Core i7 – представителями архитектуры Nehalem на ядре Bloomfield.

|

Эволюция процессоров Intel |

Архитектура

Согласно официальным сведениям первые процессоры Nehalem обладают, по крайней мере, 731 млн. транзисторов, что на 10,7% меньше, чем у «квадов» Penryn Yorkfield. В то же время, площадь кристалла Core i7 увеличена с 214 до 263 мм2.

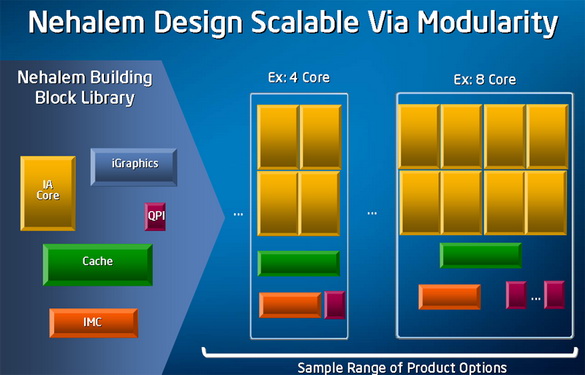

Архитектура Nehalem изначально была разработана как модульная. Инженеры Intel хотели создать набор базовых "кирпичей, которые можно собирать как блоки конструктора Lego, чтобы создавать разные версии архитектуры.

|

Модульная архитектура Nehalem. |

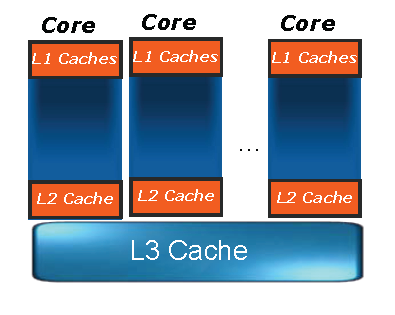

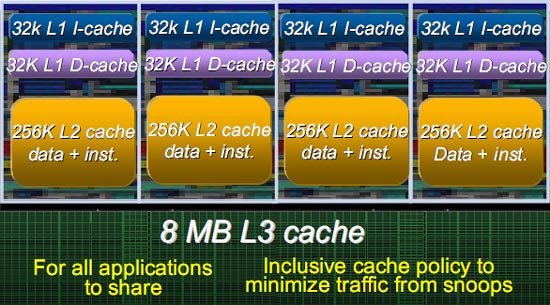

Основной чертой новой архитектуры стала модульность. Главный модуль представляет собой классический одноядерный x86-процессор: он состоит из исполнительного ядра, L1 Cache размером 64 КБ, поделенного на 2 равные части для данных и инструкций и L2 Cache размером 256 КБ.

Прочие блоки могут быть следующими:

разделяемый L3 Cache;

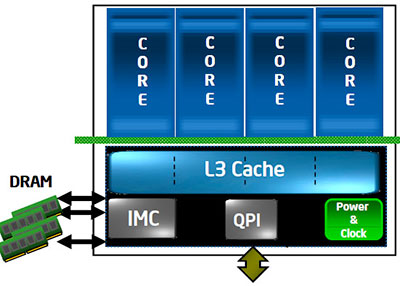

контроллер памяти;

контроллер шины QPI (QuickPath Interconnect);

контроллер шины PCI Express (пока не реализовано);

контроллер энергопотребления (PCU) и генератор частот;

контроллер интегрированной графики.

Впрочем, не следует считать, что это строго фиксированный список, и ни одного пункта больше архитектура Core i7 включить не позволяет. Скорее данный набор базовых элементов явился демонстрацией намерений Intel по дальнейшему усовершенствованию архитектуры – недаром в него вошёл контроллер интегрированной графики, на тот момент ни в одном процессоре Core i7 ещё не присутствующий. Всё это вместе может комбинироваться произвольным образом, причём допускается как наличие, или отсутствие определённых модулей, так и различное их количество внутри процессора. Модель Core i7 920 выглядит, например, так:

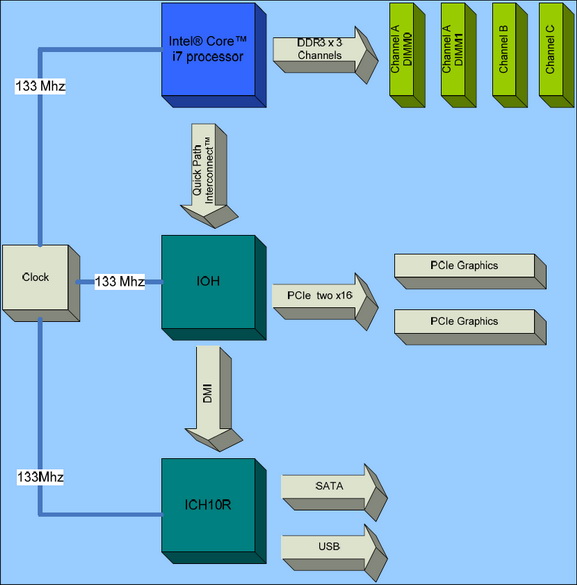

Как легко заметить, она включает в себя четыре процессорных ядра, один трёхканальный контроллер памяти DDR3, один контроллер шины QPI для общения с чипсетом, и модуль отвечающий за генерацию необходимых процессору для работы частот и управление энергопотреблением. С другой стороны, это лишь один из возможных вариантов, реализованный в данной конкретной модели. Например, если на базе новой архитектуры создавать серверный процессор — то не лишним будет увеличить количество не только ядер, но и контроллеров QPI, если же, наоборот, мы разрабатываем мобильный CPU — можно сократить количество ядер, чтобы уменьшить энергопотребление и заменить контроллер чересчур быстрой QPI на обычную PCI Express. Чисто теоретически, никто, наверное, не мешает убрать и L3, оставив всего по минимуму: одно исполнительное ядро, контроллер памяти, PCI-E (Celeron?..) Таким образом, главная цель Intel, похоже, достигнута: у неё есть модульная архитектура с достаточно небольшим количеством основных модулей, из которых, комбинируя их произвольным путём, можно достаточно легко «слепить» как скромный low-end процессор для какого-нибудь неттопа, так и многоядерного серверного монстра. И всё это — из одних и тех же модулей, вот в чём основная прелесть! Однако, разумеется, не только в модульности дело, есть и другие важные изменения. Давайте рассмотрим их подробнее.

|

Архитектура Core i7. |

Но Intel не только обновила свою архитектуру, взяв у конкурента интересные инновации. С бюджетом более 700 млн. транзисторов (731 млн., если быть точным), инженеры смогли серьёзно улучшить основные характеристики исполнительного ядра, добавив в то же время новую функциональность. Например, поддержка многопоточности (simultaneous multi-threading, SMT), которая впервые появилась в Pentium 4 "Northwood" под названием Hyper-Threading, вновь вернулась. Поскольку физических ядер на кристалле четыре, некоторые версии Nehalem, которые используют два ядра в одной упаковке, смогут выполнять до 16 потоков одновременно.

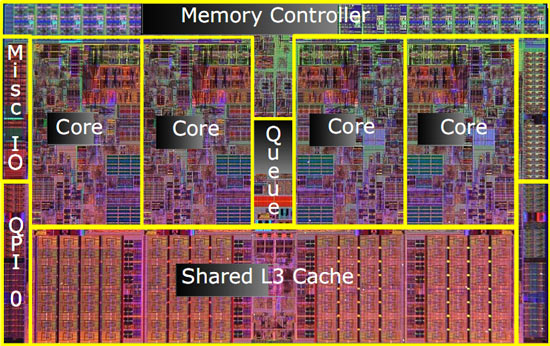

Первые процессоры Core i7 с ядром Bloomfield имели четырехъядерный дизайн, тогда как структура их предшественников – Core 2 Quad – представляла собой мультичиповый модуль из пары Core 2 Duo. К числу основных элементов кристалла Core i7 принадлежат четыре физических ядра, разделяемый L3 Cache, встроенный контроллер памяти DDR3 и шина QuickPath Interconnect (QPI).

|

Структура кристалла Core i7 |

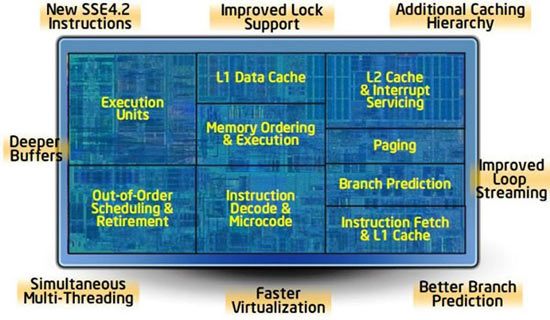

Каждое из четырех ядер Bloomfield, в свою очередь, распределяется на меньшие блоки.

|

Устройство ядра Bloomfield. |

Трёхуровневая иерархия Cache

Иерархия памяти в Conroe была очень простой; Intel сконцентрировалась на производительности общего L2 Cache, который стал лучшим решением для архитектуры, нацеленной, главным образом, на двуядерные конфигурации. Но в случае с Nehalem инженеры начали с нуля и пришли к такому же заключению, что и конкуренты: общий L2 Cache не очень хорошо подходит для "родной" четырёхъядерной архитектуры. Разные ядра могут слишком часто "вымывать" данные, необходимые другим ядрам, что приведёт к слишком многим проблемам с внутренними шинами и арбитражем, пытаясь обеспечить все четыре ядра достаточной пропускной способностью с сохранением задержек на достаточно низком уровне. Чтобы решить эти проблемы, инженеры оснастили каждое ядро собственным L2 Cache. Поскольку он относительно мал (256 КБ), получилось обеспечить Cache очень высокой производительностью; в частности, задержки существенно улучшились по сравнению с Penryn – с 15 тактов до, примерно, 10 тактов. Объем L1 Cache составляет 64 КБ: по 32 КБ для инструкций и данных.

|

Трёхуровневая иерархия Cache |

Затем есть огромная Cache–память третьего уровня (8 МБ), отвечающая за связь между ядрами. Архитектура Cache Nehalem – инклюзивная для всех нижних уровней иерархии Cache. Это означает, что если ядро попытается получить доступ к данным, и они отсутствуют в L3 Cache, то нет необходимости искать данные в собственных Cache других ядер – там их нет. Напротив, если данные присутствуют, четыре бита, связанные с каждой строчкой Cache–памяти (один бит на ядро) показывают, могут ли данные потенциально присутствовать (потенциально, но без гарантии) в нижнем Cache другого ядра, и если да, то в каком. Чем выше загрузка L3 Cache, тем эффективнее проявляет себя Core i7 в мультипоточных приложениях.

Эта техника весьма эффективна для обеспечения когерентности персональных Cache каждого ядра, поскольку она уменьшает потребность в обмене информацией между ядрами. Есть, конечно, недостаток в виде потери части Cache-памяти на данные, присутствующие в Cache других уровней. Впрочем, не всё так страшно, поскольку L1 и L2 Cache относительно небольшие по сравнению с L3 Cache – все данные L1 и L2 Cache занимают, максимум, 1,25 Мбайт в L3 Cache из доступных 8 Мбайт. Как и в случае Barcelona, L3 Cache работает на других частотах по сравнению с самим чипом. Следовательно, задержка доступа на данном уровне может меняться, но она должна составлять около 40 тактов.

|

Организация Cache–памяти |

Единственные разочарования в новой иерархии Cache Nehalem связаны с L1 Cache. Пропускная способность Cache инструкций не была увеличена – по-прежнему 16 байт на такт по сравнению с 32 у Barcelona. Это может создать "узкое место" в серверно-ориентированной архитектуре, поскольку 64-битные инструкции крупнее, чем 32-битные, тем более что у Nehalem на один декодер больше, чем у Barcelona, что сильнее нагружает Cache. Что касается Cache данных, его задержка была увеличена до четырёх тактов по сравнению с тремя у Conroe, облегчая работу на высоких тактовых частотах. Но инженеры Intel увеличили число промахов L1Cache данных, которые архитектура может обрабатывать параллельно.