- •Раздел 1 Основы теории операционных систем

- •Раздел 2 Машинно-зависимые свойства операционный систем

- •Раздел 3 Машинно-независимые свойства операционных систем

- •Раздел 1 основы теории ос

- •Общие сведения об операционных системах

- •Архитектура ос

- •Распределенная обработка в сетевых ос

- •Сетевые службы.

- •Раздел 2 машинно – зависимые компоненты ос

- •Архитектурные особенности модели микропроцессорной системы

- •Обработка прерываний

- •Планирование процессов

- •Обслуживание ввода-вывода

- •Управление реальной памятью

- •Управление виртуальной памятью

- •Раздел 3 машинно-независимые свойства операционных систем

- •Работа с файлами

- •Планирование заданий

- •Синхронизация процессов и потоков

- •Защищённость и отказоустойчивость ос

Раздел 2 машинно – зависимые компоненты ос

Архитектурные особенности модели микропроцессорной системы

Упрощенная архитектура упрощенной микро-ЭВМ

Джон фон Нейман, Физик, математик, пришел к мысли, что программа должна быть представлена в памяти ЭВМ в цифровой форме, как и данные. Десятичная арифметика, которая использовалась ранее в ЭВМ на основе электронных ламп, была заменена двоичной. Его ЭВМ была первой машиной программой в памяти и даже сейчас является основой большинства современных ПК.

Память

ввод

Арифметико-логическое устройство

Блок

управления

вывод

Аккумулятор

Рисунок 2.1 – Основной состав ЭВМ.

ЭВМ состоит из 5 основных частей, показанных на рисунке 2.1:

память;

АЛУ;

устройство управления;

устройство ввода;

устройство вывода.

Внутри АЛУ находится особый внутренний регистр в 40 битов – аккумулятор. Типичная команда добавила слово из памяти в аккумулятор и сохранила содержимое аккумулятора в памяти. ЭВМ не выполняла операций с плавающей точкой, так как фон Нейман понимал, что любой ведущий математик был способен держать плавающую точку в голове.

Структура оперативной памяти

Для идентификации переменных и команд на разных этапах жизненного цикла программы используется:

символьные имена (метки) – присваивает пользователь при написании программы на алгоритмическом языке или ассемблере;

виртуальные адреса (математические или логические адреса) - вырабатывает транслятор переводящий программу на машинный язык; так как во время трансляции в общем случае неизвестно, в какое место в ОП будет загружено программа, то транслятор присваивает переменным и командам виртуальные (условные) адреса, обычно считая по умолчанию, что начальным адресом программы будет нулевой адрес;

физические адреса – соответствуют номерам ячеек ОП, где в действительности расположены переменные и команды.

Совокупность виртуальных адресов процесса – виртуальное адресное пространство (ВАП). Диапазон возможных адресов виртуального пространства у всех процессов является одном и тем же. Например, при использовании 32-разрядных адресов этот диапазон задается границами 0000000016 и FFFFFFFF16 . Тем не менее, каждый процесс имеет собственное виртуальное пространство - транслятор присваивает виртуальные адреса переменным и кодам каждой программе независимо. Совпадение виртуальных адресов переменных и команд различных процессов не проводит к конфликтам, так как ОС отображает их на различные физические адреса. В том случае, когда необходимо, что бы несколько процессов разделяли общие данные или коды, ОС отображает соответствующие участки виртуального адресного пространства этих процессов на один тот же участок физической памяти.

В разных ОС используются разные способы структуризации ВАП. В одних ОС виртуальное адресное пространство подобно физической памяти представлена в виде непрерывной линейной последовательности виртуальных адресов. Такую структуру называют плоской (flat). При этом виртуальным адресом является единственное число, представляющее смещение относительно начала (000…000) ВАП. Адрес такого типа называется линейным виртуальным адресом.

В других ОС ВАП делится на части - сегменты. В этом случае помимо линейного адреса может быть использован виртуальный адрес, представляющий собой пару чисел (n, m), где n – определенный сегмент, а m – смещение виртуального сегмента.

Существуют и более сложные способы структуризации ВАП, когда виртуальные адреса образуются тремя или более числам.

Адресация

Способы адресации:

непосредственная адресация – операнд содержится в адресной части команды, SO он автоматически вызывается из памяти одновременно с командой, не требуя дополнительного обращения к памяти, но таким способом можно работать только с константами, число значений ограничено размером поля:

MOV R1, # 4 (непосредственный адрес для второго операнда) – загрузить в регистр R1 константу 4;

прямая адресация – дается полный адрес операнда, команда имеет доступ только к одному и тому же адресу памяти, то есть значение может меняться, а адрес – нет, используется только для доступа к глобальным переменным, адреса которых известны во время компиляции.

MOV 00А01070, ≠ 4 – загрузить в ячейку памяти с указанием адреса константы 4;

регистровая адресация – схожа с прямой адресацией только вместо ячейки памяти определяется регистр, является самым распространенным

MOV R1, # 4 – регистровая адресация для первого операнда;

косвенная регистровая адресация – операнд берется из памяти или отправляется в память, но адрес содержится в регистре, может обращаться к памяти , не имея в команде полного адреса

АДД R1, (R2) – второй операнд из памяти, адрес ячейки содержится в регистре R2;

индексная адресация – обращение к памяти по регистру и константе смещения. Возможен и другой способ: указатель адреса ячейки памяти содержится в команде, смещение – в регистре.

MOV R4, А (R2) – для второго операнда используется индексная адресация,

А – смещение, R2 – регистр, если А=124300, в регистре R4 загружается слово, которое находится в регистре R2 со смещением 124300 (от 0);

относительная адресная адресация – адрес вычисляется путем суммирования значений 2-х регистров и смещения, один из регистров – база, другой – индекс. В регистр R5 помещается адрес некоторого элемента, смещение факультативно;

стековая адресация – команда не содержит адреса, возможно при наличии стека.

Основные регистры

В организации вычислительного процесса важную роль играют регистры процессора, которые делятся на несколько групп:

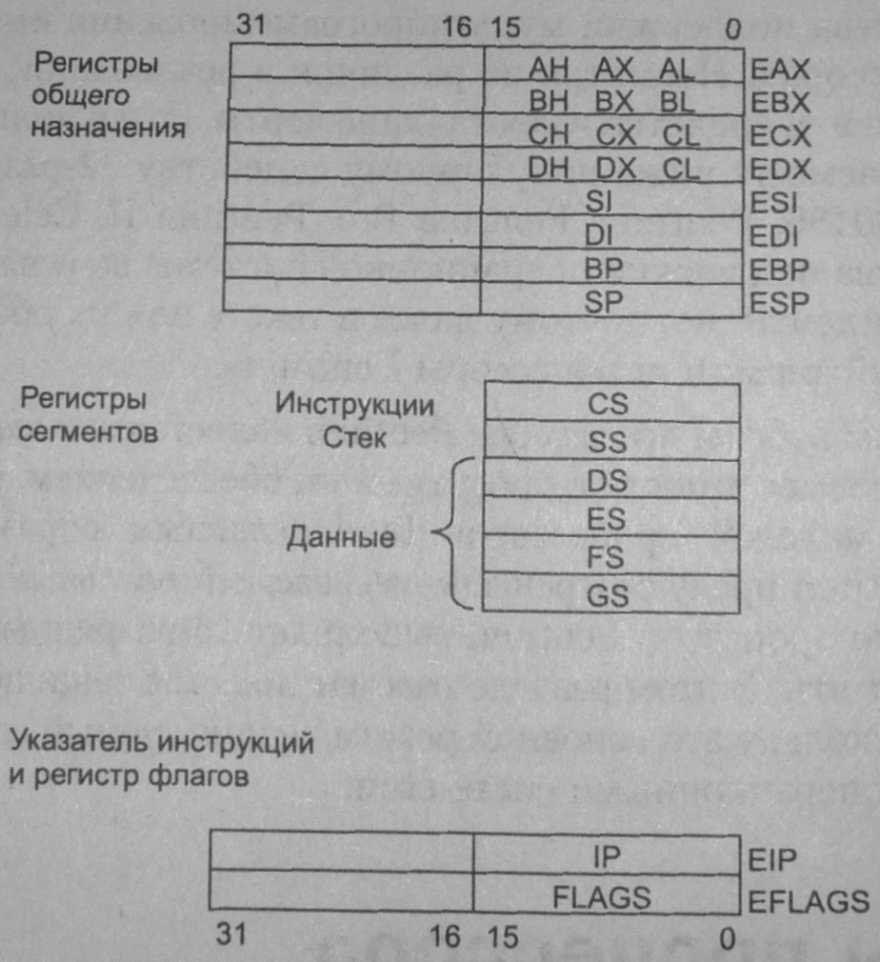

регистры общего назначения. В процессоре Pentium имеется восемь 32-разрядных регистров общего назначения. Четыре из них (А, В, С и D) используются для временного хранения операндов арифметических, логических и другие команд. Программист может обращаться к этим регистрам как к единому целому, используя обозначения ЕАХ, ЕВХ, ЕСХ, EDX, а также к некоторым их частям, как это показано на рисунке 2.2. Здесь обозначение AL (L — Low) относится к первому, самому младшему байту регистра ЕАХ, АН (Н — High) — к следующему по старшинству байту, а АХ обозначает оба младших байта регистра. Остальные четыре регистра общего назначения (ESI, EDI, ЕВР и ESP) предназначены для задания смещения адреса относительно начала некоторого сегмента данных. Эти регистры используются совместно с регистрами сегментов в системе адресации для задания виртуального адреса, который затем с помощью таблиц страниц отображается на физический адрес.

Рисунок 2.2 – основные регистры.

регистры сегментов CS, SS, DS, ES, FS и GS в защищенном режиме ссылаются на дескрипторы сегментов памяти — описатели, в которых содержатся такие параметры сегментов, как базовый адрес, размер сегмента, атрибуты защиты и некоторые другие. Регистры сегментов хранят 16-разрядное число, называемое селектором, в котором 12 старших разрядов представляют собой индекс в таблице дескрипторов сегментов, 1 разряд указывает, в какой из двух таблиц, GDT или LDT, находится дескриптор, а три разряда поля RPL хранят значение уровня привилегий запроса к данному сегменту. Регистр CS (Code Segment) предназначен для хранения индекса дескриптора кодового сегмента, регистр SS (Stack Segment) — дескриптора сегмента стека, а остальные регистры используются для указания на дескрипторы сегментов данных. Все регистры сегментов, кроме CS, программно доступны. Значение регистра CS изменяется при выполнении команд межсегментных вызовов CALL и переходов JMP, а также при переключении задач;

указатель инструкций EIP содержит смещение адреса текущей инструкции, которое используется совместно с регистром CS для получения соответствующего виртуального адреса;

регистр флагов EFLAGS содержит признаки, характеризующие результат выполнения операции, например флаг знака, флаг нуля, флаг переполнения, флаг паритета, флаг переноса и некоторые другие. Здесь хранятся некоторые признаки, устанавливаемые и анализируемые механизмом прерываний, в частности флаг разрешения аппаратных прерываний IF.

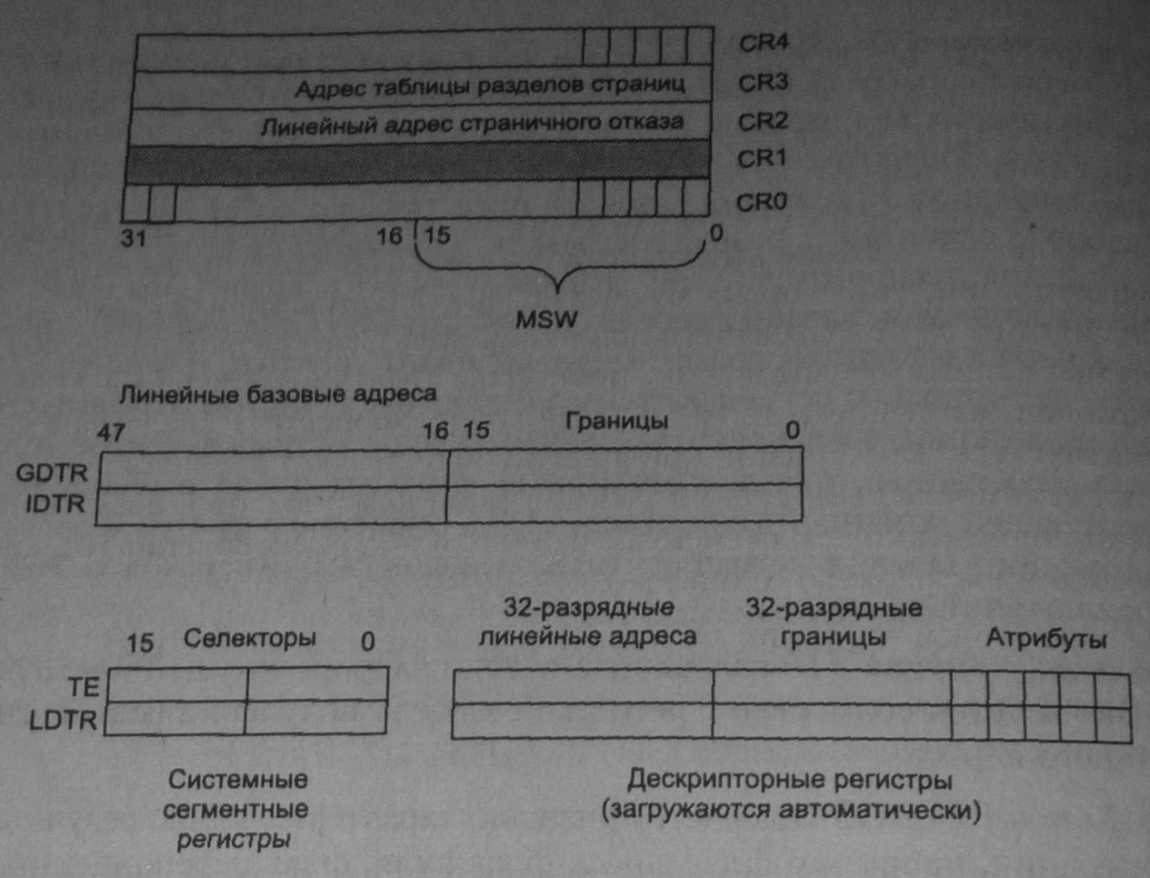

управляющие регистры - CRO, CR1, CR2, CR3 и CR4 - показаны на рисунке 2.3. Регистр CR0 содержит все основные признаки, существенно влияющие на работу процессора, такие как реальный/защищенный режим работы, включение/ выключение страничного механизма системы виртуальной памяти, а также признаки, влияющие на работу кэша и выполнение команд с плавающей точкой. Младшие два байта регистра CR0 имеют название Mashine State Word, MSW — «слово состояния машины». Регистр CR1 в настоящее время не используется (зарезервирован). Регистры CR2 и CR3 предназначены для поддержки работы системы виртуальной памяти. Регистр CR2 содержит линейный виртуальный адрес, который вызвал так называемый страничный отказ. Регистр CR3 содержит физический адрес таблицы разделов, используемой страничным механизмом процессора;

Рисунок 2.3 – Управляющее и системные регистры.

регистры системных адресов содержат адреса важных системных таблиц и структур, используемых при управлении процессами и памятью. Регистр GDTR (Global Descriptor Table Register) содержит физический 32-разрядный адрес глобальной таблицы дескрипторов GDT сегментов памяти, образующих общую часть виртуального адресного пространства всех процессов. Регистр IDTR (Interrupt Descriptor Table Register) хранит физический 32-разрядный адрес таблицы дескрипторов прерываний IDT, используемой для вызова процедур обработки прерываний в защищенном режиме работы процессора. Кроме этих адресов в регистрах GDTR и IDTR хранятся 16-битные лимиты, задающие ограничения на размер соответствующих таблиц. Два 16-битных регистра хранят не физические адреса системных структур, а значения индексов дескрипторов этих структур в таблице GDT, что позволяет кос-, венно получить соответствующие физические адреса. Регистр TR (Task Register) содержит индекс дескриптора сегмента состояния задачи TSS. Регистр LDTR (Local Descriptor Table Register) содержит индекс дескриптора сегмента локаль-^ ной таблицы дескрипторов LDT сегментов памяти, образующих индивидуальную часть виртуального адресного пространства процесса;

регистры отладки и тестирования, а так же регистры математического сопроцессора, выполняющие операции с плавающей точкой хранят значения точек останова, а регистры тестирования позволяют проверить корректность работы внутренних блоков процессора.

Форматы данных и команд

Типы данных:

числовые:

целые числа разной длинны, например, 8,16,32,64 бита. Могут быть со знаком и без знака (знаковый бит);

числа с плавающей точкой (действительные), их длина 32, 64 и 128 бит;

нечисловые:

символьные – код ASCII (7-битные символы), UNICОD (16-битные);

строка символов;

логические (булевы) – истина, ложь;

указатели – машинные адреса.

Команды состоят из кода операции некоторой дополнительной функции (откуда поступают операнды, куда должны отправляться результаты):

безадресная команда:

код команды

одноадресная команда:

код адрес

двухадресная команда:

код адрес1 адрес2

3-х адресная команда:

код адрес1 адрес2

адрес3