2.3. Сумматоры

Сумматор представляет собой логический операционный узел, выполняющий арифметическое сложение кодов двух чисел в цифровых устройствах.

При арифметическом сложении выполняются различные дополнительные операции: учет знаков чисел, выравнивание порядков слагаемых и т. д.

Сумматоры квалифицируют по различным признакам, например по числу входов и выходов.

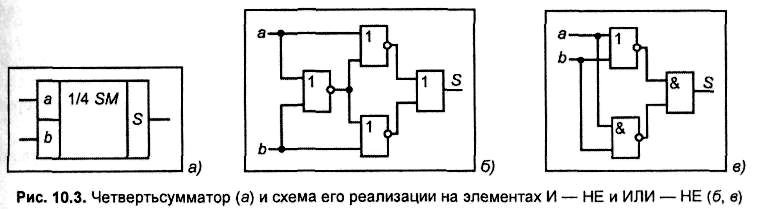

На рис. 10.3 показан четвертьсумматор с двумя входами для двух одноразрядных чисел и одним выходом, на котором реализуется их сумма.

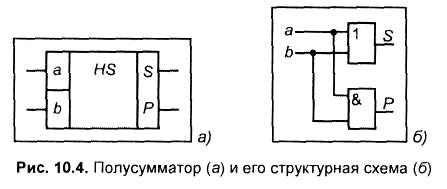

На рис. 10.4, а показан полусумматор с двумя входами, на которые подаются одноименные разряды двух чисел, и двумя выходами, на одном из которых реализуется арифметическая сумма, а на другом — перенос в следующий более старший разряд. Обозначением полусумматора служат буквы HS (halfsum — полусумма).

Полусумматор может быть реализован на элементе исключающих ИЛИ и одном двухвходовом вентиле И (рис. 10.4, б).

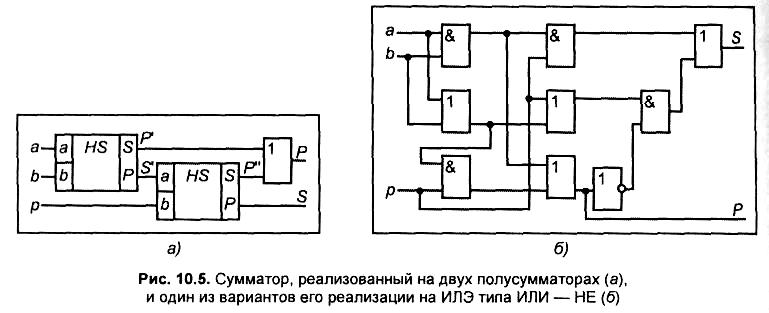

Полные одноразрядные сумматоры характеризуются наличием трех входов, на которые подаются одномерные разряды двух складываемых чисел и перенос из предыдущего бо-

лее младшего разряда, и двумя выходами, на одном из которых реализуется арифметическая сумма в данном разряде, а на другом — перенос в более старший разряд.

Схема полного сумматора, реализованного на двух полусумматорах, показана на рис. 10.5, а.

Сумматор на схемах обозначается SM. На входы а и b сумматора подаются два слагаемых, на вход р— перенос из предыдущего несущего разряда. Выходы обеспечивают суммирование по каналу S и перенос в старший разряд по каналу Р.

Особенностью выходных сигналов полного двоичного сумматора является их самодвойственность как функций алгебры логики. Другими словами, выходные сигналы S и Р способны инвертировать свое значение при инвертировании всех переменных, от которых они зависят.

Полные сумматоры совместно с инверторами используются для проведения операций вычитания. Сумматоры и вычитатели реализованы в виде интегральных схем.

2.4. Шифраторы и дешифраторы

Шифратором в вычислительной технике называют комбинационный узел, предназначенный для преобразования одного из совокупности входных функционально однотипных однопозиционных кодов в двоичный код.

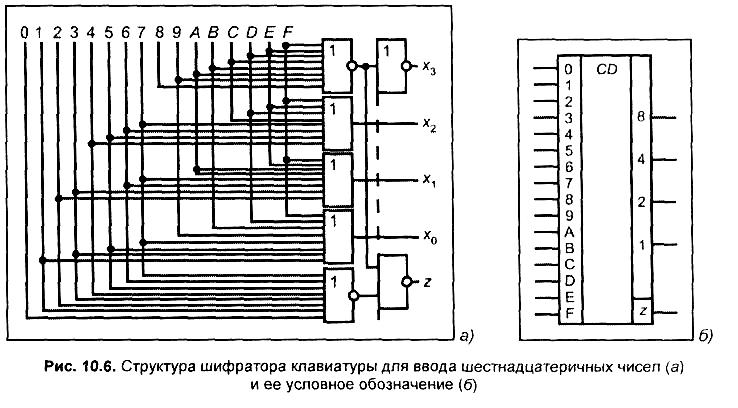

Одним из аппаратных средств для ввода данных в цифровую систему является клавиатура, которая переводит десятичные цифры в код. На рис. 10.6 приведена структура шифратора клавиатуры, выполненная на логических элементах.

Клавиатура предназначена для ввода шестнадцатеричных чисел. Переменные 4-разрядного двоичного кода с весами соответственно 8, 4, 2, 1 обозначены переменными хъ, х2, хи % Осведомительный сигнал Z принимает значение 1 при нажатии клавиши и значение О при всех нажатых клавишах. Этот сигнал называется сигнал-универсум,

Шестнадцатеричные цифры состоят из десятичного числа от 0 до 9 и шести цифр, обозначенных большими латинскими буквами А, В, С, D, E, F. Схема шифратора состоит из шести логических ячеек типа ИЛИ — НЕ и одной типа И — НЕ. Интегральная схема может быть обозначена буквами CD (coder). Приведенный тип шифратора предназначен для обработки зависимых однопозиционных сигналов. Это означает, что из всех клавиш может быть нажата только одна. Такие шифраторы называются приоритетными. При большом числе кнопок на клавиатуре код каждой клавиши поддерживается или программным сканированием столбцов и строк, или специализированным контроллером.

Дешифратором в цифровой технике называют комбинационный узел, преобразующий n-разрядный двоичный код в однопозиционный или в совокупность однопозиционных кодов. Примерами однопозиционных кодов могут быть адрес ячейки памяти, однозначный сигнал установки счетчика в нулевое состояние и т. д.

Двоичный n-разрядный код имеет 2" наборов и столько же однопозиционных кодов. Дешифраторы, как и шифраторы, выполняются в виде интегральных схем.

Полным дешифратором называется дешифратор, имеющий N = 2" выходов, если N < 2", то — неполным.

На рис. 10.7 приведены структурные схемы полного дешифратора, преобразующего двухразрядный двоичный код в однопозиционный.

Переменные дешифруемого двухразрядного двоичного кода обозначены х0 и х,, однопозиционный выход дешифратора обозначен как J0. Однопозиционный выход дешифратора, вырабатывает активный сигнал 0 или 1. Выходные сигналы Ju J2, Jj определяются функцией алгебры логики и зависят от переменных х0 и х{. Условное обозначение дешифратора приведено на рис. 10.7, в. Цифры 2 и 1 слева обозначают двоичные веса разрядов дешифрируемого двоичного кода, а кружки справа свидетельствуют о том, что активными сигналами выхода являются уровни 0 положительной логики. Их отсутствие свидетельствует о том, что активными сигналами

выхода являются 1. На интегральных схемах дешифратора маркируются буквы DC — decoder.