- •1. Стислі теоретичні відомості

- •2. Генератор імпульсів г5-54

- •3.1. Технічні дані осцилографа с1-55

- •3.2. Принцип дії приладу осцилографа с1-55

- •3.3. Органи управління та регулювання осцилографа

- •3.4. Вимір часових інтервалів

- •3.6. Вимір амплітуди досліджуваних сигналів

- •4. Порядок виконання роботи

- •6. Контрольні завдання та запитання

- •2. Порядок виконання роботи

- •4. Контрольні запитання та завдання

- •1. Стислі теоретичні відомості

- •2. Порядок виконання роботи

- •4. Контрольні запитання та завдання

- •В статичному режимі та в режимі підсилення

- •1. Стислі теоретичні відомості

- •2. Порядок виконання роботи

- •4. Контрольні запитання та завдання

- •Лабораторна робота 5 дослідження часових характеристик та параметрів біполярних транзисторів

- •1. Стислі теоретичні відомості

- •2. Порядок виконання роботи

- •2. Порядок виконання роботи

- •4. Контрольні запитання та завдання

- •Дослідження статичних характеристик

- •1. Стислі теоретичні відомості

- •2. Порядок виконання роботи

- •4. Контрольні запитання та завдання

- •Цифрових інтегральних мікросхем

- •1. Стислі теоретичні відомості

- •2. Порядок виконання роботи

- •4. Контрольні запитання та завдання

- •Список літератури

- •Лабораторні роботи 1–8

4. Контрольні запитання та завдання

Намалюйте принципову схему ЦІС, яка досліджується, та поясність реалізацію логічних операцій І – НІ та АБО – НІ.

Поясність особливості ІМС як нового типу електронних приладів.

Перелічіть основні переваги використання цифрових ІМС.

Як класифікують цифрові ІМС?

Перелічіть базові функціональні елементи.

Порівняйте параметри базових електронних ключів на біполярних ЦІС та МОН-структурах.

Перелічіть та дайте визначення основних статичних параметрів ЦІС.

В чому суть методів вимірювання статичних параметрів ЦІС?

Намалюйте передавальну характеристику ЦІС.

Лабораторна робота 8

ДОСЛІДЖЕННЯ ДИНАМІЧНИХ ПАРАМЕТРІВ

Цифрових інтегральних мікросхем

Мета роботи: поглиблення та закріплення знань про структуру, принцип дії, особливості та основні динамічні параметри ЦІС, виконаних на КМОП-транзисторах, надбання навичок експериментального визначення основних динамічних параметрів ЦІС типу К561ЛА7.

1. Стислі теоретичні відомості

Властивості інтегральних логічних елементів (ІЛЕ) в режимі перемикання оцінюють за допомогою динамічних параметрів, які визначають за реакцією схеми в часі на дію вхідних сигналів. Це часові співвідношення між вхідними та вихідними сигналами, а також часові діаграми різних режимів роботи ІМС.

До динамічних відносяться наступні параметри (рис. 8.1):

t1,0 (tTLH) – тривалість переходу ІМС зі стану логічної одиниці в стан логічного нуля. Цей інтервал часу, за який напруга на виході ІМС змінюється від рівня лог. 1 до рівня лог. 0, виміряний на рівнях 0,9 та 0,1 або на заданих значеннях напруги;

t0,1 (tTLH) – тривалість переходу ІМС зі стану лог. 0 в стан лог. 1. Це інтервал часу, за який напруга на виході ІМС змінюється від рівня лог. 0 до рівня лог. 1, виміряний на рівнях 0,1 та 0,9 або на заданих значеннях напруги;

t0,1затр.(tDHL) – тривалість затримки увімикнення ІМС. Це інтервал часу між вхідним та вихідним імпульсами при зміні напруги на виході ІМС від напруги лог. 1 до напруги лог. 0, виміряний на рівні 0,1 або на заданих рівнях напруги;

t0,1затр.(tDHL) – тривалість затримки вимикання ІМС. Це інтервал часу між вхідним та вихідним імпульсами при зміні напруги на виході ІМС від рівня лог. 0 до рівня лог. 1;

Рис. 8.1. Динамічні параметри ЦІС

t1,0 затр.пош.(tPHL)– тривалість затримки поширення сигналу при увімкненні ІМС. Це інтервал часу між вхідним та вихідним імпульсами при зміні напруги на виході ІМС від рівня лог. 1 до рівня лог. 0, виміряний на рівні 0,5 або на заданих значеннях напруги;

t0,1затр.пош.(tPLH) – тривалість затримки поширення сигналу при вимиканні ІМС. Це інтервал часу між вхідним та вихідним імпульсами при зміні напруги на виході ІМС від рівня лог. 0 до рівня лог. 1, виміряний на рівні 0,5 або на заданих значеннях напруги;

t0,1затр.пош.с.(tPAV) – середній час затримки поширення сигналу логічної ІМС. Це інтервал часу, який дорівнює напівсумі часу затримки поширення сигналу при вмиканні та часу затримки поширення сигналу при вимкненні логічної ІМС:

![]() .

.

Середній час затримки поширення визначає швидкодію ЦІС. Його значення в наносекундах для різних серій ІМС подано в таблиці 1.

Таблиця 1

Тип логіки |

р-МОН |

КМОН |

ТТЛ |

ЕСТЛ |

n-МОН |

|

tPAV |

100 |

15 – 50 |

1 3 |

0,5 – 2 |

40 – 100 |

5 |

Обмеження за швидкодією, які характерні для р-канальних МОН-схем, ліквідовані за допомогою n-канальних МОН-структур. Рухливість електронів в кремнії більша, ніж рухливість дірок, що забезпечує швидкість перемикання МОН-схем з n-канальним в 2-3 рази більшу, ніж схем з р-каналом. Використання методу іонної імплантації та структур зі збідненими, а не зі збагаченими каналами дозволило знизити напругу живлення до 5 В, що робить ці схеми сумісними за електричними рівнями з ТТЛ.

Ряд важливих позитивних якостей мають елементи інжекційної логіки ІЛ2, які з'явились внаслідок удосконалення технології та схемотехніки ІМС.

Методи вимірювання динамічних параметрів ЦІС основані на визначенні часового інтервалу між двома різними (або однаковими) рівнями напруги вхідних та вихідних сигналів. З цією метою використовують генератор імпульсних сигналів та вимірювач часових інтервалів. В лабораторній роботі для вимірювання інтервалів часу використовують осцилограф.

При вимірюванні динамічних параметрів як навантаження використовують мікросхему та її еквівалент.

В логічних

схемах використовують МДН-транзистори

з окисним діелектриком

![]() – МОН-транзистори. В основі

МОН-транзисторної логіки (МОП ТЛ) лежать

МОП-транзисторні ключі-інвертори. В

ключах з динамічним навантаженням

використовують транзистори з каналом

того ж типу, як і в активних транзисторах.

Це ДМОН-транзисторна логіка на ключах

одного типу провідності.

– МОН-транзистори. В основі

МОН-транзисторної логіки (МОП ТЛ) лежать

МОП-транзисторні ключі-інвертори. В

ключах з динамічним навантаженням

використовують транзистори з каналом

того ж типу, як і в активних транзисторах.

Це ДМОН-транзисторна логіка на ключах

одного типу провідності.

На транзисторах з каналами протилежного типу провідності виконуються комплементарні ключі, які складають основу КМОН логіки або КМОН ТЛ.

Особливістю інтегральних логічних елементів на МОН-транзисторах є відсутність струму у вхідному колі. В результаті логічні рівні UO та U1 не залежать від навантаження та залишаються такими ж, як і при холостому ході. Вплив наступного ключа призводить лише до збільшення вихідної ємності даного логічного елементу.

На рис. 8.2 зображено два типових варіанти ІЛЕ МОН-логіки, виконаних на МОН-транзисторах з n-каналами. Використання динамічного навантаження зменшує площу ІЛЕ та розширює одну з основних переваг МОН ТЛ – високий ступінь інтеграції. Ця перевага зумовлена тим, що МОН-структури не потребують спеціальної ізоляції між ІЛЕ, на відміну від структури на основі біполярних транзисторів.

Транзистори

VТ1

та VТ2

є активними, а транзистори Т3

– динамічним навантаженням. Затвор VТЗ

з'єднаний зі стоком, тому

![]() ,

тобто

,

тобто

![]() –

порогова напруга). Це означає, що VТЗ

працює на пологій ділянці. Якщо на

затвори VТ1

та VТ2

(рис. 8.2, а)

подати напругу

U0вх<U0

транзистор VТ3

переходить у відкритий стан, його

залишкова напруга мала і U1вих=EC.

Якщо на затвор VТ1

або VТ2

подати напругу U1вх

<U0

(або на обидва затвори), транзистор (чи

обидва) переходить у відкритий стан,

залишкова напруга мала і U0вих→0.

Напруга живлення повністю прикладена

до вимкнутого навантажуючого транзистора

VТ3.

Для зменшення залишкової напруги в

ключі з динамічним навантаженням

транзистори VТ1

(VТ2)

та VТ3

повинні суттєво відрізнятися. В активного

транзистора відношення ширини до довжини

каналу повинно бути якомога більшим, а

у навантажуючого – якомога меншим.

–

порогова напруга). Це означає, що VТЗ

працює на пологій ділянці. Якщо на

затвори VТ1

та VТ2

(рис. 8.2, а)

подати напругу

U0вх<U0

транзистор VТ3

переходить у відкритий стан, його

залишкова напруга мала і U1вих=EC.

Якщо на затвор VТ1

або VТ2

подати напругу U1вх

<U0

(або на обидва затвори), транзистор (чи

обидва) переходить у відкритий стан,

залишкова напруга мала і U0вих→0.

Напруга живлення повністю прикладена

до вимкнутого навантажуючого транзистора

VТ3.

Для зменшення залишкової напруги в

ключі з динамічним навантаженням

транзистори VТ1

(VТ2)

та VТ3

повинні суттєво відрізнятися. В активного

транзистора відношення ширини до довжини

каналу повинно бути якомога більшим, а

у навантажуючого – якомога меншим.

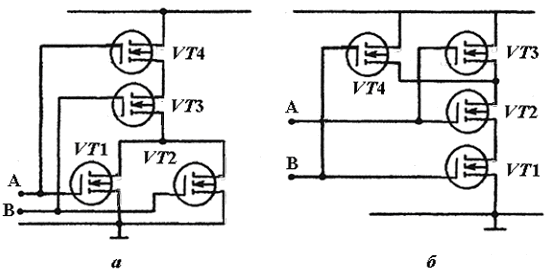

Рис. 8.2. Логічні елементи МОН ТЛ з динамічним навантаженням:

а виконують логічну функцію АБО – НІ;

б виконують логічну функцію І – НІ

Транзистори VТ1 та VТ2 (рис. 8.2, а) ввімкнені паралельно, відпирання кожного з них призводить до зменшення вихідного рівня, тобто схема виконує логічну функцію 2 АБО – НІ. При відміченій вище геометрії транзисторів залишкова напруга має таке ж мале значення (0,05...0,15 В), як і в біполярних ключах. Тому можна вважати U0вих = Uзал = 0,1B.

В схемі МОН ТЛ залишкова напруга зменшується пропорційно кількостей відкритих логічних транзисторів, так як паралельне з'єднання транзисторів рівноважне збільшенню відношення ширини до довжини каналу.

Звичайно

напруга живлення в МОН ТЛ обирається в

3-4 рази більшою ніж порогова напруга.

Тому, якщо

![]() = 1,5...3 В, то логічний перепад (5...10 В)

набагато перевищує значення, властиве

схемам ДТЛ, ТТЛ та ІЛ2.

= 1,5...3 В, то логічний перепад (5...10 В)

набагато перевищує значення, властиве

схемам ДТЛ, ТТЛ та ІЛ2.

Ще однією перевагою МОН ТЛ є підвищена завадостійкість. Для відкривання транзистора необхідна напруга близька до порогової, тобто 1,5...3 В, в той час як у біполярних ІЛЕ вона складає 0,7...1,4 В.

Зображений

на рис 8.2, б

ІЛЕ відрізняється послідовним вмиканням

логічних транзисторів. Тому струм в

колі й низький рівень вихідної напруги

![]() можливі

лише при відкриванні всіх (в даному

випадку обох) логічних транзисторів.

Це має місце при подачі рівня U1вх

на всі логічні входи. Наведена ІЛЕ

виконує функцію 2 І – НІ. Рівень

можливі

лише при відкриванні всіх (в даному

випадку обох) логічних транзисторів.

Це має місце при подачі рівня U1вх

на всі логічні входи. Наведена ІЛЕ

виконує функцію 2 І – НІ. Рівень

![]() в даній схемі такий самий, як і в

попередній, але рівень

в даній схемі такий самий, як і в

попередній, але рівень

![]() більший – він пропорційний кількості

послідовно ввімкнених логічних

транзисторів і може складати 0,2...0,5 В та

більше. Відповідно меншим буде логічний

перепад.

більший – він пропорційний кількості

послідовно ввімкнених логічних

транзисторів і може складати 0,2...0,5 В та

більше. Відповідно меншим буде логічний

перепад.

Швидкодія МОН ТЛ обмежується швидкістю перезарядки ємності СО = ССВ + СЗВ + СМ (паразитна ємність мантажа).Такі ІЛЕ менш швидкодіючі, ніж біполярні.

Логічні елементи на комплементарних ключах показані на рис. 8.3, а і б. Основна перевага КМОН логіки є в тому, що зміна вихідної напруги не пов'язана зі зміною струму стоку: він залишається близьким до нуля. В результаті КМОН логічні елементи споживають дуже малу потужність. В структурах КМОН ТЛ паралельне з'єднання одного типу транзисторів супроводжується послідовним з'єднанням іншого типу. Логічна функція, що виконується, визначається вмиканням транзисторів “нижнього” поверху. Транзистори VТ1 та VТ2 – транзистори з індукованим n-канналом (збагаченого типу), а VТ3 та VТ4 – з індукованим р-каналом.

Якщо в

схемі (рис. 8.3, а)

на обидва логічних входи подані низькі

рівні U0вх

<![]() ,

то VТ1

та VТ2

закриті (канали відсутні). В транзисторах

VТ3

та VТ4

утворюються канали так як напруга

,

то VТ1

та VТ2

закриті (канали відсутні). В транзисторах

VТ3

та VТ4

утворюються канали так як напруга

![]() і перевищує (за модулем) порогову напругу.

Однак, оскільки через канали течуть

незначні струми закритих транзисторів

VТ1

та VТ2,

падіння напруги на каналах транзисторів

VТ3

та VТ4

виходить малим. Тому можна вважати, що

вхідна напруга дорівнює напрузі живлення

U1вих

= EC.

Відповідно логічний перепад складає

і перевищує (за модулем) порогову напругу.

Однак, оскільки через канали течуть

незначні струми закритих транзисторів

VТ1

та VТ2,

падіння напруги на каналах транзисторів

VТ3

та VТ4

виходить малим. Тому можна вважати, що

вхідна напруга дорівнює напрузі живлення

U1вих

= EC.

Відповідно логічний перепад складає

![]() .

.

Рис. 8.3. Логічні елементи КМОН ТЛ:

а виконують логічну функцію АБО – НІ;

б виконують логічну функцію І НІ

Розглянемо

випадок, коли вхідний інформаційний

сигнал U1вх>U0

подається тільки на один вхід А. Це

забезпечить перемикання транзистора

VТ1

у відкритий стан. Слід звернути увагу

на те, що для нормального функціонування

ІЛЕ на основі КМОН-структур, рівень

вхідного сигналу повинен бути таким,

щоб виконувалась умова

![]() .

.

Тоді забезпечується перемикання транзистора VT4 в закритий стан і на виході сформується рівень логічного нуля. Такі ж процеси відбуваються, якщо U1вх подавати тільки на вхід В чи на обидва входи одночасно.

Вихідна напруга ІЛЕ змінюється при подачі рівня U1вх на будь-який із входів (А чи В) або на обидва входи. Такий елемент виконує логічну функцію АБО – НІ.

Стан схеми (рис. 8.3, б) змінюється тільки при подачі рівня U1вх >U0 одночасно на обидва входи. При цьому реалізується логічна функція І НІ.

Крім високої економічності, додатковими перевагами КМОН ТЛ в порівнянні з МОН ТЛ є малі робочі напруги (до 2 та менше) та більш висока швидкодія. Останнє зумовлено тим, що в таких ІЛЕ вихідна ємність заряджається та розряджається струмами відкритих транзисторів.

Література: [1, c. 117–119]; [4, c. 223–230]; [6]; [11]; [12]; [13]; [14].