МІНІСТЕРСТВО ОСВІТИ І НАУКИ, МОЛОДІ ТА СПОРТУ

КИЇВСЬКИЙ НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ БУДІВНИЦТВА ТА АРХІТЕКТУРИ

КАФЕДРА ІНФОРМАЦІЙНИХ ТЕХНОЛОГІЙ

Курсова робота

з дисципліни

«Комп’ютерна схемотехніка»

Роботу виконала:

студентка групи ПНК-21

Троц Ю.М.

Роботу перевірив:

доц. Щербина О.А.

2011.

Описати на VHDL та здійснити моделювання роботи елементів І-НЕ з двома і трьома входами і затримкою формування сигналу, що дорівнює 15 нс.

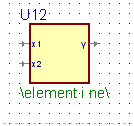

Елемент І-НЕ з двома входами.

Код на мові VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity \element i ne\ is

port(

x1 : in STD_LOGIC;

x2 : in STD_LOGIC;

y : out STD_LOGIC

);

end \element i ne\;

--}} End of automatically maintained section

architecture \element i ne\ of \element i ne\ is

begin

y<= not ( x1 and x2) after 15 ns;

end \element i ne\;

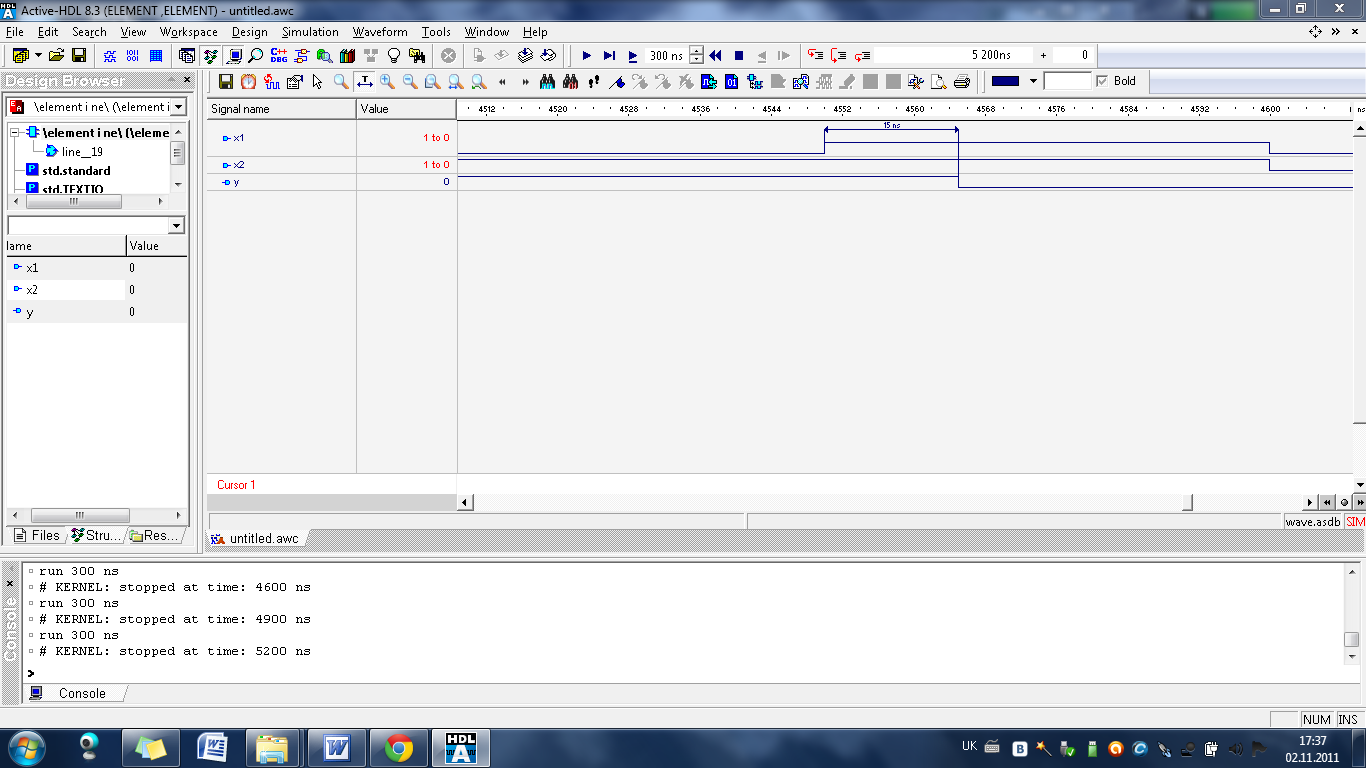

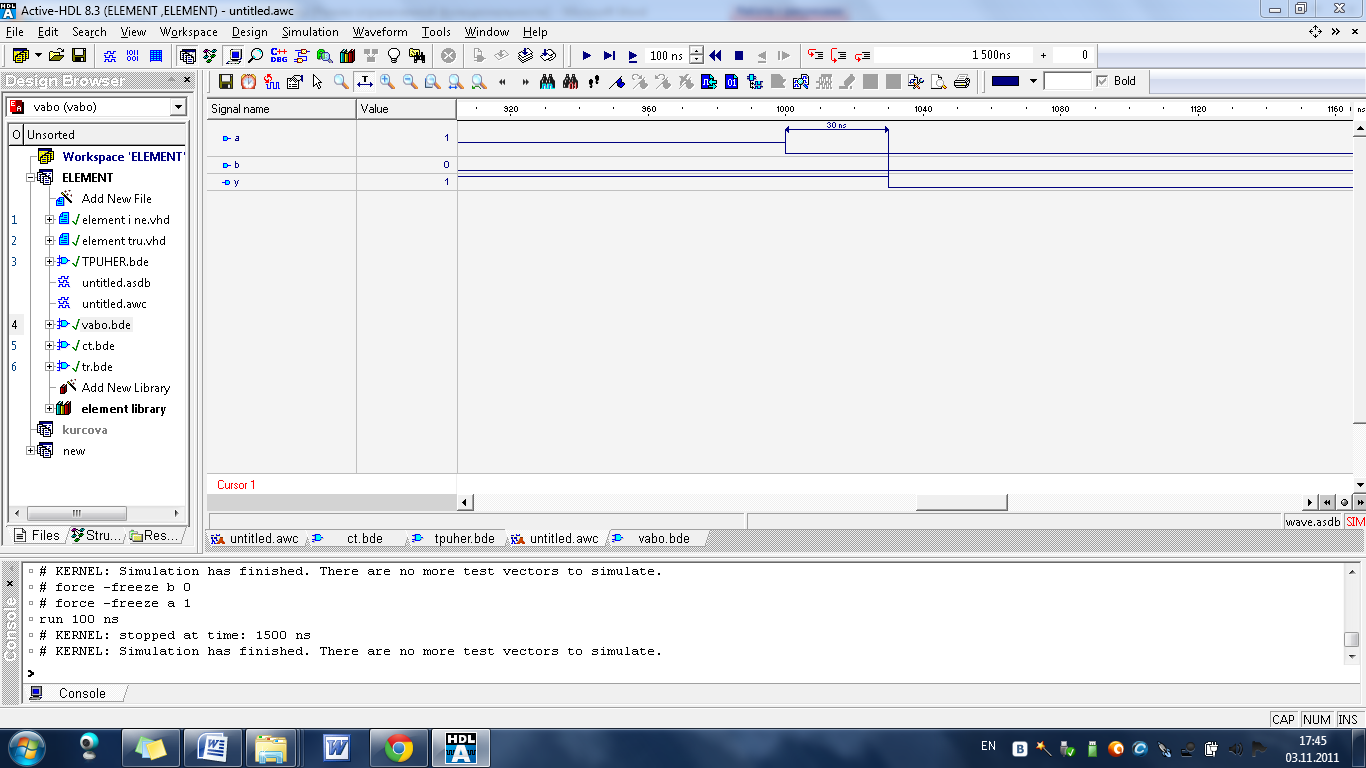

Часова діаграма:

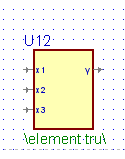

Елемент 3І-НЕ з трьома входами.

Код на мові VHDL:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity \element tru\ is

port(

X1 : in std_logic;

x2 : in STD_LOGIC;

x3 : in STD_LOGIC;

y : out STD_LOGIC

);

end \element tru\;

--}} End of automatically maintained section

architecture \element tru\ of \element tru\ is

begin

y<= not (x1 and x2 and x3) after 15 ns;

end \element tru\;

Часова діаграма:

Затримка сигналу складає 15 нс.

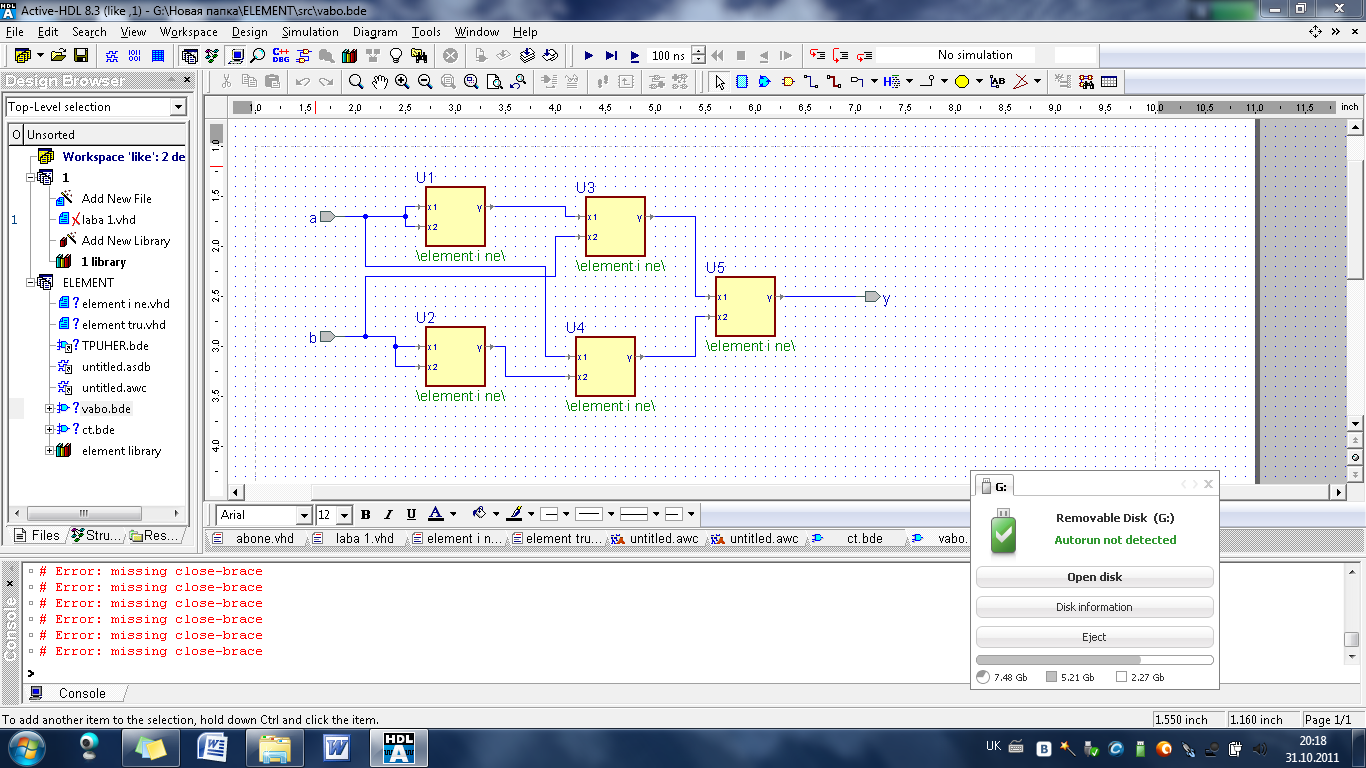

Елемент виключаюче АБО.

Код на мові VHDL:

-------------------------------------------------------------------------------

--

-- Title : vabo

-- Design : ELEMENT

-- Author : Unknown

-- Company : Unknown

--

-------------------------------------------------------------------------------

--

-- File : c:\STUD\My_Designs\TROTS\ELEMENT\compile\vabo.vhd

-- Generated : Fri Oct 28 17:30:56 2011

-- From : c:\STUD\My_Designs\TROTS\ELEMENT\src\vabo.bde

-- By : Bde2Vhdl ver. 2.6

--

-------------------------------------------------------------------------------

--

-- Description :

--

-------------------------------------------------------------------------------

-- Design unit header --

library IEEE;

use IEEE.std_logic_1164.all;

entity vabo is

port(

a : in STD_LOGIC;

b : in STD_LOGIC;

y : out STD_LOGIC

);

end vabo;

architecture vabo of vabo is

---- Component declarations -----

component \element i ne\

port (

X1 : in std_logic;

X2 : in std_logic;

y : out STD_LOGIC

);

end component;

---- Signal declarations used on the diagram ----

signal NET102 : STD_LOGIC;

signal NET195 : STD_LOGIC;

signal NET217 : STD_LOGIC;

signal NET78 : STD_LOGIC;

begin

---- Component instantiations ----

U1 : \element i ne\

port map(

x1 => a,

x2 => a,

y => NET78

);

U2 : \element i ne\

port map(

x1 => b,

x2 => b,

y => NET195

);

U3 : \element i ne\

port map(

x1 => NET78,

x2 => b,

y => NET102

);

U4 : \element i ne\

port map(

x1 => a,

x2 => NET195,

y => NET217

);

U5 : \element i ne\

port map(

x1 => NET102,

x2 => NET217,

y => y

);

end vabo;

![]()

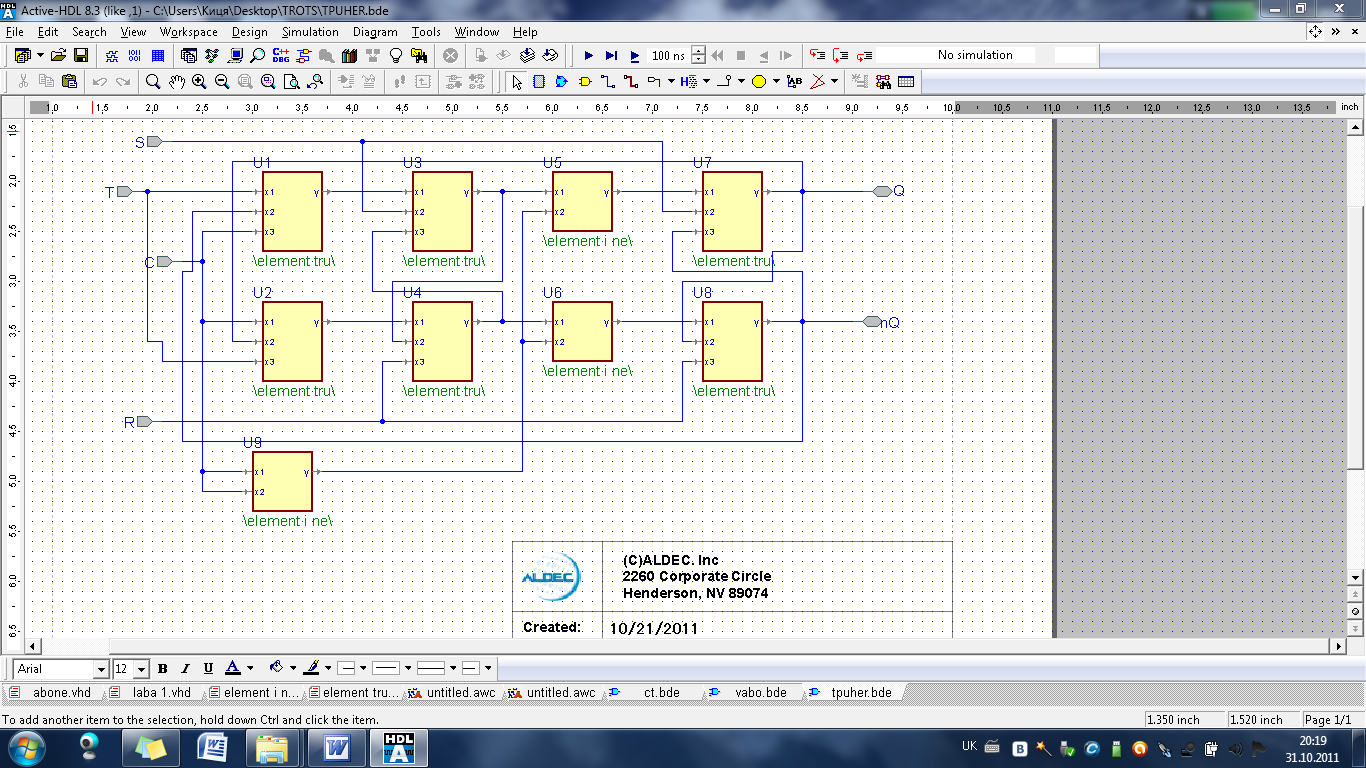

Т-тригер з асинхронними RS входами.

Побудувати

з цих елементів Т-тригер, що має інверсний

динамічний вхід синхронізації С та

асинхронні входами R і S. Пересвідчитись

у правильній роботі тригера, виконавши

моделювання, та виміряти час інвертування

стану тригера( тобто затримки між зміною

сигналу на вході С і встановленням

відповідних значень сигналів на виходах

Q i nQ). Зробити загальний висновок про

затримки у тригері, якщо затримка у

логічному елементі І-НЕ дорівнює

![]() .

.

Код на мові VHDL:

--

-- Title : TPUHER

-- Design : ELEMENT

-- Author : Unknown

-- Company : Unknown

--

-------------------------------------------------------------------------------

--

-- File : c:\STUD\My_Designs\TROTS\ELEMENT\compile\TPUHER.vhd

-- Generated : Fri Oct 21 16:45:28 2011

-- From : c:\STUD\My_Designs\TROTS\ELEMENT\src\TPUHER.bde

-- By : Bde2Vhdl ver. 2.6

--

-------------------------------------------------------------------------------

--

-- Description :

--

-------------------------------------------------------------------------------

-- Design unit header --

library IEEE;

use IEEE.std_logic_1164.all;

entity TPUHER is

port(

C : in STD_LOGIC;

R : in STD_LOGIC;

S : in STD_LOGIC;

T : in STD_LOGIC;

Q : inout STD_LOGIC;

nQ : inout STD_LOGIC

);

end TPUHER;

architecture TPUHER of TPUHER is

---- Component declarations -----

component \element i ne\

port (

x1 : in STD_LOGIC;

x2 : in STD_LOGIC;

y : out STD_LOGIC

);

end component;

component \element tru\

port (

x1 : in STD_LOGIC;

x2 : in STD_LOGIC;

x3 : in STD_LOGIC;

y : out STD_LOGIC

);

end component;

---- Signal declarations used on the diagram ----

signal NET152 : STD_LOGIC;

signal NET166 : STD_LOGIC;

signal NET184 : STD_LOGIC;

signal NET188 : STD_LOGIC;

signal NET213 : STD_LOGIC;

signal NET227 : STD_LOGIC;

signal NET262 : STD_LOGIC;

begin

---- Component instantiations ----

U1 : \element tru\

port map(

x1 => T,

x2 => nQ,

x3 => C,

y => NET152

);

U2 : \element tru\

port map(

x1 => C,

x2 => Q,

x3 => T,

y => NET166

);

U3 : \element tru\

port map(

x1 => NET152,

x2 => S,

x3 => NET227,

y => NET213

);

Часова діаграма:

При

переході

![]() затримка в 45 ns,

тобто з

,

тобто

затримка в 45 ns,

тобто з

,

тобто

![]() ,

а при переході з

,

а при переході з

![]() затримка в тригері 60 ns,

тобто 4τ, тобто,

затримка в тригері 60 ns,

тобто 4τ, тобто,

![]() .

.

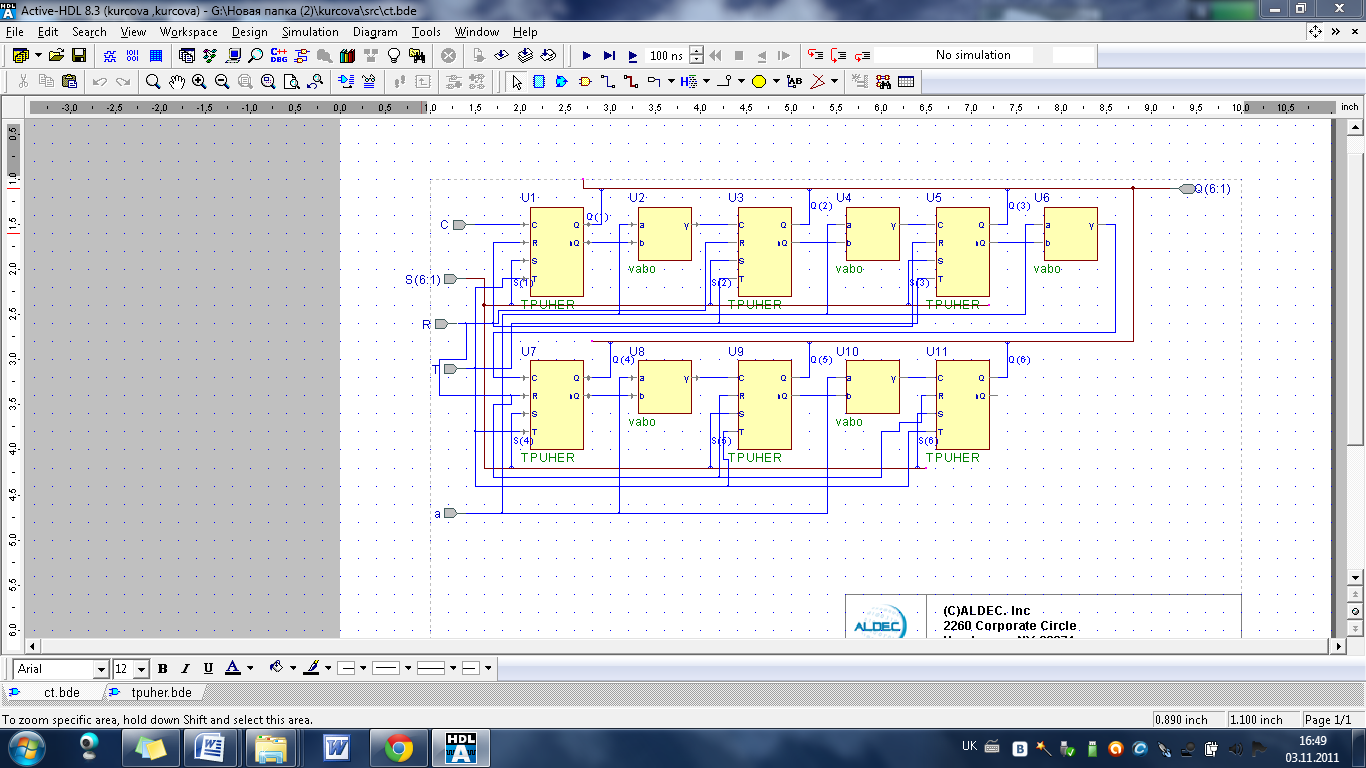

6- розрядний реверсивний лічильник, з послідовним переносом.

Побудувати на цих тригерах та елементах І-НЕ з довільною потрібною вам кількістю входів 6- розрядний лічильник з послідовним переносом. Асинхронні входи тригерів R об’єднайте і використайте для встановлення в лічильнику початкового нульового значення, а входи S використайте для запису в лічильник довільного числа паралельним кодом. Пересвідчіться у правильній роботі схеми лічильника, виконавши моделювання в усіх режимах, та виміряйте час найдовшого перехідного процесу у цьому лічильнику. Узагальніть отриманий результат на випадок довільної розрядності лічильника n, виразивши цей час у вигляді формули, що залежить від затримки τ і розрядності.

Код на мові VHDL:

-------------------------------------------------------------------------------

--

-- Title : ct

-- Design : ELEMENT

-- Author : Unknown

-- Company : Unknown

--

-------------------------------------------------------------------------------

--

-- File : C:\STUD\My_Designs\TROTS\ELEMENT\compile\ct.vhd

-- Generated : Fri Oct 28 17:27:00 2011

-- From : C:\STUD\My_Designs\TROTS\ELEMENT\src\ct.bde

-- By : Bde2Vhdl ver. 2.6

--

-------------------------------------------------------------------------------

--

-- Description :

--

-------------------------------------------------------------------------------

-- Design unit header --

library IEEE;

use IEEE.std_logic_1164.all;

entity ct is

port(

C : in STD_LOGIC;

R : in STD_LOGIC;

T : in STD_LOGIC;

a : in STD_LOGIC;

S : in STD_LOGIC_VECTOR(6 downto 1);

Q : inout STD_LOGIC_VECTOR(6 downto 1)

);

end ct;

architecture ct of ct is

---- Component declarations -----

component TPUHER

port (

C : in STD_LOGIC;

R : in STD_LOGIC;

S : in STD_LOGIC;

T : in STD_LOGIC;

Q : inout STD_LOGIC;

nQ : inout STD_LOGIC

);

end component;

component vabo

port (

a : in STD_LOGIC;

b : in STD_LOGIC;

y : out STD_LOGIC

);

end component;

---- Signal declarations used on the diagram ----

signal NET133 : STD_LOGIC;

signal NET138 : STD_LOGIC;

signal NET143 : STD_LOGIC;

signal NET148 : STD_LOGIC;

signal NET209 : STD_LOGIC;

signal NET302 : STD_LOGIC;

signal NET307 : STD_LOGIC;

signal NET312 : STD_LOGIC;

signal NET317 : STD_LOGIC;

signal NET405 : STD_LOGIC;

signal NET698 : STD_LOGIC;

begin

---- Component instantiations ----

U1 : TPUHER

port map(

C => C,

Q => Q(1),

R => NET698,

S => S(1),

T => NET698,

nQ => NET138

);

U10 : vabo

port map(

a => a,

b => NET317,

y => NET143

);

U11 : TPUHER

port map(

C => NET143,

Q => Q(6),

R => NET698,

S => S(6),

T => NET698

);

U2 : vabo

port map(

a => a,

b => NET138,

y => NET133

);

U3 : TPUHER

port map(

C => NET133,

Q => Q(2),

R => NET698,

S => S(2),

T => NET698,

nQ => NET302

);

U4 : vabo

port map(

a => a,

b => NET302,

y => NET148

);

U5 : TPUHER

port map(

C => NET148,

Q => Q(3),

R => NET698,

S => S(3),

T => NET698,

nQ => NET307

);

U6 : vabo

port map(

a => a,

b => NET307,

y => NET405

);

U7 : TPUHER

port map(

C => NET405,

Q => Q(4),

R => NET698,

S => S(4),

T => NET698,

nQ => NET312

);

U8 : vabo

port map(

a => a,

b => NET312,

y => NET209

);

U9 : TPUHER

port map(

C => NET209,

Q => Q(5),

R => NET698,

S => S(5),

T => NET698,

nQ => NET317

);

---- Terminal assignment ----

-- Inputs terminals

NET698 <= R;

NET698 <= T;

end ct;