4. Логическое проектирование.

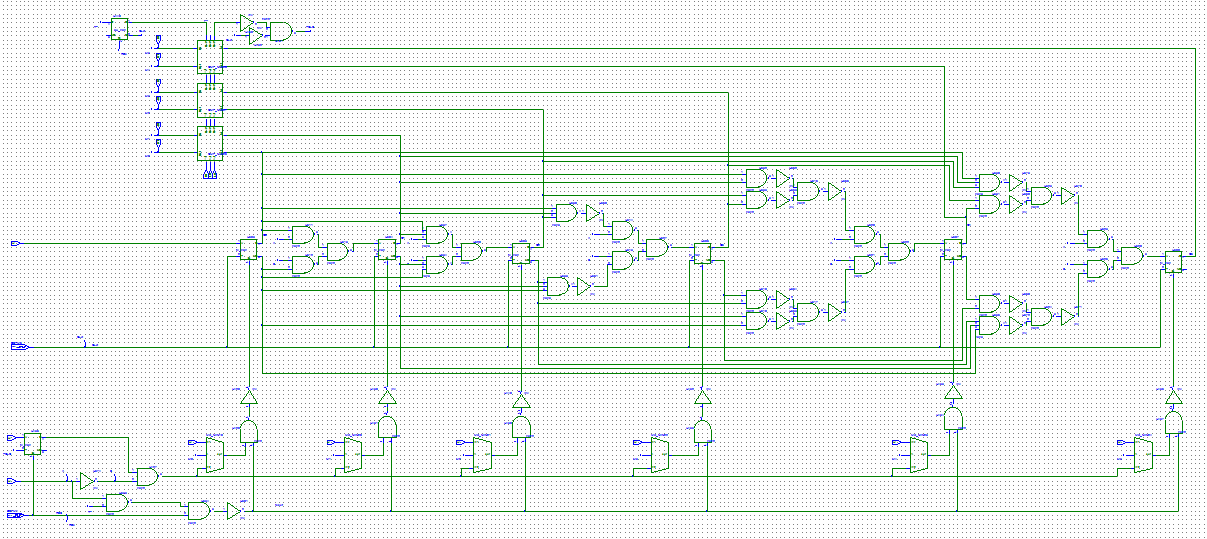

За основу устройства принят шестиразрядный реверсивный счетчик, построенный в соответствии со схемой, приведенной на рисунке 3.1. Для управления модулями счета в схему дополнительно введены 2 триггера (TV и DC), а так же блоки компаратора и мультиплексора.

Опишем работу счетчика в прямом и обратном направлении счета.

В прямом направлении счета на компараторе выставляется число M-1, где М – модуль счета. При появлении на счетчике числа М-1 компаратор срабатывает по выходу “равно”. Этот сигнал поступает на вход D-триггера, который выдает сигнал сброса, спустя такт.

В обратном направлении счета при том же модуле, а соответственно и тех же сигналах на компараторе на выходах счетчика появляется число N-1, где N – разрядность счетчика. В результате чего компаратор срабатывает по выходу ”больше”. Данный сигнал поступает на вход TV-триггера, который выдает сигнал сброса. Этот сигнал поступает на входы мультиплексоров, которые стоят перед каждым триггером счетчика. Управляющими сигналами мультиплексора являются сигналы управления модулем счета. Таким образом происходит обнуление необходимых триггеров и предустановка начального значения счетчика.

Для обеспечения независимости сбросов прямого и обратного счетов введены 3 конъюктора, на которые подан сигнал, управляющий направлением счета.

Как это описание ввязано со следующим рисунком 4.1 не ясно.

Разрядность счетчика равна 6. Вы уверены в правильности описания работы в режиме вычитания?

У Вас по заданию всего четыре модуля счета, т.е. устройству достаточно всего двух сигналов, управляющих модулем счета. А у Вас их целых шесть, для чего?

Реверсивный счетчик с переменным модулем счета .

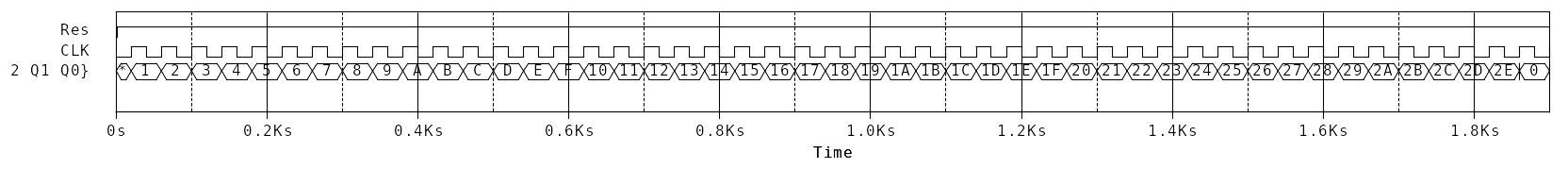

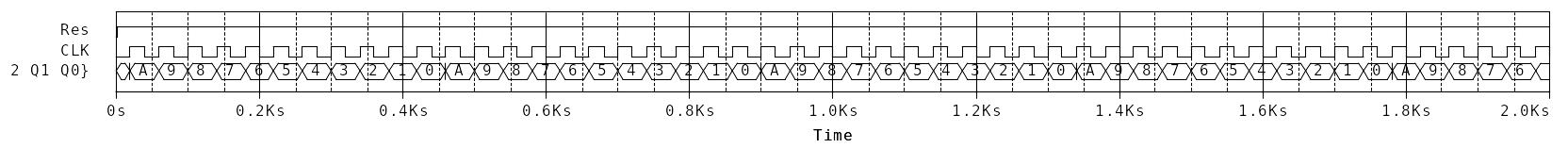

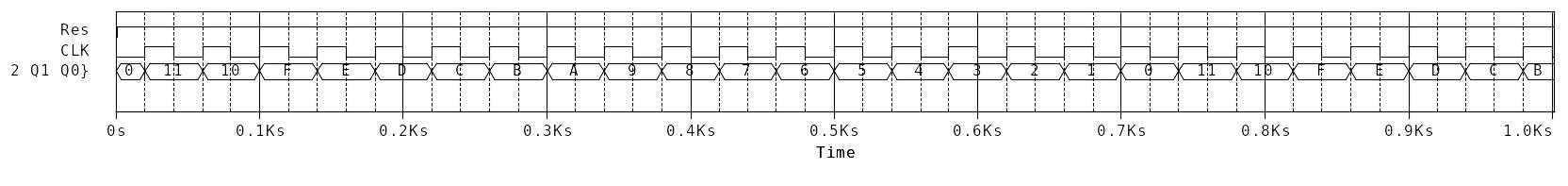

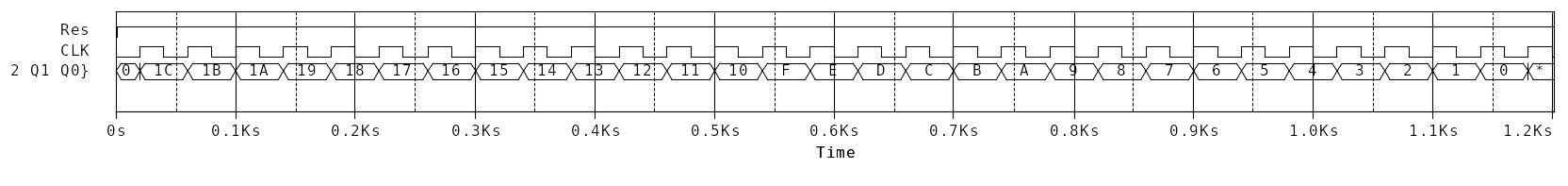

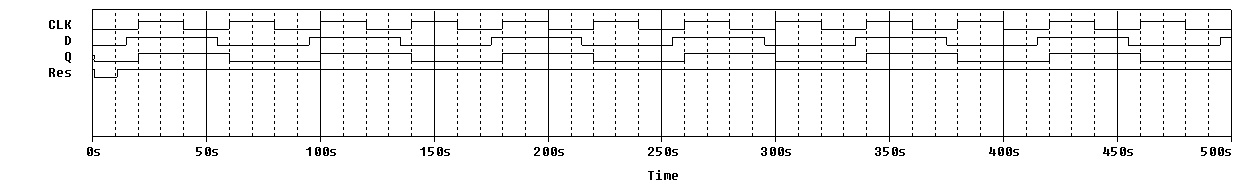

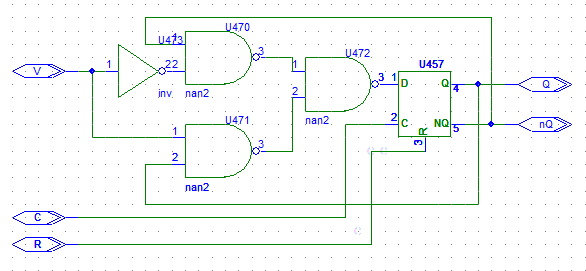

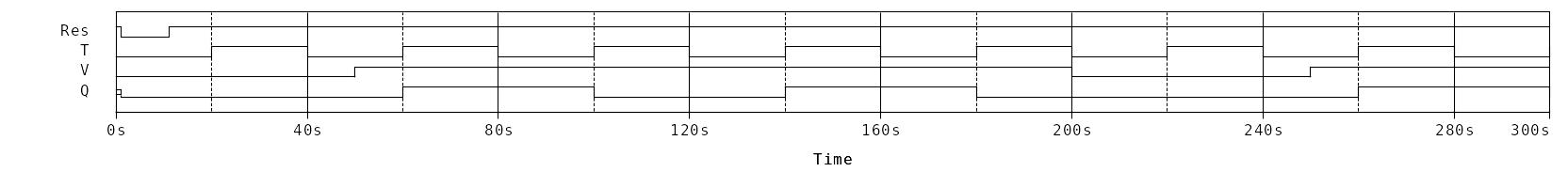

Конечная схема полученная в результате логического моделирования показана на рисунке 4.1, а её временные диаграммы на рисунке 4.2.

Рисунок 4.1 — реверсивный счетчик с переменным модулем счета

а) 11

б) 18

в)

29

в)

29

г)

47

г)

47

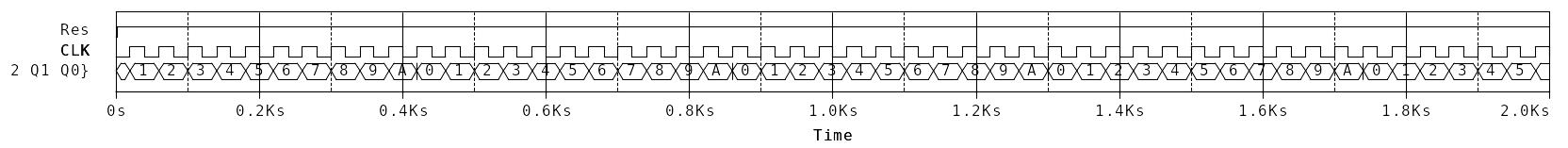

Рисунок 4.2 — Временные диаграммы счетчика (прямой счет)

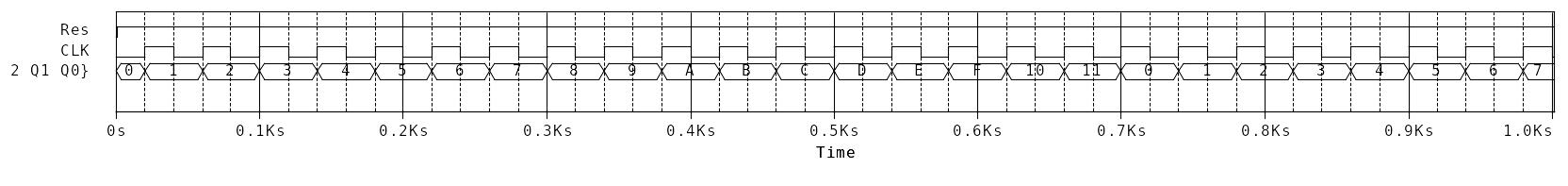

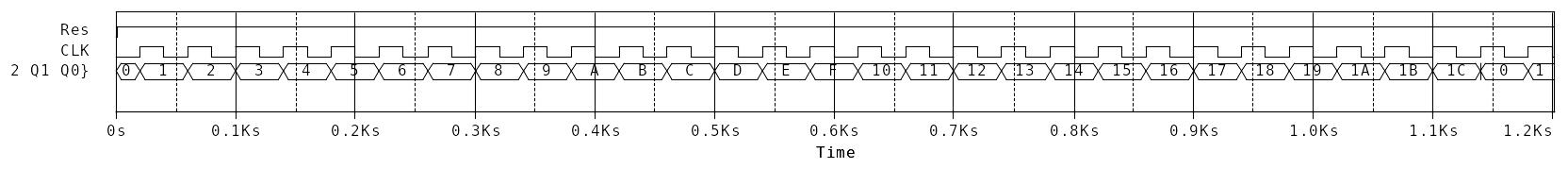

а)11

б)18 в)29

в)29

г)47

Рисунок 4.3 — Временные диаграммы счетчика (обратный счет)

Как будет работать устройство при понижении модуля счета из большего, чем новый модуль числа?

Например. M1 = 47 и текущее число на счетчике Q1 = 12, в этот момент переключаемся на модуль счета M2 = 11. Какое число появится на счетчике на очередном такте и далее?

RS-триггер.

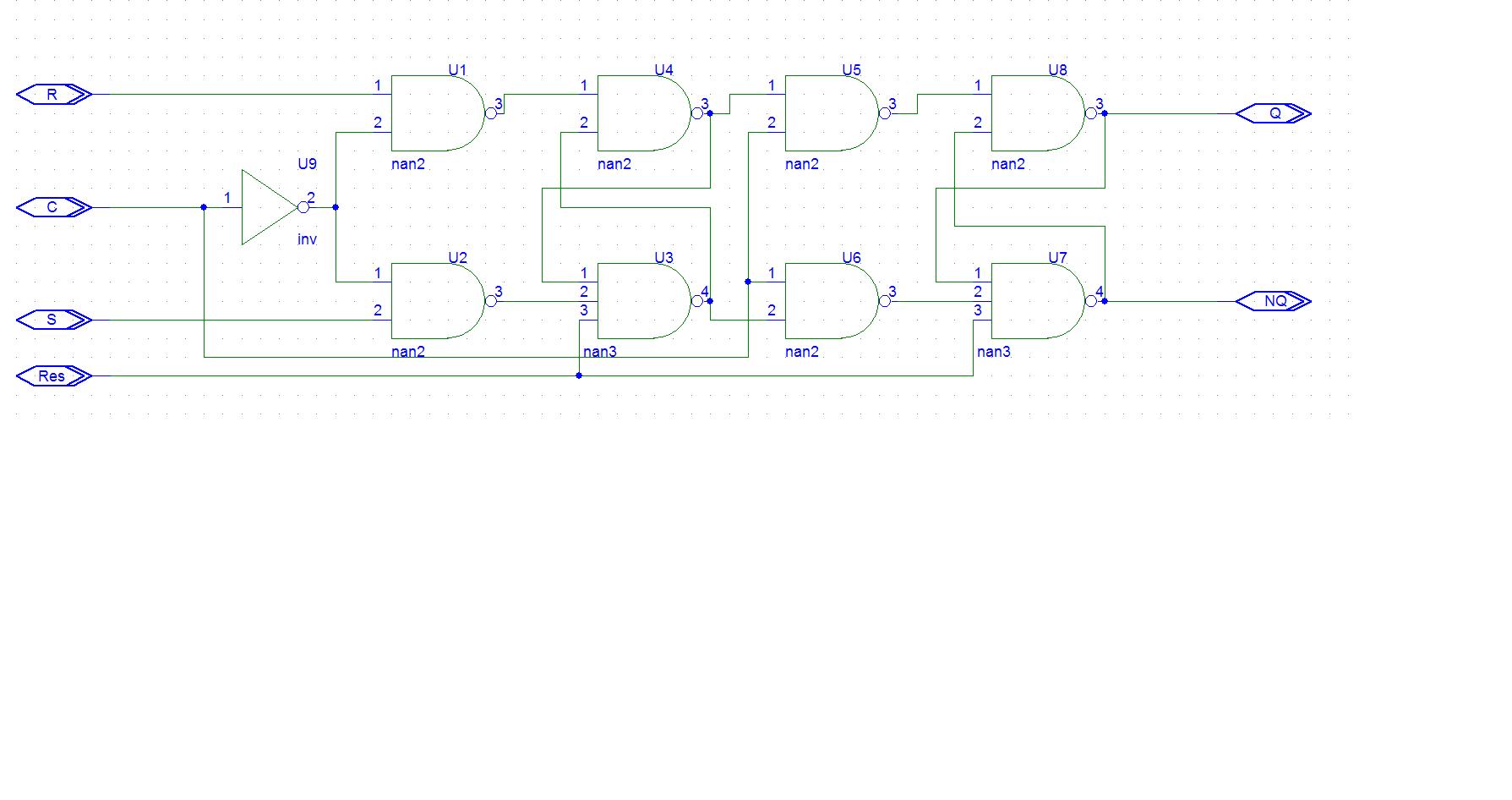

Схема RS-триггера показана на рисунке 4.4.

R |

S |

Qn |

Qn+1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

x |

1 |

1 |

1 |

x |

Т аблица

4.1 - таблица истинности RS-триггера.

аблица

4.1 - таблица истинности RS-триггера.

Рисунок 4.4 — переключающийся по фронту RS-триггер в базисе И-НЕ

и его диаграмма работы

DC-триггер.

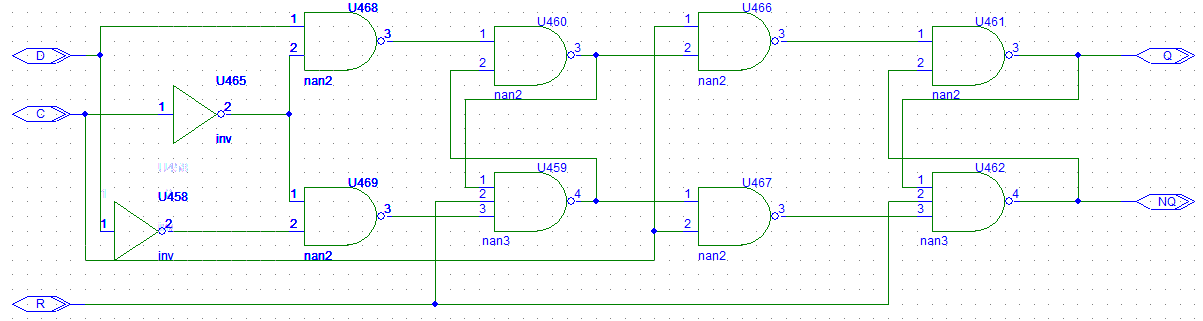

Схема DC-триггера показана на рисунке 4.5.

Qn

D

C

Qn+1

Qn

D

C

Qn+1

0

0

0

0

1

0

0

1

0

0

1

0

1

0

1

0

0

1

0

0

1

1

0

1

0

1

1

1

1

1

1

1

Таблица 4.2 – Таблица истинности DC-триггера

![]()

Рисунок 4.5 — DC-триггер в базисе И-НЕ и его диаграмма работы

TV-триггер.

Схема TV-триггера показана на рисунке 4.6.

V |

T |

Qn |

Qn+1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

Таблица 4.3 – таблица истинности TV-триггера

Qn+1=

![]()

![]()

![]() ;

;

Рисунок 4.6 — переключающийся по фронту TV-триггер в базисе И-НЕ и его диаграмма работы

Мультиплексор.

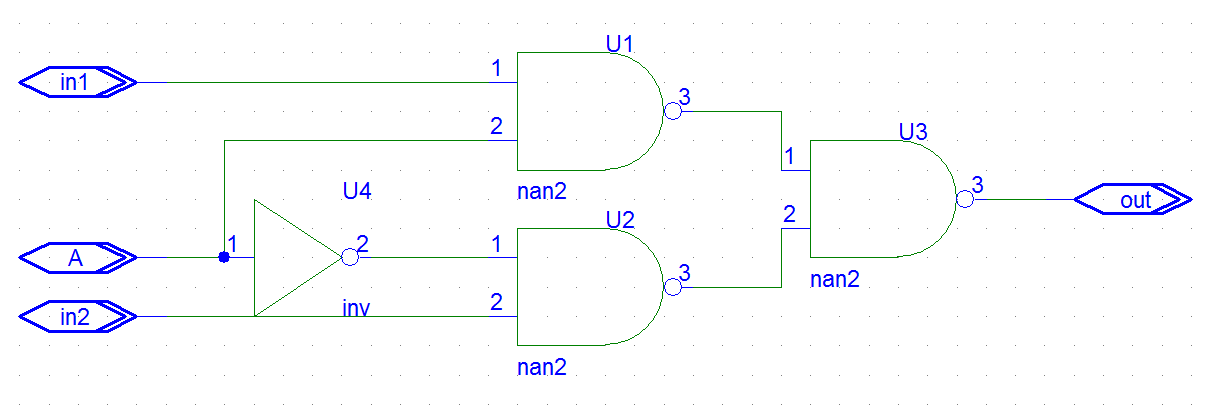

Для управления режимами счета (прямой - обратный) и сброса, используется мультиплексор 2-1. Его схема представлена на рисунке 4.7.

Рисунок 4.7 — мультиплексор 2-1 в базисе И-НЕ

Логическая

функция мультиплексора в соответствии

с логическим базисом.

![]()

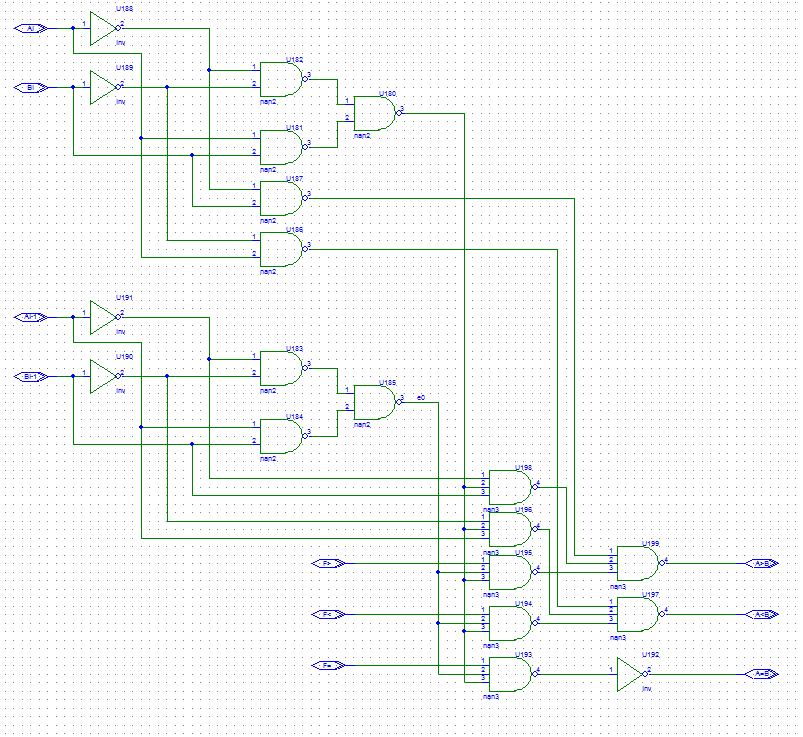

Компаратор для управления счетом.

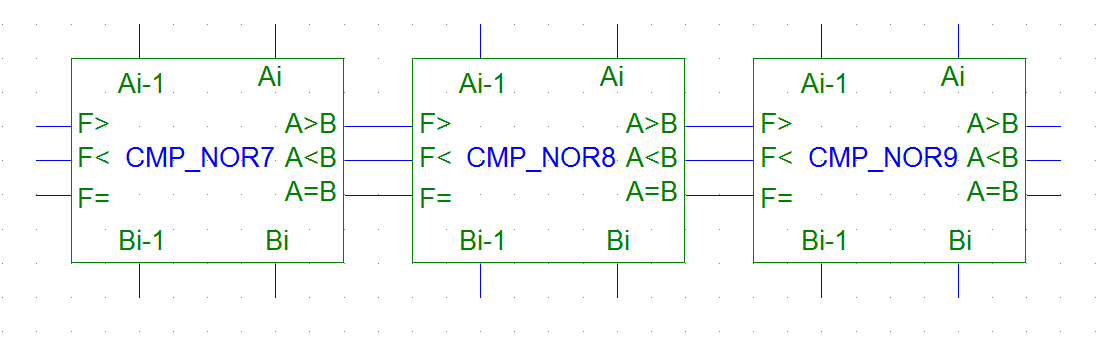

За основу возьмем схему двухразрядного компаратора с возможностью наращивания из книги «Цифровая схемотехника». рисунок 4.8.

Рисунок 4.8 —Двухразрядный компаратор

a |

b |

FA>B |

FA<B |

FA=B |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

Таблица 4.4 – таблица истинности компаратора.

Логические функции компаратора с учетом входов повышения разрядности (F’):

![]()

![]()

![]()

Каскадируя данный компаратор получаем шестиразрядный (рисунок 4.9)

Рисунок 4.9 —Шестиразрядный компаратор

Максимальный путь равен 28 вентилям. Максимальный коэффициент разветвления по выходу равен 6.