Московский Институт Электронной Техники (ТУ)

Курсовой проект

по курсу микросхемотехники цифровых интегральных схем

на тему:

«Реверсивный счетчик с переменным модулем счета (11 18 29 47), триггер t-V»

Выполнил:

Проверили: Гуминов Н.В.

Балашов А.Г.

Москва

2011

Оглавление

1. Введение 4

2.Техническое задание 5

ТРИГГЕРНЫЕ СХЕМЫ 6

4. Логическое проектирование. 13

1. Введение

Разработка интегрального прибора делится на три основных этапа: логическое проектирование, схемотехническое проектирование и топологическое проектирование.

Разработка логической схемы производится с помощью составления таблиц истинности и карт Карно и преобразования готовых формул с помощью правил де Моргана.

Схемотехническое моделирование проводится на основе логической схемы, после замены всех логических вентилей на эквивалентные схемы в КМОП базисе.

Топология разрабатывается в соответствии с технологическим базисом, предложенным в техническом задании.

В данном курсовом проекте разрабатывается реверсивный счетчик с переменным модулем счета (11 18 29 47) на триггерах TV.

Более полное описание устройства будет предложено в последующей части работы.

2.Техническое задание

Подробное описание технического задания приведено в таблице 2.1.

Таблица 2.1: Техническое задание

№ |

Параметр ТЗ |

Значение |

1 |

номер варианта |

23 |

2 |

название устройства |

Реверсивный счетчик, TV |

3 |

логический базис |

И-НЕ |

4 |

технологический базис |

ES2-0.7um |

5 |

время фронта и среза, tфр,ср, нс |

3 |

6 |

рабочая частота по входному сигналу, fраб, МГц |

10 |

7 |

рабочая частота по входам настройки, fset, МГц |

-- |

8 |

нагрузочная емкость, Cн, пФ |

3 |

9 |

напряжение питания, Vdd, В |

5 |

3. Теоретические сведения триггерные схемы

Логические схемы с несколькими логическими переменными на входах, в которых имеются два устойчивых состояния и два выхода, при этом на одном выходе схемы снимается высокий потенциал («1», Q), а на другом – его инверсия («0», Q), называется триггерами. Выходные сигналы в триггерах зависят не только от входных управляющих переменных, но и от значений выходных переменных в предыдущем интервале времени. В интервале между входными управляющими логическими сигналами состояние триггера не меняется, он «помнит» набор предыдущих логических переменных, на выходах сохраняются соответствующие потенциалы (бистабильная ячейка, БЯ). Изменить состояние триггера и, значит, величины потенциалов на выходах, возможно только под действием определенного набора входных логических переменных и значений выходных переменных в предыдущем интервале работы схемы.

Поскольку для переустановки триггера в конечном диапазоне времени необходима некоторая последовательность управляющих сигналов при наличии на выходах конкретного логического состояния, триггерные схемы относятся к классу последовательностных логических схем. Способность триггеров под действием определенного набора входных логических переменных «запоминать» состояние на выходе в течение неограниченного времени (без отключения питания) позволяют использовать их в качестве элементов памяти.

Переключение триггеров под действием запускающего сигнала происходит скачкообразно, лавинообразно, формируется выходной сигнал с крутыми фронтами, поэтому их часто называют защелками (latch), спусковыми устройствами.

В общем случае триггерное устройство состоит из входной комбинационной логической схемы, формирующей команду управления триггером, и собственно триггерный элемент памяти.

Простейший триггер можно реализовать на усилителях, охваченных положительной обратной связью (ПОС), например, на элементах И-НЕ или ИЛИ-НЕ, у которых, в соответствии с передаточной характеристикой, выполняются функции усиления и инверсии. На рис. 1. показаны обобщенный триггерный элемент (а), реализация бистабильной ячейки на усилителях-инверторах (б), схемы ячейки памяти (простейшие триггеры) на элементах 2И-НЕ (в) и 2ИЛИ-НЕ (г).

Выходные переменные принято обозначать буквами Q иQ, можно записать постулат триггера [1]:

Q = 1, Q = 0,

Q = 0, Q = 1.

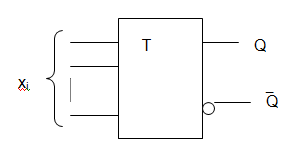

Входные логические переменные (в общем случае хi) обозначаются следующими символами:

S (set) – установка триггера (Q=1),

R (reset) – сброс триггера (Q=0),

J (jet) – вход установки универсального триггера (Q=1),

K (key cancel) - вход сброса универсального триггера (Q=0),

D (data) информационный вход, данные,

T (takt) – счетный вход,

C (clock) – управляющий тактовый сигнал, синхросигнал,

Pr (precharge) – сигнал выборки, предзаряда, активизации триггера,

Cl (cleare) – сброс, очистка, стирание, установка в «0»-состояние,

V – сигнал блокирования работы триггера, сохранение ранее записанной информации.

Рис.3.1 Обобщенный триггер, триггер на элементах 2ИЛИ-НЕ.

Триггер считается установленным (в состояние «1»), если Q = 1,Q = 0.

Триггер считается сброшенным (в состояние «0»), если Q = 0,Q = 1.

Комбинация возможных сочетаний входных логических переменных и выходных значений функции лежит в основе классификации типов триггеров по реализуемой логической функции. Некоторые сочетания переключающих сигналов и выходных состояний из всех возможных переборов (для конечного числа входов) никогда не используются, а некоторые применяются очень широко.

Наиболее широко применяются в микроэлектронике триггеры RS-, RST(С)-, JK-, JKT- T-, VT-, D-, DC(Т)-, DV- типов.

Различают асинхронные и синхронные триггеры.

Асинхронные триггеры переключаются при изменении сигналов на информационных входах.

Синхронные триггеры переключаются только под действием определенного активизирующего синхронизирующего сигнала (тактового сигнала, синхроимпульса, синхросигнала и т.д.).

Синхронизируемые триггеры могут быть:

статическими, они меняют состояние под действием либо высокого («1»), либо низкого («0») уровня синхросигнала. В течение разрешающего значения одного синхросигнала триггер может переключаться несколько раз под действием информационных сигналов в соответствии с логической функцией.

динамическими, они переключаются при поступлении положительного (фронт) или отрицательного (срез) перепада синхронизирующего напряжения. За время действия одного синхроимпульса триггер может переключиться только один раз.

Частота работы асинхронного триггера определяется только собственными задержками в логических элементах, на которых реализован данный триггер. Частота изменения входных сигналов определяется временем завершения процесса переключения на выходах триггера.

Частота работы синхронного триггера определяется частотой синхросигнала. Суммарные задержки логических элементов, на которых реализован триггер, должны обеспечить возможность реализации логической функции за время действия одного синхросигнала.

Работу конкретного триггера определяет логическая функция (характеристическое уравнение) или таблица состояний (переходов).

Входы триггера могут быть прямыми или инверсными, то есть действующий переключающий сигнал может быть высоким («1») или низким («0»). Чаще всего это связано с элементной базой, в которой реализован триггер: для элемента ИЛИ-НЕ сигнал 0 является пассивным, его появление не изменяет состояние триггера, а сигнал 1 – это активный сигнал, при его появлении на выходе триггера будет состояние 0. На схеме рис.1,г показан простейший триггер на ИЛИ-НЕ элементах. Входу S поставлен в соответствие выход Q. для элементов И-НЕ сигнал 0 будет активным, так как при его появлении на входе элемента, на выходе появится 1, триггер переключается (рис.1,в).

Базовая триггерная ячейка RS- типа, показанная на рис 1, имеет вход S установки в 1 и вход R установки в 0. Сочетание значений входных переменных S = 1, R = 1 запрещено, поскольку на обоих выходах должны установиться логические 0 и после окончания действия входных сигналов состояние триггера будет неопределенным: в схеме с глубокой ПОС одинаковые состояния невозможны, а в какую сторону перебросится триггер – не известно.

Опишем работу RS- триггера при помощи логической функции и таблицы истинности:

Qn+1 = S + QnR.

Для схемы с инверсными информационными входами:

Qn+1 =S + QnR.

В таблице истинности (таблице переходов) демонстрируется, как исходное состояние Qn триггера (n- ный такт работы) под действием входных переменных меняется на Qn+1 состояние в (n+1)- такте работы в соответствии с логической функцией.

Таблица 1. Таблица состояний RS- триггера.

-

Таблица переходов RS-триггера

Qn

S

R

Qn+1

0

0

0

0

0

0

1

0

0

1

0

1

0

1

1

Неопределенность

1

0

0

1

1

0

1

0

1

1

0

1

1

1

1

Неопределенность

Составим карту Карно для RS- триггера.

Qn

S |

1 |

х |

х |

1 |

1 |

0 |

0 |

0 |

R

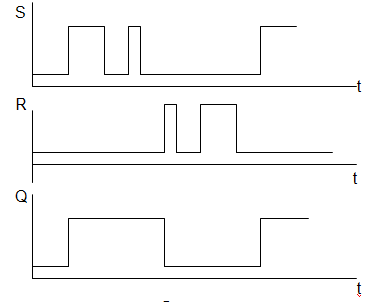

На рис.2 показана идеализированная тактовая диаграмма работы рассмотренного асинхронного RS- триггера с прямыми входами (ИЛИ-НЕ базовые элементы).

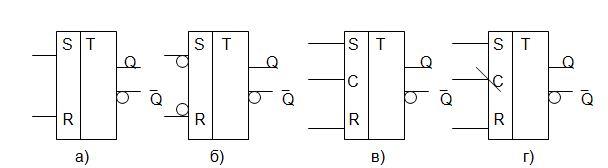

На рис.3 представлены виды условных обозначений RS- триггеров.

Рис.3.2. Тактовая диаграмма работы идеализированного асинхронного RS-триггера

Рис.3.3. Условные обозначения RS- триггеров: асинхронный с прямыми входами (а), асинхронный с инверсными входами (б), синхронный с прямыми статическими входами (в), синхронный с прямыми динамическими входами, управляемый срезом (г).

RS- и RSТ- триггеры редко используют в качестве отдельного схемного узла из-за наличия неопределенных состояний на выходах схемы при одновременных единицах на управляющих входах, но они являются базовыми элементами для построения других типов триггеров.

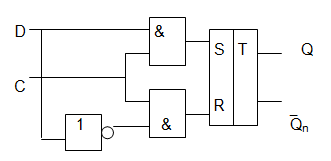

На рис. 3.4,3. 5, показаны структурные схемы наиболее распространенных типов триггерных схем: D- триггер, JK- триггер соответственно.

Qn+1=

CD +CQn

Рис.3.4. Триггер D-типа (задержки, хранения), статический на RS- триггере.

Qg+1

= C(JQn

+ KQn)

+ CQn

Рис. 3.5. Структурная схема универсального статического JK- триггера на RS- триггере.

В работе триггерных схем возникают критические последовательности входных сигналов, приводящие к неоднозначности или неустойчивости состояний на выходах. Чаще всего это последовательности сигналов SR = 1100 для дизъюнктивных БЯ и SR = 0011 для конъюнктивных БЯ. Рекомендуется избегать таких сочетаний переменных в соответствующих триггерах.

Еще одна особенность работы триггерных схем связана с возможностью появления состязаний. Состязанием называется эффект неодновременного изменения управляющих сигналов на входах триггера или внутренней БЯ, связано это с различными задержками распространения сигналов в элементах и узлах устройства. В том случае, когда разность времени изменения управляющих сигналов превышает время переключения БЯ, возможно ее переключение в некоторое промежуточное состояние, не предусмотренное логической функцией. Лучший способ устранения состязаний – введение запрещения на изменение некоторой входной переменной в течение определенного промежутка времени. Такие меры ведут к снижению тактовой частоты устройства, но обеспечивают его устойчивую работу.

С четчик

– это тип автоматов, которые под

действием входных импульсов переходят

из одного состояния в другое, фиксируя

тем самым число поступивших на вход

импульсов в том или ином коде. Каждый

счетчик характеризируется емкостью

или модулем счета М. Эта характеристика

определяет число возможных состояний

счетчика. При поступлении на счетчик

М входных сигналов начинается новый

цикл, полностью повторяющий предыдущий.

Счетчики классифицируют по следующим

признакам: по способу кодирования

(двоичные, двоично-десятичные, счетчики

Джонсона и др.), по направлению счета

(суммирующие, вычитающие, реверсивные),

по типу переноса (последовательные,

параллельные, комбинированные),

синхронные или асинхронные. Как и любой

автомат, счетчик можно построить на

триггерах любого типа, однако удобнее

всего будет использовать счетные,

Т-триггеры, или JK, включенные

в счетном режиме (J=K=1).

четчик

– это тип автоматов, которые под

действием входных импульсов переходят

из одного состояния в другое, фиксируя

тем самым число поступивших на вход

импульсов в том или ином коде. Каждый

счетчик характеризируется емкостью

или модулем счета М. Эта характеристика

определяет число возможных состояний

счетчика. При поступлении на счетчик

М входных сигналов начинается новый

цикл, полностью повторяющий предыдущий.

Счетчики классифицируют по следующим

признакам: по способу кодирования

(двоичные, двоично-десятичные, счетчики

Джонсона и др.), по направлению счета

(суммирующие, вычитающие, реверсивные),

по типу переноса (последовательные,

параллельные, комбинированные),

синхронные или асинхронные. Как и любой

автомат, счетчик можно построить на

триггерах любого типа, однако удобнее

всего будет использовать счетные,

Т-триггеры, или JK, включенные

в счетном режиме (J=K=1).

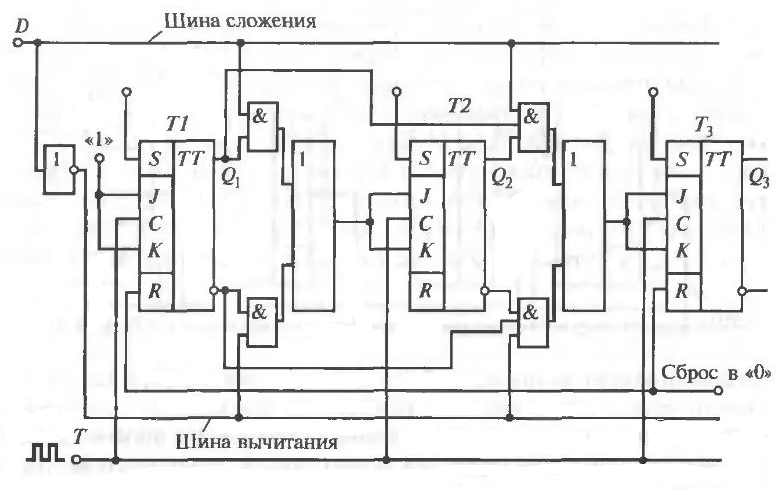

Рисунок 3.1. Реверсивный счетчик .

Реверсивный счетчик должен работать как на сложение, так и на вычитание. В суммирующем счетчике каждый последующий триггер принимает информацию с прямого выхода предыдущего, а в вычитающем - с инверсного входа, т.е. для перехода от сложения к вычитанию и обратно надо изменять подключение счетного входа последующего триггера к выходу предыдущего.