- •Лабораторна робота №1 Системні плати пк. Шини сучасних пк

- •Теоретичні відомості

- •1). Підтримка сучасних процесорних технологій.

- •2). Гнучкість стосовно швидко змінних процесорних технологій.

- •3). Підтримка інших нових технологій.

- •Контрольні запитання

- •1). Мікросхема з scsі bіos є на самому контролері (як на відеокартах).

- •2). Образ scsі bіos прошитий у Flash-bіos материнської плати.

- •3). Scsі bіos немає взагалі. Робота всіх scSі-пристроїв забезпечується тільки драйверами операційної системи.

- •1). Мікросхеми пзп.

- •2). Статичне озп.

- •3). Динамічне озп (дозп).

- •Завдання для лабораторної роботи

- •Контрольні запитання

- •1) Управління динаміком з використанням таймера.

- •2) Управління динаміком без таймера.

- •3) Відтворення музики.

- •Завдання для лабораторної роботи

- •Контрольні запитання

- •Лабораторна робота №6. Клавіатура

- •Теоретичні відомості

- •1). Вхідній і вихідній буфери даних.

- •2). Регістр стану (rs).

- •3). Порт контролера 8042 (р1, р2).

- •4) Керуючі сигнали t0 і t1.

- •5) Інтерфейс 8042 з клавіатурою.

- •6) Програмування контролера.

- •1). Обробка клавіш зсуву (Shift, Ctrl, Alt).

- •2). Обробка клавіш-перемикачів (Insert, CapsLock, NumLock, ScrollLock.).

- •3). Комбінація Ctrl-Alt-Del.

- •4). Комбінація Ctrl-Break.

- •6). Алфавітно-цифрові клавіші.

- •7). Спеціальні скан-коди.

- •1) Режими роботи.

- •2) Програмування контролера 8048 блоку клавіатури.

- •Завдання до лабораторної роботи.

- •Контрольні запитання

- •Лабораторна робота №7. Робота з відеопам’яттю в текстовому режимі

- •Теоретичні відомості

- •1) Монохромний mda.

- •2) Кольоровий графічний адаптер cga.

- •3) Розширений графічний адаптер ega.

- •4) Адаптери vga і svga.

- •5) Адаптер mcga.

- •6) Графічні сопроцесори.

- •1) Адаптери mda і cga.

- •2) Адаптер ega.

- •3) Адаптер mcga.

- •4) Адаптер vga.

- •Завдання до лабораторної роботи

- •Контрольні запитання:

- •Лабораторна робота №8 Робота з відеопам’яттю в графічному режимі.

- •Теоретичні відомості.

- •Завдання до лабораторної роботи

Завдання для лабораторної роботи

Завдання: написати програму для виконання завдання згідно свого варіанту.

Особливості програмування:

1). На мові Turbo-Pascal.

Для звернення до пам’яті використовується визначений масив Mem. Наприклад, для читання байта по адресу А000:0000h використовується вираз b:=Mem[$a000:$000] (b – змінна типу byte).

Для перевірки деяких бітів слова чи байта використовуйте операцію AND з маскою, що містить 1 в потрібних бітах та 0 в інших.

2). На мові Turbo-C.

Для звернення до пам’яті використовуються дальні вказівники, які описуються в програмі наступним чином: char far * uk; для роботи за байтами. Для читання байта по адресу А000:0000h використовується вираз uk=(char far *) 0xA0000000; b=* uk; де b –змінна типу char.

Для перевірки деяких бітів слова чи байта використовуйте операцію & з маскою, що містить 1 в потрібних бітах та 0 в інших.

Варіанти завдань.

1. Визначити дату створення BIOS.

2. Визначити тип ПК.

3. Визначити чи є у ПК НГМД.

4. Визначити чи є у ПК арифметичний сопроцесор.

5. Визначити чи є у ПК миша PS/2.

6. Визначити тип дисплея.

7. Визначити кількість НМГД.

8. Визначити чи є у ПК вбудований модем;

9. Визначити чи є у ПК вбудований ігровий адаптер;

10. Визначити кількість паралельних портів.

Контрольні запитання

1. Що включає в себе системна пам'ять ПК.

2. Фізична організація мікросхем ПЗП, статичного ОЗП, динамічного ОЗП.

3. Розподіл адресного простору пам'яті.

4. Які області адресного простору не міняються при переході в заборонений режим і чому.

5. Де розміщена системна BIOS і що вона включає в себе.

6. Яку довідкову інформацію користувач може прочитати з ПЗП BIOS.

7. Як знайти початкову фізичну адресу оброблювача i-го переривання.

8. Що таке розширена пам'ять (Extend Memory), для яких МП вона може бути реалізована і чому.

9. Призначення драйвера XMS і його основні функції.

10. Призначення і функції ЕММ-ДРАЙВЕРА.

11. Що таке UMB-блоки пам'яті і як вони використовуються.

12. КЕШ-пам’ять в сучасних персональних комп’ютерах.

13. Типи організації динамічної оперативної пам'яті.

14. Оперативна пам’ять FPM, EDO і BEDO.

15. Модулі SІММ, DІММ та RІММ, їх характеристики.

16. Пам’ять DDR SDRAM.

ЛАБОРАТОРНА РОБОТА №4

Запам’ятовуючі пристрої. Модулі пам’яті

Мета: ознайомитися з основними типами запам’ятовуючих пристроїв сучасних комп’ютерів та визначити їх параметри.

Теоретичні відомості.

Запам’ятовуючі пристрої. Модулі пам’яті

Пам'ять типу ROM – або ПЗП, використовується тільки для зчитування даних. Існує три типи мікросхем ROM:

– ROM (Read Only Memory) – постійна пам’ять, пришивається при виготовлені;

– PROM (Programmable ROM) – програмований ПЗП;

– EPROM (Erasable PROM), EEPROM (Electrically Erasable PROM), Flash ROM – ППЗП з ультрафіолетовим та електронним стиранням.

Пам'ять типу SRAM – статична оперативна пам’ять (Static RAM). Має високу швидкодію, тому використовується в якості кеш-пам’яті.

Щоб мінімізувати час очікування при зчитуванні процесором даних з повільної оперативної пам'яті, в сучасних персональних комп'ютерах передбачено два типи кеш-пам'яті: кеш-пам'ять першого рівня (L1) і кеш-пам’ять другого рівня (L2). кеш-пам'ять першого рівня також називають вбудованим або внутрішнім кешем, вона безпосередньо вбудована в процесор і фактично є частиною мікросхеми процесора. Кеш-пам'ять другого рівня називають зовнішнім кешем. Спочатку вона встановлювалася на системній платі і працювала на частоті системної плати. Для підвищення ефективності в процесорах Pentium Рго та Pentium ІI/ІIІ кеш-пам'ять другого рівня встановлюється не на системній платі, а в середині корпуса (картриджа) процесора.

Пам'ять типу DRAM – динамічна оперативна пам’ять (Dynamic RAM) використовується в більшості систем сучасних ПК. Цій пам’яті характерна невисока швидкодія, тому існує кілька типів організації DRAM, які покращують швидкодію: FРМ. ЕDО, BEDO, SDRАМ, RDRAM, DDR SDRAM.

FРМ (Fast Page Mode) – швидкий сторінковий режим динамічної оперативної пам’яті. Щоб скоротити час очікування, стандартна пам'ять DRAM розбивається на сторінки. Як правило для доступу до даних в пам'яті необхідно вибрати рядок та стовпець адреси, що забирає певний час. Розбиття на сторінки забезпечує швидший доступ до всіх даних в межах даного рядка пам'яті, тобто якщо змінюється не номер рядка, а тільки номер стовпця. FРМ ще називають Static Column або Nibble Mode. Сторінкова організація пам'яті – проста схема підвищення ефективності пам'яті, у відповідності з якою пам'ять розбивається на сторінки від 512 байт до кількох кілобайт. Електронна схема перегортання дозволяє при зверненні до комірок пам'яті в межах сторінки зменшити кількість станів очікування. Якщо потрібна комірка пам'яті знаходиться за межами поточної сторінки, то додається один або більше станів очікування, так як система вибирає нову сторінку. Для збільшення швидкості доступу до пам'яті FРМ був втілений пакетний (burst) режим доступу. Переваги пакетного режиму доступу проявляється тому, що в більшості випадків доступ до пам'яті є послідовним. Після встановлення рядка і стовпця адреси в пакетному режимі можна звертатися до наступних трьох суміжних адрес без додаткових станів очікування. Але доступ в пакетному режимі обмежується чотирма операціями. Схема синхронізації в пакетному режимі для стандартної DRAM з часом доступу 60 нc виглядає так: 5-3-3-3. Це означає, що перша операція доступу займає п'ять циклів на системній шині з частотою 66 МГц (тривалість одного такту 15 нc), що дорівнює 75 нc (5*15 нc), в той час як наступні операції займають по три циклу кожна (3*15 нc = 45 нc). Без розбиття на сторінки схема доступу виглядала б як 5-5-5-5, тому що для кожної передачі даних запам'ятовуючому пристрою потрібно було б один і той же час очікування. Іншим методом прискорення пам'яті FРМ є чергування. Цей метод використовує сумісно два окремих банка пам'яті, розподіляючи парні і непарні байти між цими банками. Коли відбувається звернення до одного банку, в іншому банку вибирається рядок і стовпець адреси. До моменту закінчення вибірки даних в першому банку в другому закінчуються цикли очікування і він буде готовий до вибірки даних. Коли дані вибираються із другого банку, в першому йде процес вибірки рядка і стовпця адреси для наступної операції доступу. Це суміщення (перекриття в часі) операцій доступу в двох банках призводить до зменшення часу очікування і забезпечує швидший пошук даних. Єдина проблема полягає в тому. що для використання цього метода необхідно встановлювати ідентичні пари банків, при цьому вдвоє збільшується кількість мікросхем.

Оперативна пам'ять ЕDО (Extended Data Out) використовується з 1995 року. Це вдосконалений тип FРМ, його ще називають Hyper Page Mode. Пам'ять ЕDO збирається із спеціально виготовлених мікросхем, які враховують перекриття синхронізації між черговими операціями доступу. Драйвери виведення даних на мікросхемі, на відміну від FРМ, не вимикаються, коли контролер пам'яті знищує стовпець адреси на початку наступного циклу. Це дозволяє сумістити по часу наступний цикл з попереднім, економлячи приблизно 10 нc в кожному циклі. Таким чином, контролер пам'яті ЕDО може починати виконання нової команди вибірки стовпця адреси, а дані будуть зчитуватися по поточній адресі. Це майже ідентично використанню різних банків для чергування пам'яті, але на відміну від чергування, не потрібно одночасно використовувати два ідентичних банка пам'яті в системі. Для оперативної пам'яті EDO схема синхронізації в пакетному режимі має вигляд 5-2-2-2. Це означає, що чотири передачі даних займають 11 повних системних циклів (проти 14 циклів в пам'яті FРМ).

Оперативна пам'ять ВЕDO (Burst Extended Data Out) - є різновидом пам'яті EDO. В основному це таж сама пам'ять, що і ЕDО, але з швидшою передачею даних. На жаль, тільки набір системної логіки Intel 440FX підтримує її.

Мікросхеми FРМ, ЕDО і ВЕDО встановлюються в модулі пам'яті SІММ. В комп'ютерах застосовується два типа модулів SІММ: 30-контактні (9 розрядів) і 72-контакті (36 розрядів). Мікросхеми в модулях SIММ можуть встановлюватися як на одній, так і на обох сторонах плати. Використання 30-контактних модулів в сласних системах неефективно, оскільки для заповнення одного банку пам'яті 64-розрядних систем необхідно вісім таких модулів. Для заповнення одного банку пам'яті в 64-розрядних системах 72-контактні SІММ необхідно встановлювати парами. На рис. 4.1 і 4.2 зображені типові 30- та 72-контактні модулі SІММ. Контакти нумеруються зліва направо і розміщуються з обох сторін плати модуля.

Рис.4.1 – 30-контактний модуль SIMM

Рис.4.2 – 72-контактний модуль SIMM

Ємності модулів бувають різні. В табл. 4.1 і 4.2 наведені ємності 30- та 72-контактних модулів SIMM. Модулі з різною ємністю можуть мати різну швидкодію – від 50 до 120 нс.

SDRАМ (Synchronous DRAM) – це тип динамічної оперативної пам'яті DRАМ. робота якої синхронізується з шиною пам'яті. Вона використовується з 1997 року. SDRAM передає інформацію в високошвидкісних пакетах, що використовують високошвидкісний синхронізований інтерфейс. SDRAM дозволяє уникнути більшості циклів очікування, необхідних при роботі асинхронної SDRAM, оскільки сигнали, по яким працює пам'ять такого типу, синхронізовані з тактовим генератором системної плати. Схема синхронізації пакетного доступу SDRAM виглядає як: 5-1-1-1, тобто чотири операції зчитування виконується за вісім тактів. Крім того, пам'ять SDRAM може працювати на частоті 100 МГц (10 нc). Останні оновлення SDRAM підтримують робочу частоту 133 МГц.

Таблиця 4.1 – Ємність 30-контактних модулів SIMM

|

Ємність

|

Модулі з контролем парності

|

Модулі без контролю парності

|

|

256 Кбайт |

256 Кбайт х 9 |

256 Кбайт х 8 |

|

1 Мбайт |

1 Мбайт х 9 |

1 Мбайт х 8 |

|

4 Мбайт |

4 Мбайт х 9 |

4 Мбайт х 8 |

|

16 Мбайт |

16 Мбайт х 9 |

16 Мбайт х 8 |

Таблиця 4.2 – Ємність 72-контактних модулів SIMM

|

Ємність

|

Модулі з контролем парності

|

Модулі без контролю парності

|

|

1Мбайт |

256 Кбайт х 36 |

256 Кбайт х 32 |

|

2 Мбайт |

512 Кбайт х 36 |

512 Кбайт х 32 |

|

4 Мбайт |

1 Мбайт х 36 |

1 Мбайт х 32 |

|

8 Мбайт |

2 Мбайт х 36 |

2 Мбайт х 32 |

|

16 Мбайт |

4 Мбайт х 36 |

4 Мбайт х 32 |

|

32 Мбайт |

8 Мбайт х 36 |

8 Мбайт х 32 |

|

64 Мбайт |

16 Мбайт х 36 |

16 Мбайт х 32 |

|

128Мбайт |

32 Мбайт х 36 |

3 2 Мбайт х 32 |

Пам'ять SDRAM виготовляється у вигляді модулів DIММ. 168-контактні модулі DIММ (72-розряди) широко використовуються в системах з процесорами Pentium MMX, Pentium Рго і Pentium II/IIІ. Модуль DІММ зображений на рис.4.3. Для забезпечення роботи системи достатньо одного модуля DІММ, оскільки він забезпечує роботу з 64 розрядами даних.

Рис.4.3 – 168-контактний модуль DIMM

В табл. 4.3 наведені ємності 168-контактних модулів DІММ. Для модулів DІММ швидкодія лежить в діапазоні від 10 до 60 нc.

Таблиця 4.3 – Ємність 168-контактних модулів DIMM.

|

Ємність

|

Модулі з контролем парності

|

Модулі без контролю парності

|

|

8 Мбайт |

1 Мбайт х 72 |

1 Мбайт х 64 |

|

16 Мбайт |

2 Мбайт x 72 |

2 Мбайт х 64 |

|

32 Мбайт |

4 Мбайт х 72 |

4 Мбайт х 64 |

|

64 Мбайт |

8 Мбайт х 72 |

8 Мбайт х 64 |

|

128 Мбайт |

16 Мбайт х 72 |

16 Мбайт х 64 |

|

256 Мбайт |

32 Мбайт х 72 |

32 Мбайт х 64 |

RDRAM (Rambus DRАМ) - радикально новий тип пам’яті. використовується з 1999 року. Мікросхеми RDRAM передбачають подвоєну (16-розрядну) шину передачі даних, а частота збільшена до 800 МГц (пропускна здатність мікросхеми дорівнює 1,6 Гбайт/с). Для збільшення продуктивності можна використовувати дво- і чотириканальні RDRAM, які дозволяють збільшувати швидкість передачі даних до 3,2 або 6,4 Гбайт/с. Один канал пам'яті Rambus може підтримувати до 32 мікросхем RDRAM, які встановлюються в модулі RІММ. Модуль RІММ зображений на рис. 4.4.

Рис.4.4 – 184-контактний модуль RIMM

Робота з пам'яттю організовується між контролером пам'яті та окремою мікросхемою. Передача даних здійснюється по шині даних мікросхеми шириною 2 байта. Шина пам'яті працює на частоті 400 МГц. але дані передаються по фронту та по спаду тактового сигналу, тобто двічі в тактовому імпульсі. Права границя тактового імпульсу називається парним циклом, а ліва - непарним. Синхронізація здійснюється з допомогою передачі пакетів даних на початку парного циклу. Максимальний час очікування складає 2,5 нc. Кожні 10 нc одна мікросхема RDRAM може передавати 16 байт. П'ять повних циклів тактового сигналу відповідає десяти циклам даних.

Пам'ять DDR SDRAM (Double Data Rate - подвійна швидкість передачі даних) – вдосконалений стандарт SDRAM, при використанні якого швидкість передачі даних збільшується вдвічі Це досягається не за рахунок збільшення тактової частоти, а за рахунок передачі даних два рази за один цикл, перший раз на початку циклу, а другий - в кінці. Саме завдяки цьому і збільшується швидкість передачі вдвічі (при цьому використовуються тіж самі частоти і синхронізуючі сигнали). Модулі пам'яті DDR виготовляються на основі мікросхем RDRAM, але набагато дешевші за модулі RІММ. В основному пам'ять DDR SDRAM використовується в системах з процесорами фірм АМD і Суrix.

Завдання до лабораторної роботи

Завдання: ознайомитися з теоретичними відомостями про запам'ятовуючі пристрої комп'ютера, визначити типи досліджуваних модулів пам'яті DRAM, встановити їх характеристики та способи організації, скласти звіт про виконання роботи.

Контрольні запитання

1. КЕШ-пам’ять в сучасних персональних комп’ютерах.

2. Типи організації динамічної оперативної пам'яті.

3. Оперативна пам’ять FPM, EDO і BEDO.

4. Модулі SІММ, DІММ та RІММ, їх характеристики.

5. Пам’ять DDR SDRAM.

ЛАБОРАТОРНА РОБОТА №5

Системний таймер.

Мета: вивчення функцій системного таймера та набуття практичних навичок роботи з таймером та динаміком при генерації звука.

Теоретичні відомості

Структура та призначення таймера

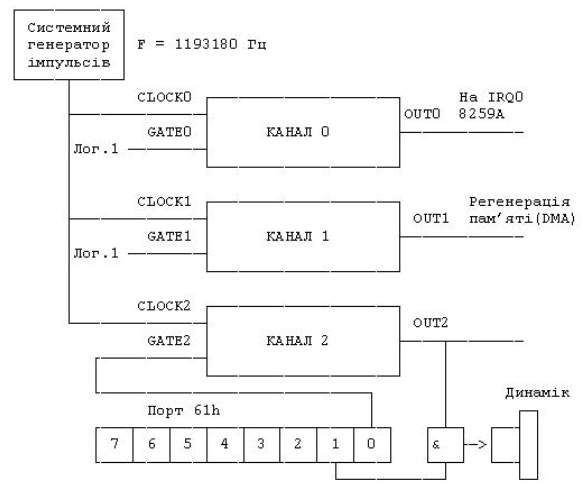

Всі комп'ютери IBM містять 3-х канальний 16-ти розрядний пристрій, що називається системним таймером. Таймер реалізується на мікросхемі Intel 8253 (для IBM PC та IBM XT) або 8254 (для IBM AT та IBM PS/2). Структурна схема системного таймера зображена на рис.5.1.

Рис. 5.1 – Структурна схема таймера

Таймери 8253 та 8254 складаються з трьох незалежних каналів. Кожний канал містить регістри:

– стану каналу RS (8 розрядів);

– керуючого слова PSW (6 розрядів);

– буферний регістр OL (16 розрядів);

– регістр лічильника CE (16 розрядів);

– регістр констант перерахунку CR (16 розрядів).

Канали таймера підключаються до зовнішніх приладів за допомогою трьох ліній:

– GATE - керуючий вхід;

– CLOCK - вхід тактової частоти;

– OUT - вихід таймера.

Регістр лічильника CE працює в режимі віднімання. Його вміст зменшується по задньому фронту сигналу CLOCK за умови, що на вході GATE встановлений рівень логічної 1. В залежності від режиму роботи таймера при досягненні лічильником CE нуля тим або іншим способом змінюється вихідний сигнал OUT.

Буферний регістр OL потрібен для запам’ятовування поточного вмісту регістру лічильника CE без зупинки процесу рахування. Після запам’ятовування буферний регістр є доступним програмі для зчитування.

Регістр констант перерахунку CR потрібен для зберігання констант перерахунку і може завантажуватися в регістр лічильника, якщо це вимагається в поточному режимі роботи таймера.

Вміст регістру CR змінюється тільки при перезавантаженні лічильника або при перепрограмуванні режиму (запису керуючого слова). При перепрограмуванні вміст CR обнулюється.

Регістр стану каналу RS зберігає поточний стан каналу і може бути зчитаний для вибраного каналу командою "зворотне читання".

Регістр керуючого слова PSW зберігає керуючу інформацію каналу і задає його режим роботи до наступного перепрограмування.

Системний генератор імпульсів (СГІ) незалежно від типу і продуктивності комп'ютера IBM виробляє імпульси однієї і тієї же частоти - 1 193180 Гц.

В комп'ютерах IBM PC/XT/AT/PS2 задіяні всі три канали таймера. Канал 0 використовується в системному годиннику. Цей канал працює в режимі 3 і використовується як генератор імпульсів з частотою приблизно 18.2 Гц. Вихід каналу OUT0 підключений до лінії запиту на переривання IRQ0 і виробляє переривання INT 8h приблизно 18.2 разу в секунду (точне значення - 1193180/65535 разу в секунду).

При ініціалізації BIOS встановлює свій оброблювач для переривань таймера. Ця програма кожний раз збільшує на 1 поточне значення 4-байтової змінної, що розташована в області даних BIOS за адресою 0040: 006Ch - лічильника тіков таймера.

Якщо цей лічильник переповнюється (тобто минуло більш 24 годин з моменту запуску таймера), в середину 0040: 0070h заноситься 1.

Стандартний оброблювач переривань таймера здійснює також контроль за роботою двигунів НГМД. Якщо після останнього звернення до НГМД минуло більше 2 секунд, оброблювач переривань вимикає двигун (адреса 0040:0040h містить час, що залишився до виключення двигуна).

Остання дія, яку виконує оброблювач переривань таймера, це виклик переривань INT 1Ch. Після ініціалізації системи вектор INT 1Ch вказує на команду IRET, тобто нічого не виконується. Програма користувача може встановити власний оброблювач цього переривання для того, щоб виконати будь-які періодичні дії.

Необхідно відзначити, що переривання INT 1Ch викликається до скидання контролера переривань, тому під час виконання переривання INT 1Ch всі апаратні переривання заборонені. Для скидання контролера переривань треба в порт 20h записати значення 20h. На рис.5.2. зображений механізм обробки переривання таймера.

Рис.5.2 – Механізм обробки переривань таймера

Канал 1 використовується для регенерації вмісту динамічної пам'яті комп'ютера, тому його краще не чіпати. Вихідна лінія каналу OUT зв'язана з мікросхемою прямого доступу до пам’яті (DMA), і її імпульс змушує DMA регенерувати пам'ять. Канал використовує режим 2 таймера. Канал 2 зв'язаний з гучномовцем (динаміком) комп'ютера і може бути використаний для генерації різноманітних звуків або музики або як генератор випадкових чисел. Канал використовує режим 3 таймера.

Програмування таймера

Кожний канал таймера програмується окремо і незалежно від інших. При програмуванні каналу необхідно послати йому керуюче слово (старші 2 розряди керуючого слова вказують номер каналу, а інші 6 розрядів запираються в регістрі PSW вибраного каналу), після чого у відповідний каналу таймера порт завантажуються потрібні дані. При цьому не вимагається жорсткої послідовності дій, треба стежити тільки за тим, щоб керуюче слово даного каналу посилалося до посилки першого байта константи інформації.

Оскільки розмір даних, що записуються у порт обмежується 1 байтом, то запис даних більшого об’єму виконується у відповідності з вказівками керуючого слова.

Таймеру відповідають 4 порти вводу/виводу з наступними адресами: 40h - канал 0; 41h - канал 1; 42h - канал 2; 43h - керуюче слово. Призначення бітів керуючого регістру (керуючого слова) наступне:

0: 0 – двійкові дані; 1 - дані в формі BCD (двійково-десяткові)

1-3: номер режиму: 000 – режим 0 (переривання термінальної лічби); 001 – режим 1 (програмуємий чекаючий мультивібратор); X01 – режим 2 (програмуємий генератор імпульсів); X11 – режим 3 (генератор меандра); 100 – режим 4 (програмно-запускаємий одновібратор); 101 – режим 5 (апаратно-запускаємий одновібратор)

5-4: тип операції: 00 – передати значення лічильника в буфер (читання на льоту); 01 – читати/писати тільки старший байт; 10 – читати/писати тільки молодший байт; 11 – читати/писати спочатку молодший байт потім – старший;

7-6: номер каналу: 00 – канал 0; 01 – канал 1; 10 – канал 2; 11 – код команди RBC ("зворотне читання").

Молодший розряд байта визначає формат константи, що використовується для рахування. В двійково-десятковому форматі константа задається в діапазоні 1-9999, в двійковому форматі діапазон рівний 1h-FFFFh.

Для визначення поточного значення регістру лічильника можна використати просте читання (читання з портів 40h-42h), але на час читання повинен бути заблокований сигнал CLK або встановлений GATE=0 для зупинення рахування, інакше вміст лічильника може бути змінений при читанні.

При читанні вмісту лічильника каналу "на льоту", тобто без зупинки процесу рахування, необхідно в 43h порт послати керуюче слово, призначення бітів якого наступне:

7-6: задають номер каналу (0, 1, 2);

5-4: містять нулі - код даної команди.

Інші біти не мають значення і керуюче слово не завантажується в регістр PSW (тобто не міняється режим роботи каналу), по ньому тільки запирається вміст CE в вихідному регістрі OL і може бути прочитаний через порт 40h+N (де N - номер каналу) по правилу, що задається розрядами 5 і 4 регістру PSW. При читанні двох байт (код 3h) після читання першого (молодшого) байта можливі операції запис/читання інших каналів.

"Зворотне читання" дозволяє визначити поточний стан регістрів CE вибраних одного, двох або всіх трьох каналів і/або визначити стан (режим роботи, тип рахування, код читання/запису, признак перезавантаження констант, стан сигналу OUT) на час виконання команди.

Для виконання "зворотного читання" необхідно в порт 43h записати керуюче слово, призначення бітів якого наступне:

0: повинен бути рівний 0;

1: CNT0, вибір нульового каналу при CNT0=1;

2: CNT1, вибір першого каналу при CNT1=1;

3: CNT2, вибір другого каналу при CNT2=1;

4: STATUS, запирається стан каналів, визначених в 1-3 розрядах при STATUS=0;

5: COUNT, запирається поточний стан лічильників (регістрів CE) каналів, визначених в 1-3 розрядах при COUNT=0;

6-7: код команди "зворотне читання". Обидва біти повинні дорівнювати одиниці.

Як при "читанні на льоту" дане керуюче слово не записується в регістр PSW і не міняє режимів роботи каналів. Читання запертих значень каналів, означених в розрядах 1-3, виконується з портів 40h-42h.

При цьому якщо в керуючому слові "зворотного читання" обидва біти STATUS і COUNT (4-й і 5-й) рівні нулю і, наприклад, біт 3-й (CNT2) рівний одиниці (вибраний другий канал), то при першому читанні з 42h порту прочитається заперте слово стану каналу, а при двох наступних читаннях з того ж 42h порту - молодший і старший байт запертого регістру CE. Формат (значення бітів) прочитаного слова стану наступний:

0: тип рахування (0 – двійковий, 1 – двійково-десятковий BCD);

1-3: код режиму роботи;

4-5: код читання/запису констант рахування;

6: ознака перезавантаження (0 – константа завантажена в CE, 1 – не завантажена);

7: стан вихідного сигналу (0 – OUT=0, 1 – OUT=1).

Генерація звуків і музики

Звуки і музику на ПЕОМ можна відтворювати двома засобами: з використанням таймера; без використання таймера.

В будь-якому випадку при надходженні на динамік електричного сигналу деякого рівня відбувається втягнення мембрани динаміка, а при зміні рівня електричного сигналу - виштовхування. Таким чином періодичний електричний сигнал викликає вібрацію мембрани динаміка, тобто генерацію звука тієї же частоти.

Відзначимо, що в усіх моделях IBM, за винятком IBM PCjr, що має (окрім динаміка) спеціальний звуковий генератор, гучність звука не змінюється.