- •Организация ввода-вывода.

- •Принцип записи информации на магнитный носитель.

- •Методы записи цифровой информации.

- •Логические основы обработки информации.

- •Электрические сигналы

- •Применение логических элементов.

- •Дешифраторы.

- •Мультиплексоры.

- •Триггеры.

- •Асинхронные однотактные rs- триггеры.

- •Синхронный однотактный rs-триггер

- •Двухтактные триггеры

- •Регистры.

- •Сдвигающие регистры.

- •Счетчики.

- •Многоразрядные счетчики

- •Суммирующий многоразрядный счетчик

- •Микросхемы памяти.

- •Внешние устройства информационных систем. Устройства отображения информации.

- •Функциональный (координатный) метод формирования изображения.

- •Растровый метод формирования изображения.

- •Структурная схема видеомонитора мс 6105.

- •Устройства вывода информации.

- •Классификация печатающих устройств.

- •Устройства вывода текстовой информации.

- •Неполноматричное знакосинтезирующее устройство.

- •Лазерный принтер

- •Струйные принтеры.

- •Копировальные аппараты.

- •Ввод информации.

- •Устройства ручного ввода информации.

- •Устройства ввода графической информации.

- •Ввод информации с оптических дисков.

- •Внешние запоминающие устройства.

- •Узлы накопителей на магнитных дисках.

- •Литература.

Синхронный однотактный rs-триггер

При распространение сигналов в сложных схемах возможны случаи когда информационные сигналы поступают на входы триггера в различные моменты времени, что приводит к ложным срабатываниям триггера, а, следовательно, к ошибкам в работе последующих схем.

Процесс задержки сигналов при их распространение на различные отрезки времени называется эффектом «гонок».

Для устранения влияния эффекта «гонок» на работу логических схем применяют синхронизацию работы различных узлов, т.е. специальным сигналом определяется момент времени, когда следует принять информацию. С этой целью, например, в триггер вводят дополнительный вход – синхронизирующий. Пока на этом входе пассивный уровень напряжения триггер не воспринимает информационные сигналы. Только в момент установки на синхронизирующем входе активного уровня напряжения триггер реагирует на информационные сигналы и устанавливается в соответствующее состояние. Активным является низкий или высокий уровень напряжения в зависимости от особенностей схемы.

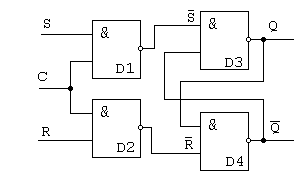

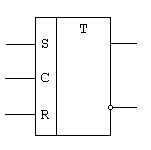

Для построения синхронного триггера к асинхронному триггеру D3, D4 ( Рис.32) добавляют входную логику D1, D2. Дополнительное инвертирование входных сигналов элементами D1 и D2 делает входы триггера прямыми.

Р ис.

32. Электрическая схема и условное

графическое обозначение однотактного

синхронного триггера.

ис.

32. Электрическая схема и условное

графическое обозначение однотактного

синхронного триггера.

.

При пассивном уровне сигнала (НУН) на выходах элементов D1 и D2 устанавливаются высокие уровни напряжения, которое переводит триггерную ячейку D3D4 в режим хранения информации. Изменение информационных сигналов S и R при этом не изменяют состояние триггера.

Для переключения синхронного триггера необходимо активизировать вход синхронизации (подать высокий уровень напряжения). При этом возможно два случая:

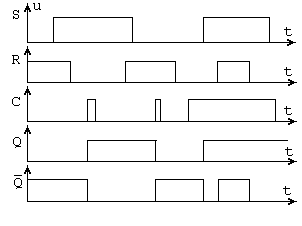

Если сначала устанавливаются определенные информационные сигналы S и R, а затем подается высокий уровень напряжения на вход синхронизации C, то триггер переключается синхронно в момент изменения синхросигнала.

Если сначала установить высокий уровень напряжения на входе C, а затем изменить информационные сигналы, то триггер переключается асинхронно в моменты изменения информационных сигналов.

Рис. 33. Временные диаграммы, поясняющие работу однотактного синхронного RS-триггера.

Двухтактные триггеры

При применении однотактного синхронного триггера нельзя его выходные сигналы использовать для управления этим же триггером, так как это приводит либо к возбуждению схемы, либо схема не реагирует на входной сигнал.

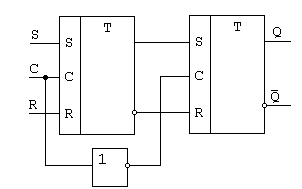

Кроме того, для надежного хранения бита (единицы) информации целесообразно использовать двухступенчатые схемы (триггеры), в которых битах записывается сначала в одну триггерную ячейку, а затем переписывается в другую, что исключает сквозную передачу информации по схеме. Такие триггеры работают за два такта сигнала синхронизации.

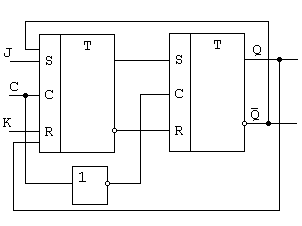

Рис. 34. Электрическая схема двухтактного синхронного RS-триггера, построенного на однотактных синхронных RS-триггерах и его условное графическое обозначение.

При низком уровне сигнала синхронизации первая ступень находится в режиме хранения информации и сигналы на входах S и R не воспринимает. В это время на входе синхронизации второй ступени действует ВУН и вторая ступень принимает сигналы с выходов первой.

Если на вход синхронизации триггера подать высокий уровень напряжения, то вторая ступень переходит в режим хранения (C2 = 0) и не воспринимает информационных сигналов. Первая же ступень переключается в состояние, определяемое сигналами на ее информационных входах S и R. Когда на синхровходе триггера устанавливается низкий уровень напряжения первая ступень переходит в режим хранения информации, а вторая (поскольку С2 = 1) переписывает информацию из первой ступени. Выходные сигналы первой ступени являются информационными сигналами для второй ступени.

Таким образом, для переключения всего триггера необходимо двойное изменение сигнала синхронизации (два такта), что обеспечивается подачей на вход синхроимпульса. Двухтактный триггер не имеет неопределенного состояния.

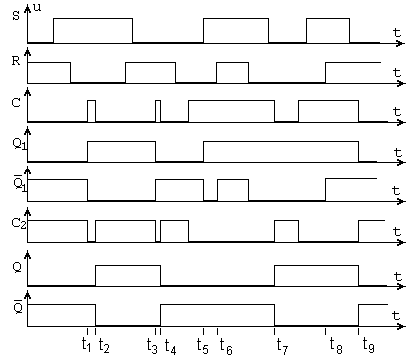

Рис. 35. Временные диаграммы, поясняющие работу двухтактного синхронного RS-триггера.

В приведенных временных диаграммах (Рис. 35) на отрезке времени 0 – t1 установлены определенные уровни входных информационных сигналов S и R. Затем, в момент времени t1, подан высокий (активный) уровень напряжения на синхронизирующий вход С. В этот момент входная информация записывается в первую ступень триггера, а вторая ступень переключается сигналом С1 в режим хранения и не реагирует на изменение состояния первой ступени. В момент времени t2 изменение сигнала синхронизации С1 переключает первую ступень в режим хранения информации, а вторая ступень воспринимает информацию с выходов первой ступени и переключается в единичное состояние. Аналогично работает триггер на отрезке времени t2 – t4. В момент t5 первая ступень воспринимает входную информацию, а в момент t6 входные информационные сигналы S и R переводят первую ступень в неопределенное состояние, однако из-за тог, что на синхровходе второй ступени действует низкий (пассивный) уровень напряжения, вторая ступень остается в режиме хранения предыдущего состояния. На момент времени t7 неопределенное состояние первой ступени сменилось на единичное, поэтому в момент t7 вторая ступень переходит в то состояние, которое на этот момент времени имеет первая ступень, т.е. в единичное. Аналогично работает триггер на отрезке времени t7 – t9.

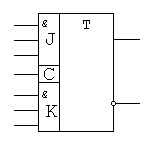

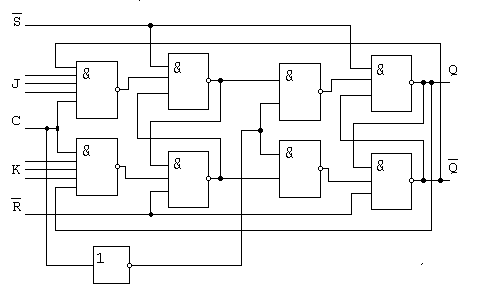

Двухтактный синхронный RS-триггер, имеющий внутренние обратные связи (прямой выход соединен со входом R, а инверсный – со входом S) и разветвленную входную логику называется JK-триггером. Рис. 36.

Вход J – аналогичен входу S, а вход K – входу R. Несколько входов J(K) объединены функцией И (&), следовательно, только при активных уровнях на всех входах J(K) триггер может переключаться в единичное (нулевое) состояние при подаче синхроимпульса.

Рис. 36. Условное графическое обозначение и электрическая схема JK-триггера.

D-триггер.

Одним из недостатков RS-триггера является двух информационных входов, на которые необходимо подавать два сигнала противоположных по уровню. Если имеется только один информационный сигнал, то в схему необходимо вводить инвертор.

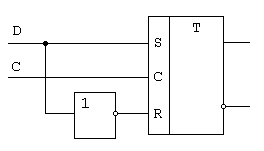

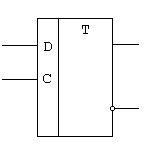

D-Триггер строится на базе синхронного RS-триггера, у которого входы S и R соединены через инвертор (Рис. 37).

Рис. 37. Электрическая схема D-триггера, построенного на основе однотактного RS-триггера и его условное графическое обозначение.

В результате получаем триггер с одним информационным входом D(данные). Этот триггер по сигналу синхронизации устанавливается в состояние соответствующее уровню напряжения на входе D. Неопределенного состояния не имеет.

D-триггеры выпускаются в интегральном исполнении и имеют динамический вход синхронизации, т.е. воспринимают информационный сигнал только в момент перепада сигнала синхронизации с высокого уровня на низкий (инверсный вход C) или с низкого уровня на высокий (вход C прямой).

Во всех остальных случаях триггер находится в режиме хранения информации. Примером D-триггера в интегральном исполнении является микросхема К155TМ2.

Д инамический

вход синхронизации триггера обозначается

так как показано на рисунке 38.

инамический

вход синхронизации триггера обозначается

так как показано на рисунке 38.

Рис. 38. Условное графическое обозначение триггеров с динамическим входом синхронизации.

JK- и D - триггеры в интегральном исполнении имеют как правило дополнительные входы независимой установки S, R, которые позволяют переключить триггер асинхронно независимо от уровня сигнала синхронизации. Пример построения двухтактного триггера с входами независимой установки показан на рисунке 39.

Рис. 39. Полная электрическая схема JK-триггера со статическим входом синхронизации и входами независимой установки.