лекции ВТиИТ / 05_Архитектура ЭВМ, процессор, режимы работы

.pdf

|

Архитектура ЭВМ |

|

||

Любой процесс вычисления можно разбить на следующие этапы: |

|

|||

– определение и задание порядка вычисления; |

|

|||

– задание исходных данных; |

|

|

||

– вычисление; |

|

|

|

|

– вывод данных (получение конечного результата). |

|

|||

|

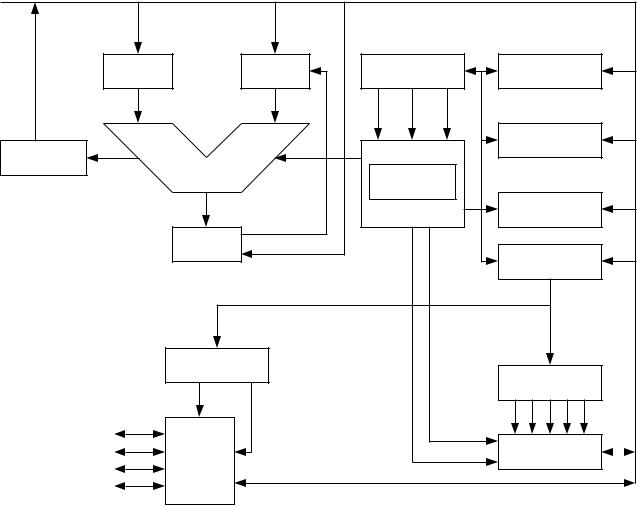

Обобщенная структурная схема |

|

||

|

|

Пульт управления |

|

|

процессор |

|

|

|

|

|

Устройство управления |

|

||

|

|

|

АЛУ |

|

|

|

ПАМЯТЬ |

|

|

Данные, код |

Устройство |

Оперативная |

Устройство |

|

программы |

ввода |

вывода |

||

|

||||

|

|

Внешняя |

|

|

|

Принципы программного управления |

|

||

1.Любой алгоритм приводится в виде последовательности управляющих команд. Каждая команда определяет простой шаг преобразования информации;

2.Принцип условного перехода;

3.Принцип хранимой программы. Любая программа представляет собой набор команд, которые хранятся как данные (без определенной команды нельзя определить команда это или данные);

4.Принцип двоичного кодирования;

5.Принцип иерархии запоминающих устройств.

Классификация процессоров

По области применения:

1.Процессоры встраиваемых систем

–универсальные;

–с расширенными коммуникационными возможностями;

–с расширенными дискретными вводами и выводами;

–с возможностью обработки аналоговых сигналов.

2.Коммуникационные процессоры (поддержка сетевых интерфейсов и протоколов)

–сетевые (Ethernet)

–модемные

3.Процессоры цифровой обработки сигналов (небольшой набор команд, высокое быстродействие)

4.Медийные процессоры (аудио-, видео-адаптеры)

5.Сопроцессоры (математические)

6.Транспьютеры

7.Другие типы

–нейтропроцессоры построения нейтронных сетей

–узкоспециализированные процессоры

По полноте вычислительного ядра:

1.Сопроцессоры (арифметические)

2.Полнофункциональные

3.С расширенной периферией

4.Однокристальные микро ЭВМ

5.Однокристальные мультимедийные системы

По архитектуре вычислительного ядра:

По разрядности ядра

–типовые кратности 4, 8, 16, 32, 64

–нетиповые – разрядность, не кратная восьми

–масштабируемые (масштабность наращивается блочно)

По организации памяти:

1.С архитектурой фон-Неймана (Машины фон-Неймана хранят программу и данные в одной и той же области памяти. В машинах этого типа команды содержат указание, что выполнить, и адрес данных, подлежащих обработке.)

2.С Гарвардской архитектурой (Единственное отличие гарвардской архитектуры состоит в том, что память программ и память данных разделены, и они используют физически разделенные линии передачи.)

По системе команд:

1.CISC архитектура (компьютер с полным набором инструкций, разные команды имеют разные длины, скорости обработки)

2.RISC (система с сокращенным набором команд)

По уровню распараллеливания процесса

–суперскалярный (процессор сам определяет набор команд )

–с внешним командным символом

–мультискалярные (распараллеливание на отдельные информационные блоки)

Однопроцессорные ЭВМ

Микропроцессорная система – это микропроцессор и дополнительные устройства, выполняющие вспомогательные для МП функции.

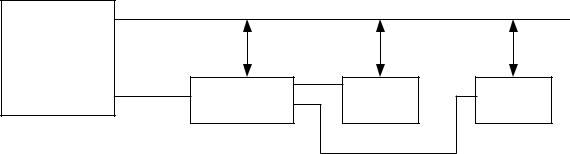

Магистрально – модульная структура построения Трехшинная структура

AB адресная шина

CPU |

ROM |

|

RAM |

|

I/O ports |

|

|

|

|

|

|

DB шина данных

СB шина управления

Возможно мультиплексирование шин адреса (AB) и шины данных (DB) по времени – двухшинная организация (есть шина управления CB и мультиплексированная шина адреса/данных – A/DB)

Двухшинная организация

Работает медленнее

A/D B - шина адреса и управления

CPU

СВ

ALE разрешение на защелки адреса

RG A Регистр адреса

I/O, RAM

Структура процессора

КОП (код операции) Устройство

управления

Vi |

|

Si |

|

||

|

|

|

|

|

|

Операнды

АЛУ

Vi – множество управляющих сигналов

Si – множество сигналов, определяет выполняемую операцию Арифметическо-логическое устройство (АЛУ) –

(может выполнять операции «сложение», «вычитание», «И», «ИЛИ», «сравнение», «инкремент», декремент»)

Устройство управления (УУ) – для выработки управляющего сигнала, обработки, управления системным интерфейсом.

|

Устройство управления |

|

С микропрограммной логикой |

|

|

|

ШД |

|

|

|

Si от |

|

RG команд |

АЛУ |

|

|

|

|

RG адреса микрокоманд |

|

ГТИ |

Постоянное запоминающее |

|

|

|

|

|

устройство (МПЗУ) |

|

|

RG микрокоманд |

|

|

Vi |

|

|

АЛУ |

|

Каждая команда выполняется как программа, записанная в МПЗУ. Команда поступает из шины данных в регистр команд, который формирует начальный адрес микрокоманды. Регистр адреса микрокоманд выбирает из ПЗУ команду и записывает в регистр микрокоманд

– формируется сигнал управления для АЛУ.

Микрокоманда может содержать адреса других микрокоманд, для дальнейшего выполнения микрокоманд.

ГТИ – генератор тактовых импульсов служит для синхронизации работы блоков. Достоинство: гибкость структуры, возможность обновления микрокоманд в МПЗУ.

С жесткой логикой

RG команд

ДШК

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ADD |

|

SUBS |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

КС |

|

|

|

ДШ |

|

|

СУ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Si |

|

|

|

|

|

|

|

|

ГТИ |

|||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

Такт |

|

|

Такт |

|

|

|||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Vi

ДШК – дешифратор команд КС – комбинационная схема

Повышается быстродействие (т.к. нет ячейки памяти), но жесткая структура. ГТИ задает последовательность выполнения команд путем выработки на дешифратор тактов последовательности тактовых сигналов. ДШ определяет часть комбинационной схемы, на которую поступает управляющий сигнал от дешифратора тактов.

|

|

АЛУ |

|

n |

|

|

|

|

n |

|

|

|

RG А Прямой |

|

|

|

n |

|

RG В |

|

|

|

|

|

|

|

n |

|

RG А Инверсный |

|

|

|

n |

|

|

RG Признаков |

|

|

|

|

|

n |

|

Si в АЛУ |

|

|

n |

|

|

n |

|

|

|

Аккумулятор |

|

|

|

|

Операнды помещаются в регистры А и В. Основой является сумматор. Аккумулятор – регистр, хранящий значение результата. Инверсный регистр А используется при операциях вычитания.

В RG признаков – помещаются признаки выполнения операций (результат >0, <0, =0, перенос (С) единицы из старшего разряда, промежуточный перенос, переполнение).

|

Общая структура процессора |

|

|

||

|

|

Регистры процессора |

|

|

|

|

|

|

|

|

ШД |

RG A |

|

RG B |

RG Команд |

Счетчик |

|

|

команд |

|

|||

|

|

|

|

|

|

|

|

|

|

Указатель |

|

RG |

|

|

УУ |

стека |

|

Состояний |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

КС, МПЗУ |

|

|

|

|

|

|

Р.О.Н. |

|

|

AК |

|

|

RG Адрес |

|

|

|

|

|

|

|

|

|

|

|

памяти |

|

|

|

ША |

|

|

|

|

|

|

ШУ |

ША |

|

|

|

|

|

|

|

|

ДШ портов |

|

|

|

|

|

|

|

|

ДШ адреса |

|

|

Порты |

|

запись |

|

ШД |

линии |

ШД |

чтение |

Запоминающее |

||

ввода/ |

ввода/ |

устройство |

|

||

|

|

||||

|

|

|

|

|

|

вывода |

вывода |

|

|

|

|

|

|

|

|

|

|

Аккумулятор (АК): Используется при операциях с АЛУ, при действиях над данными в аккумуляторе, при пересылке данных (порт ввода, вывода, память).

Регистр команд: Хранит текущую выполняемую команду Регистр признаков (состояний): Содержит признаки результатов вычислений АЛУ (см. выше).

Регистр адреса памяти: Содержит адрес в области памяти, которая будет использоваться. Данные поступают из счетчика команд, или другого регистра произвольно или в результате вычислений (содержимое Сч.К+смещение).

Счетчик команд: Содержит адрес команды, которая должна быть выполнена в следующий момент. При старте системы в Сч.К. записывают начальный адрес программы (где находится первая команда программы) Потом этот адрес посылается в регистр адреса памяти. Команда из памяти по этому адресу считывается в Рг.команд. После декодирования команды содержимое Сч.К. увеличивают на 1, т.е. в Сч.К. будет находится адрес следующей команды. Указатель стека: Стек – область памяти, которая организована по принципу LIFO (последний зашел, первый вышел). Доступ к ячейкам стека выполняется с помощью указателя стека. Указатель стека указывает на первую свободную ячейку.

Регистр состояния (признаков): Содержит признаки результата вычислений АЛУ.

Регистры общего назначения (РОН): Используются при выполнении программ, доступны при программировании, могут образовывать регистровые пары.

Команды процессора

Команда сообщает процессору, какую операцию необходимо выполнить и где находятся данные для операции.

Любая команда состоит из двух частей: код операции (КОП) + адрес.

Команды представляются в двоичном виде (неудобно для программиста) => используют мнемоническую запись (JMP, MOV, ADD, INC …)

Способы адресации:

Неявная адресация.

Данные находятся не в основной памяти (регистры общего назначения). Адреса источника и приемника входят в саму команду.

Пример: MOV C, D (перемещение данных из регистра D в регистр С). 1-байтовая команда.

Непосредственная адресация.

Данные находятся в теле команды. 1Б – код операции; 2Б – данные; 3Б – данные.

Не требуется адрес памяти, где находятся данные

Прямая адресация.

1Б – код операции;

2Б – адрес;

3Б – адрес.

В байтах 2 и 3 находится адрес памяти, по которому находятся обрабатываемые данные.

Косвенная адресация.

КОП+РОН 1-байтовая команда, в РОН находится адрес данных в памяти. Перед использованием в РОН заносят адрес.

Типы команд

1.Команды передачи данных

–команды обмена данными между регистрами внутри процессора (регистровые пересылки)

MOV r1,r2 – перенести данные из регистра r1 в r2

–команды обмена процессора с памятью

ST (store) – сохранить в память (STA A,M – сохранить данные из аккумулятора в ячейку памяти по адресу М)

LD (load) – считать данные из памяти в регистр (LDD r,M – считать данные из ячейки памяти по адресу М в регистр r)

LDA r,данные – занести данные в регистр r

–команды обмена процессора с периферийными устройствами (имеющими свое адресное пространство)

IN, OUT

2.Команда обработки данных

–арифметические команды

Сложение

ADD r (сложить данные из аккумулятора с данными из регистра r и поместить результат в аккумулятор: A + r → A)

ADD M (сложить данные из аккумулятора с данными из ячейки памяти по адресу М и поместить результат в аккумулятор: A + M → A)

Вычитание

SUB r (A – r → A) SUB M (A – M → A)

Инкремент INC r (r + 1 → r) Декремент DEC r (r – 1 → r)

–логические команды – выполняются над аккумулятором и регистром Логическое И AND r (A & r → A)

Логическое ИЛИ OR r (A + r → A) Сравнение CMP r

–команды сдвига

Циклический сдвиг аккумулятора влево – RAL, вправо – RAR

3.Команды управления

–команды перехода

безусловный переход по адресу: JMP М (М – адрес)

условный переход по адресу (анализируется регистр признаков): JZ M – переход, если в регистре признаков есть индикация 0 JNZ M – переход, если в регистре признаков нет индикации 0 JN M – переход, если в регистре признаков есть индикация < 0 JNN M – переход, если в регистре признаков есть индикация > 0

– вызов подпрограмм

безусловный вызов подпрограммы по адресу: CAL М (М – адрес)

условный вызов подпрограммы по адресу (анализируется регистр признаков): CZ M – вызов подпрограммы по адресу, если в регистре признаков есть индикация 0

CNZ M – вызов подпрограммы по адресу, если в регистре признаков нет индикации 0

выход из подпрограммы: RET

Режимы работы процессора

Программный режим

Процессор является активным устройством, управляющий всеми основными блоками, реализуется машинный цикл, который состоит из 2-х частей:

–выборка. Из счетчика команд берется адрес команды, заносится в регистр адреса памяти, из памяти считывается команда и заносится в регистр команды, после этого счетчик команд увеличивает свое значение на единицу.

–выполнение команд. Из регистра команд команда попадает на дешифратор команд устройства выполнения, вырабатывается сигнал управления для АЛУ.

Режим обращения к подпрограммам

|

|

|

|

|

|

|

|

|

|

|

стек |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А1 |

|

B1 |

|

C1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

А2 |

|

B2 |

|

|

|

|

|

|

|

|

|

|

|

C2 |

|

|

|

|

|

||

|

|

А3 |

|

B3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

C3 |

|

|

|

|

|

||

|

|

… |

|

... |

|

Указатель |

|

||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

||

|

|

Аi CALL |

|

Bi CALL |

|

|

стека |

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

Ai+1 |

|

B i+1 |

|

… |

|

|

|

|

|

|

|

|

|

|

|

|

|

Вi+1 |

|||

|

|

… |

|

… |

|

|

|

|

|

||

|

|

|

|

Return |

|

|

|

|

|

||

|

|

|

|

Return |

|

|

|

|

|

Аi+1 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сч.К |

Аi+1 |

Сч.К |

Вi+1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Программа – это последовательность команд. Пусть при выполнении программы А произошел вызов (CALL) подпрограммы В. При этом в специальную область памяти, называемую стеком, заносится содержимое счетчика команд (Сч.К.), значения РОН, Рг.Признаков на момент выполнения вызова подпрограммы В. Далее выполняется

подпрограмма В. Если при выполнении подпрограммы В была вызвана подпрограмма С, то в стек также заносится содержимое счетчика команд (Сч.К.), значения РОН, Рг.Признаков на момент выполнения вызова подпрограммы С. После выполнения подпрограммы С по команде Return происходит считывание содержимого счетчика команд (Сч.К.), значения РОН, Рг.Признаков для восстановления состояния системы для выполнения подпрограммы В. Аналогично происходит и при возвращении в программу А. Указатель стека используется для перемещений между ячейками стека.

Работа с прерываниями

При запросе от внешнего устройства (прерывания) процессор заканчивает выполнение текущей команды и выполняет действие, аппаратно реализованного вызова подпрограммы обслуживания прерывания (также записывается в стек счетчика команд, регистр общего назначения) в счетчик команд записывается команда подпрограммы обработки прерывания (подпрограмма работы с устройством, вызвавшим прерывание).

Различают прерывания по важности. В тексте программы существуют участки запрета прерываний, после этого участка вставляется команда разрешения прерывания (маскирование прерываний). Однако, есть так называемые не маскируемые прерывания – их нельзя запретить. Сигналы от них поступают на специальные входы процессора. Прерывания могут приходить от разных устройств – необходимо определять, от какого устройства пришло прерывание. Используют три основных способа:

–векторный способ Процессор имеет число входов для приема прерывания = числу устройств. При поступлении на определенный вход прерывания вызывается подпрограмма обработки прерывания от этого устройства. Каждое прерывание имеет свой вектор, по вектору определяют начальный адрес подпрограммы обработки прерываний. Недостатком является большое число входов.

–радиальный используется внешнее устройство – контроллер, который осуществляет распределение приоритетов прерываний от устройств.

|

Шина данных |

|

|

|

CPU |

|

|

|

|

|

Контроль |

IRQ |

|

|

IRQ |

ВУ |

ВУ |

||

прерываний |

||||

|

||||

|

|

|

||

|

|

IRQ |

|

Контроллер выставляет запрос CPU и выставляет вектор прерываний (адрес подпрограммы) на шину данных. Процессор избавляется от лишней работы, меньше число выводов, возможно наращивать.

– режим опроса. Все устройства соединяются одной шиной с входом прерывания процессора, и при выставлении прерываний запускается программа опроса всех возможных источников прерываний. После определения источника запроса прерывания, запускается программа обработки прерывания. Более медленный способ, но можно гибко реализовать программно.

Режим прямого доступа к памяти

Программно-управляемая пересылка данных (между устройством ввода/вывода, памятью) выполняется через аккумулятор чередованием команд записи из порта в аккумулятор и из аккумулятора в память. Вызывает большие накладные расходы, выполняется очень медленно. Используется режим прямого доступа к памяти, реализуется с помощью контроллера.

Данные напрямую передаются в ОЗУ посредством контроллера прямого доступа. Во время режима ПДП процессор лишен возможности обращения к памяти.

|

Возможно |

|

||

|

программирование |

|

||

Микропроцессор |

|

|

Контроллер |

|

|

|

|||

Состояние |

прямого доступа |

|||

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

е |

|

|

|

|

|

|

|

и |

|

|

|

|

|

|

|

н |

|

|

|

|

|

|

|

е |

|

|

|

|

|

|

|

л |

|

|

|

|

|

|

|

в |

|

|

|

|

|

|

|

а |

|

|

|

|

|

|

|

р |

|

|

|

|

|

|

|

п |

|

|

|

|

|

|

|

|

У |

|

|

|

|

|

|

|

|

Управление

ОЗУ |

|

Данные |

Устройство |

|

|

ввода/вывода |

|

|

|

|

|

|

|

|

|

Обмен данными между устройствами может быть реализован в следующих режимах:

1.Блочная передача. В этом режиме процессор останавливается на все время передачи блока данных и ожидает, пока устройства обмениваются информацией. Устройства выполняют монопольный захват шины данных.

2.Мультиплексный режим (режим одиночных передач) – обмен данными происходит в промежутках, когда шина данных не используется процессором (например, в машинном цикле есть этап декодирования команды, когда системные шины не используются).

|

Шина данных |

|

ОЗУ |

КПДП |

ВУ |

ЦП |

|

|

|

|

Шина адреса |

|

Шина управления |

|

Захват шин |

|

|

Подтверждение захвата шин |

|

|

Обмен информацией между ВУ и ОЗУ выполняется с помощью КПДП – контроллера прямого доступа к памяти.

Контроллер прямого доступа к памяти (КПДП) включает в себя следующие регистры:

1.Регистр состояния, в котором указывается: тип режима передачи (блочный/мультиплексный), готовность к передаче, окончание передачи данных, наличие запросов(прерываний) от ВУ на передачу данных)

2.Регистр начального адреса (содержит адрес, с которого следует записывать данные в устройство-приемник)

3.Регистр – счетчик пересылок, содержит число байт подлежащих пересылке

Режим прямого доступа осуществляется следующим образом:

Перед обменом из ВУ процессор считывает начальный адрес и объем данных, которые необходимо передать в ОЗУ, эти данные записываются соответственно в регистр начального адреса и в счетчик пересылок КПДП.

КПДП выставляет сигнал «захват шин». Процессор отключается от системных шин (переводит выводы микросхемы в Z-состояние) и выставляет сигнал «подтверждение о захвате шин». После этого осуществляется обмен данными между внешним устройством (ВУ) и ОЗУ под управлением КПДП. КПДП последовательно подает на адресную шину памяти микропроцессорной системы адреса и вырабатывает сигналы управления чтением и