лекции ВТиИТ / 03_ПЛМ-ПЛИС

.pdf

Программируемые логические матрицы, программируемые логические интегральные схемы

Программируемые логические матрицы (ПЛМ) и программируемые логические интегральные схемы (ПЛИС) – это микроэлектронные приборы (микросхемы), содержащие много (иногда тысячи) логических элементов (ЛЭ) и других компонентов, входят в довольно многочисленную группу программируемых логических приборов (ПЛП). Это так называемые «стандартные полуфабрикаты» (интегральные микросхемы – ИМС). Выпущенные изготовителем, эти ИМС не могут выполнять никаких операций. ЛЭ и компоненты расположены в них в определенном порядке – матрицами, блоками, группами и др. Чтобы они могли выполнять необходимые логические операции, нужно провести заключительную операцию – программирование, которое осуществляется пользователем (конструктором), т.е. на месте потребления без участия изготовителя. При программировании имеющиеся в «полуфабрикатах» ЛЭ организуются в специальные логические структуры, выполняющие заданные логические функции (любой сложности). Это

– главная сущность группы ПЛП.

Это относительно новое направление в микроэлектронике, развивающееся быстрыми темпами. Оно является следствием быстрого роста сложности электронных систем, требующих применения высоко интегрируемых узкоспециализированных ИМС (СИС и БИС). Разработка и изготовление таких микросхем – длительный и дорогостоящий процесс, который экономически оправдан только при большом объеме выпуска (более 10 000 штук в год). При малой потребности более выгодно изготавливать упомянутые выше «полуфабрикаты» ИМС и специализировать (программировать) их в сфере потребления. В настоящее время разработано и выпускается много разновидностей (более сотни) программируемых потребителями микросхем различной степени сложности. Четкая классификация таких микросхем (приборов) пока не установилась. Будем называть их обобщенно – программируемые логические приборы (ПЛП). Несомненно одно: применение ПЛП постоянно расширяется, сложность их повышается. Рассмотрим наиболее распространенные разновидности таких приборов – ПЛМ и ПЛИС.

Программируемые логические матрицы

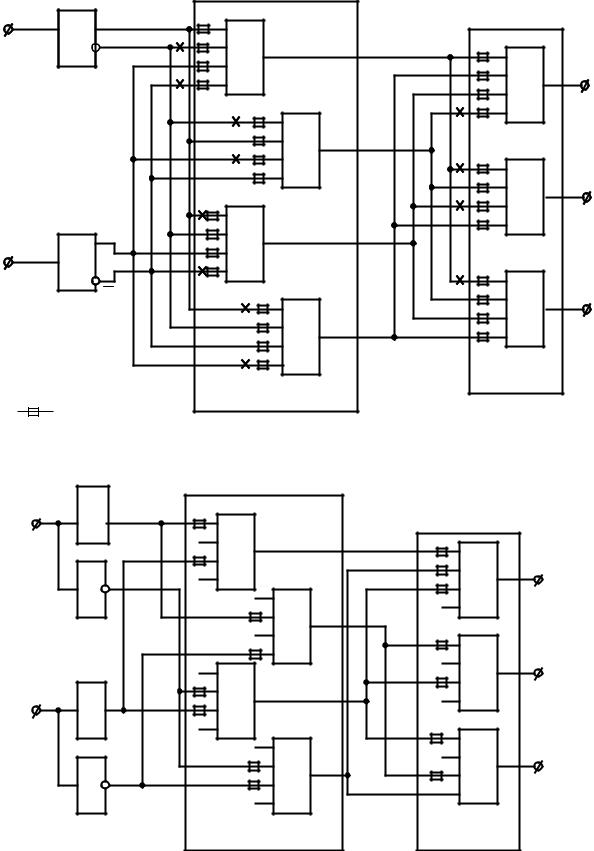

ПЛМ – наиболее распространенная и наиболее известная разновидность ПЛП, одна из первых микросхем этого типа. ПЛМ представляет собой комбинационное устройство, включающее в себя две матрицы ЛЭ (или одну), расположенных на кристалле микросхемы. Это – своего рода интеграция ЛЭ. Соединение этих ЛЭ в определенные логические схемы, выполняющие заданный набор логических функций, производится разработчиком аппаратуры. Это и есть программирование, которое превращает «полуфабрикат» в законченное специализированное изделие. Из одинаковых «полуфабрикатов» ПЛМ при помощи программирования можно получать различные логические схемы для выполнения любых логических функций, определяемых потребителем. Одна ПЛМ может заменить десятки и сотни микросхем ЛЭ малой степени интеграции. Основу ПЛМ составляют две ступени логических элементов и входные ячейки (инверторы-повторители). Первая ступень представляет собой матрицу ЛЭ типа И (конъюнкторов), вторая ступень – матрицу элементов ИЛИ (дизъюнкторов).

Выходные функции Fi задаются потребителем в виде дизъюнктивной нормальной формы (ДНФ, см. приложение) – дизъюнкции конъюнкций. Элементы первой ступени B3, …, B6 образуют логические произведения (конъюнкции, импликанты, термы) входных

сигналов A, B, … и их инверсий А , В , … Элементы второй ступени (матрицы ИЛИ) B7, B8, B9 объединяют заданным порядком (выполняют дизъюнкции) конъюнкции в выходные функции Fi. Дизъюнкция конъюнкций – это один из вариантов получения алгебраического

выражения логической |

функции |

F по таблице истинности. |

К дизъюнкции конъюнкций |

(ДНФ) можно свести все логические функции. |

|

||

На рисунке 1, а |

приведена |

разновидность ПЛМ с |

плавкими перемычками (до |

программирования) – один из самых распространённых способов осуществления

программирования ПЛМ. Каждый из входных сигналов (A, B, …) и их инверсий ( A , B , ...) соединяется с одним из входов всех схем И через плавкие перемычки ( ). Выходы каждого

). Выходы каждого

из конъюнкторов (B3, …, B6) соединяются с входами всех схем ИЛИ (В7, …, В9) тоже через плавкие перемычки ( ). Это и есть полуфабрикат. Он пока не может ничего выполнять. Например, на всех выходах конъюнкторов образуются одинаковые логические произведения

). Это и есть полуфабрикат. Он пока не может ничего выполнять. Например, на всех выходах конъюнкторов образуются одинаковые логические произведения

(термы) А A B B , а на всех выходах дизъюнкторов – одинаковые функции Fi из

четырёх одинаковых термов . К тому же этот терм равен нулю ( A A = 0, B B = 0). Программирование такой ПЛМ производится пережиганием тех перемычек, которые окажутся ненужными для выполнения заданных функций Fi. В результате программирования часть ЛЭ может быть исключена (пережиганием всех плавких перемычек ЛЭ).

Пусть, например, при программировании пережжены перемычки, которые на рис.1, а указаны значком (например, входы 2, 4 вентиля В3). Пережигание перемычек производится программаторами по определённой программе при помощи внешних импульсов тока определённой величины. Логическая схема, которая получилась после пережигания указанных перемычек, приведена на рисунке 2, б. Разорванные перегоревшими перемычками соединения на схеме не показаны, от них остались свободные выводы (например, входы 2, 4 вентиля В3). Непережженные перемычки остались в схеме. На

выходах конъюнкторов приведены образуемые ими термы АВ, AB , A B, A B . На выходах

(1)

(2)

(3)

Как уже указывалось, рассматривается очень упрощённая модель ПЛМ. Главным назначением этого рассмотрения является иллюстрация принципа программирования ПЛМ в доступной форме, поэтому выходные функции (1) – (3) получились элементарно простыми, а практическая ценность их весьма условна. К тому же это полные СДНФ, а не минимизированные (МДНФ). Даже не имея опыта минимизации, можно упростить выходные функции Fi:

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F 0 B AB , |

F1 AB AB , |

F 2 A AB . |

(4) |

||||||||||||

Пусть (4) будут примитивными МДНФ. |

При программировании |

||||||||||||||

«минимизированных» функций (4) логическая схема будет выглядеть ещё более простой (но будет не такой наглядной).

На самом деле при синтезе (при создании) устройства всё происходит в обратном порядке: сначала задаются исходные функции Fi – ДНФ (обычно получаемые из таблицы истинности, словесного описания и др.). Затем они минимизируются. Получаются минимизированные (упрощённые) функции Fi – МДНФ. Минимизацию проводят совместно для всех функций Fi. Как правило, минимизация производится при помощи ЭВМ. И на заключительной стадии производится пережигание перемычек (программирование), чтобы получить на выходах заданные функции Fi (МДНФ).

A |

|

1 |

A |

1 |

& |

|

|

|

|

|

|

|

|

|

2 |

|

|

|

1 |

|

|

||

|

|

B |

A¯ |

3 |

|

|

|

|

|

|

|

|

|

|

AAB¯ B¯ |

|

|

2 |

1 |

|

|||

|

|

|

|

4 |

|

|

|

|

|

||

|

|

|

|

B3 |

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

4 |

B |

F0 |

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B4 |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B8 |

F1 |

B |

|

B |

|

& |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||||

|

1 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

1 |

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

B |

F2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Матрица |

|

||

|

|

|

|

|

|

|

|

|

ИЛИ |

|

|

|

|

|

|

|

Матрица И |

|

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

A |

1 |

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B1 |

|

& |

AB |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

F0 |

|

|

|

|

1 |

A¯ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

B |

|

|

|

& |

AB¯ |

B7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

F1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

1 |

|

|

& |

AB¯ |

|

B8 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B2 |

B |

|

|

|

|

1 |

|

F2 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

B¯ |

|

|

& |

A¯B¯ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

B9 |

|

|

|

|

|

|

|

|

|

|

Матрица |

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Матрица И |

|

ИЛИ |

|

|

|

||

б

Рисунок 1. Программируемая логическая матрица с плавкими перемычками

Разновидности ПЛМ. В результате непрерывного развития и совершенствования разработано и выпускается несколько разновидностей ПЛМ, различающихся по структуре, способам программирования, сложности и др. Некоторые ПЛМ включают в себя до десяти и более тысяч эквивалентных вентилей (двухвходовых вентилей И-НЕ или ИЛИ-НЕ). Число выходных функций (Fi) и входных сигналов (А, В, С, …) достигает десятков, а число термов (конъюнктивных членов) – сотен. Разновидности ПЛМ:

1. Обе матрицы могут быть выполнены на однотипных ЛЭ, например на базовых ТТЛэлементах И-НЕ. Тогда вентили второй ступени (В7, …, В9) будут выполнять функции ИЛИ-

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

НЕ для инверсных термов (АВ, A B , |

|

AB , A B , см. рис. 2, б) – логических |

нулей, и |

|||||||||||||||

выходные функции F0, …, F2 будут точно такими же, как (1) – (3), например: |

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

F1 |

= A |

B |

A B = AB AB . |

(5) |

|||||||||||||

Первое выражение F1 получено для обеих матриц, выполненных на элементах И-НЕ. Затем оно преобразовано по теореме де Моргана ( B A = = A B A B ).

2.Программируемой может быть только одна матрица И (И-НЕ), а матрица ИЛИ при этом имеет фиксированную (непрограммируемую) структуру. Такую структуру имеет микросхема ПМЛ (программируемая матричная логика) – весьма распространённая разновидность ПЛМ.

3.«Полуфабрикат» ПЛМ может состоять из одних матриц ЛЭ без линий соединения. При программировании таких матриц получают специализированный фотошаблон, который используется для нанесения металлизированных соединений.

4.ПЛМ может быть репрограммируемой, т.е. можно стирать старую информацию (систему соединений ЛЭ) и производить новое программирование (ПЛМ с плавкими перемычками – нерепрограммируемая). Более подробно о репрограммируемых ПЛМ – в следующем разделе, поскольку репрограммирование относится не только к ПЛМ.

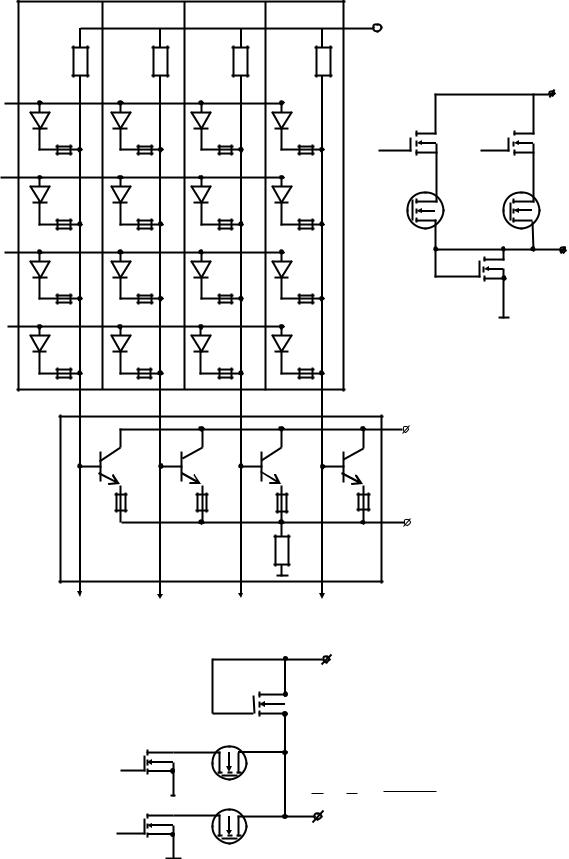

B3 |

B4 |

B5 |

B6 |

|

|

|

|

|

|

+Eп |

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

+Eп |

|

|

|

X1 |

V1 |

X2 |

V2 |

|

|

|

|

|

|

|

|

|

|

И |

|

|

|

|

|

|

матрица |

Vx |

|

Vx |

|

|

|

|

|

||

B |

|

|

|

|

|

|

|

|

|

|

|

V3 |

Y=X1+X2 |

B¯ |

|

|

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

+Eп |

V1 |

V2 |

V3 |

V4 |

|

|

|

F0 |

B7 |

|

|

|

к вентилям B8, B9 |

|

||

|

|

а |

|

|

|

|

+Eп |

|

|

|

V3 |

V1 |

|

Vх |

|

X1 |

|

|

|

V2 |

|

Vх |

Y= X 1 X 2 X 1 X 2 |

X2 |

|

|

|

|

|

в |

|

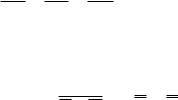

|

Рисунок 2. Реализации матриц И и ИЛИ |

||

Программируемые логические микросхемы

Это обобщающее название микросхем-«полуфабрикатов», из которых получают специализированные ИМС программированием у потребителя. В эту группу входят и рассмотренные ранее ПЛМ. Можно считать, что ПЛИС – это интеграция микросхем.

Замечание. Кроме ПЛИС имеется много других разновидностей «полуфабрикатов», т.е. микроэлектронных изделий, которые выпускаются изготовителем в незаконченном виде. Сюда можно отнести и многочисленные полузаказные изделия. Для придания им законченного, специализированного вида требуется определённая доработка, включающая и программирование потребителем. Весьма показательным в этом смысле является базовый матрический кристалл (БМК), из которого программированием и доработкой получают специализированную матрическую БИС. БМК – это ещё не микросхема, а только кристалл без соединительных линий, не установленный в корпус, а имеющий только контактные площадки для внешних выводов. Основу БМК составляют базовые ячейки (БЯ), в которых расположены различные изолированные друг от друга компоненты: транзисторы, МЭТ, диоды, резисторы и др. Из компонентов одной ячейки или нескольких ячеек могут быть созданы функциональные узлы комбинационного или последовательного типа значительной сложности – макроэлементы. Программирование и окончательное формирование специализированной БИС из БМК продолжается 6 – 8 недель и заканчивается у изготовителя нанесением соединений по изготовленному потребителем фотошаблону (в процессе программирования БИС) и установкой в корпус. Такие «полуфабрикаты» не будем включать в ПЛИС, т.к. они входят в другую группу полузаказных изделий.

Опуская вопрос о классификации «полуфабрикатов» и полузаказных изделий, в пособии ПЛИС рассматривается в более узком смысле. В группу ПЛИС включены такие «полуфабрикаты», которые представляют собой законченную производителем микросхему (в корпусе с выводами и с нанесёнными соединениями) и программирование которых производится потребителем без помощи изготовителя (пережигание плавких перемычек). Программирование ПЛИС производится довольно быстро (от нескольких секунд до нескольких минут) при помощи специальных программаторов. Рассмотренные ранее ПЛМ являются одной из многочисленных (более сотни) разновидностей ПЛИС. В структуру многих разновидностей ПЛИС входят как комбинационные, так и последовательностные (триггер, регистры, счётчики) узлы, а также узлы запоминающих устройств (ЗУ). Различаются ПЛИС и способами программирования.

Способы программирования ПЛИС. Кроме широко используемых плавких перемычек, существуют и другие, более эффективные способы программирования. Это могут быть МНОП-транзисторы, МОП-транзисторы с «плавающим» затвором или двухзатворные МОПтранзисторы. В этих транзисторах проводящий канал индуцируется (наводится) под действием заряда, накапливаемого на границе двух диэлектриков под затвором, или на изолированном (плавающем) затворе при подаче импульса напряжения в процессе программирования. Накопленный заряд сохраняется в течение нескольких лет, обеспечивая необходимые соединения элементов ПЛИС. Перед программированием такие транзисторы переводятся в закрытое состояние (т.е. все соединения разрываются) подачей специального электрического сигнала (такие ИМС называются электрически стираемыми – ЭСПЛИС) или при помощи облучения кристалла ИМС через специальное окно ультрафиолетовым светом (такие ИМС называются стираемыми – СПЛИС). Наиболее перспективными для применения в аппаратуре считаются ЭСПЛИС (например, двухзатворные МОП-транзисторы), так как изменение их конфигурации (перепрограммирование) может быть осуществлено непосредственно в аппаратуре (без извлечения из схемы) в течение времени не более 1 секунды.

Созданы ПЛИС по технологии КМОП статических оперативных ЗУ (СОЗУ). Изменение конфигурации таких ПЛИС может производиться динамически (программно).

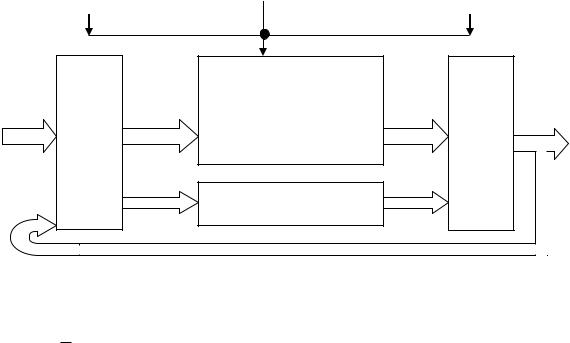

В самом общем виде современные ПЛИС могут быть представлены моделью, приведённой на рис.3, хотя отдельные узлы и блоки разных ПЛИС могут существенно различаться. Основу всех ПЛИС составляет логическая матрица. Она может быть полной (из элементов И и ИЛИ), матрицей из однотипных элементов (И-НЕ, ИЛИ-НЕ и др.) или с фиксированными элементами ИЛИ. Часто логическая матрица разбивается на логические блоки с элементами запоминания.

СИНХРОНИЗАЦИЯ, ВНЕШНЕЕ УПРАВЛЕНИЕ

|

|

ЛОГИЧЕСКАЯ |

ВЫХОДНЫЕБЛОКИ |

|

|

|

ВХОДЫ |

|

МАТРИЦА |

|

|

||

|

(ЛОГИЧЕСКИЕ |

|

ВЫХОДЫ |

|||

ВХОДНЫЕБЛОКИ |

ячейки( ) |

ячейки( ) |

||||

БЛОКИ) |

|

|||||

УПРАВЛЯЮЩАЯ |

|

|||||

МАТРИЦА |

|

|||||

|

|

|||||

|

|

ОБРАТНАЯ СВЯЗЬ |

|

|

|

Рисунок 3. Структура ПЛИС

Во входных ячейках (блоках) имеются формирователи (дешифраторы) парафазных

сигналов (A, A , …) и элементы запоминания (триггеры, регистры).

Выходные ячейки могут быть многофункциональными и выполнять функции от простого линейного до управляемого выхода с управлением полярностью выхода (при возможности выбора активно-низкого (отрицательная логика) или активно-высокого (положительная логика) выходного сигнала), с запоминанием сумм произведений, с разрешением (запретом) выхода, с внутренней синхронизацией и т.д. Выбор функции многофункциональных выходных ячеек (блоков) осуществляет управляющая матрица. Под действием обратной связи (ОС) выходные блоки могут быть преобразованы в двунаправленные блоки ввода-вывода (В-В).

Синхронные узлы имеют входы синхронизации. Сигналы внешнего управления могут выполнять такие функции, как предварительная установка, сброс или загрузка регистров, разрешение (запрет) выходов и др.

В составе некоторых высокоинтегрированных ПЛИС имеются макроячейки высокого уровня сложности – счётчики, мультиплексоры, дешифраторы, АЛУ и ЗУ.

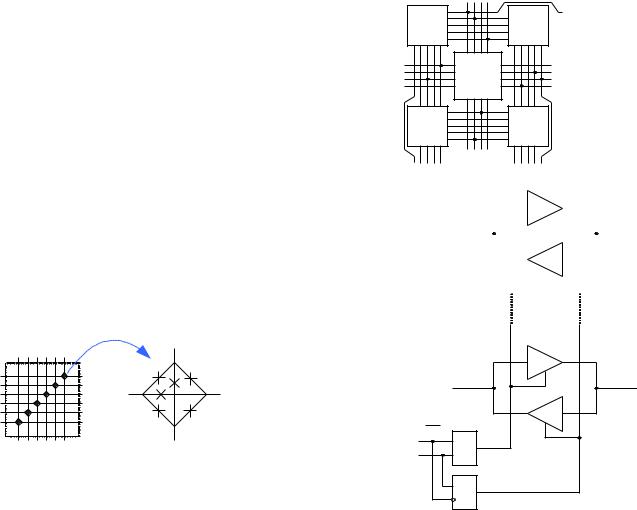

Наиболее развитыми являются микросхемы фирмы Xilinx (XC2018, XC2064, …, XC3090, …), получившие название «Программируемые вентильные матрицы» (ПВМ). Вот их некоторые особенности:

1.Логическая матрица построена на базе КМОП-элементов.

2.Логическая матрица состоит из нескольких десятков (до сотни и более) логических блоков (ЛБ) с динамически изменяемой конфигурацией, построенных на основе ячеек статических ЗУ с произвольной выборкой (рис. 4).

3.Каждый ЛБ имеет 4 – 5 логических входов, два выхода и тактовый вход (синхровход). Такой ЛБ может реализовать любую логическую функцию 4-5 логических переменных.

4.Каждый ЛБ может воспринимать на входе и формировать на выходе сигналы как положительной, так и отрицательной логики.

5.Вокруг логической матрицы расположено несколько десятков двунаправленных

блоков ввода-вывода (БВВ) тоже с изменяемой конфигурацией.

6. Каждый БВВ содержит входной регистр, схему настройки входного порогового напряжения и выходную схему с тремя состояниями (0,1, z) (рис.7).

Логические блоки и БВВ соединяются между собой. Для обеспечения дополнительных возможностей в изменении конфигурации ЛБ и БВВ используются разнообразные соединительные элементы, программируемые потребителем:

а) горизонтальные и вертикальные металлизированные линии, проложенные между ЛБ и БВВ и разделённые на сегменты (рис.5);

б) элементы обмена на координатных переключателях, соединяющие между собой отдельные сегменты металлизированных линий;

в) программируемые соединительные точки, связывающие металлизированные линии с логическими блоками и блоками ввода-вывода (рис.6).

Максимальная частота ПВМ 70 МГц.

Функциональная сложность (XC3090) – 9000 эквивалентных вентилей.

Аналогичную структуру имеют ПЛИС (СБИС) фирмы ALTERA, получившие название «Программируемые логические приборы» (PLD). PLD объединены в семейства MAX5000, МАХ7000, МАХ7000А, МАХ7000АЕ. Так, семейство МАХ7000А (АЕ) включает в себя шесть серий СБИС: ЕРМ7032АЕ, ЕРМ7256А, …, ЕРМ7512АЕ. СБИС ЕРМ7512АЕ включает в себя 10000 эквивалентных вентилей, 512 макроячеек, 22 блока логических матриц (БЛМ) и имеет максимальную частоту Fmax = 119 МГц. Менее сложная СБИС ЕРМ7032АЕ (600 эквивалентных вентилей) имеет Fmax = 178 МГц. СБИС семейства МАХ7000А (АЕ) имеют внутреннюю систему программирования (ISP), обеспечивающую эффективное программирование без применения специальных программаторов.

|

|

|

БВВ |

|

|

|

|

|

|

|

|

|

БВВ |

|

|

|

|

|

|

|

|

|

БВВ |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

БВВ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

БВВ |

|

|

ПБ |

|

|

|

|

|

|

|

|

|

|

ПБ |

|

|

|

|

|

|

|

|

|

|

ПБ |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЛБ |

|

|

|

|

|

|

|

|

|

|

ЛБ |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

БВВ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

БВВ |

|

|

ПБ |

|

|

|

|

|

|

|

|

|

|

ПБ |

|

|

|

|

|

|

|

|

|

|

ПБ |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЛБ |

|

|

|

|

|

|

|

|

|

|

ЛБ |

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

БВВ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

БВВ |

|

|

ПБ |

|

|

|

|

|

|

|

|

|

|

ПБ |

|

|

|

|

|

|

|

|

|

|

ПБ |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

БВВ |

|

|

|

|

|

|

|

|

|

БВВ |

|

|

|

|

|

|

|

|

|

БВВ |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 4. Структура ПЛИС

ПБ |

ПБ |

|

ЛБ |

ПБ |

ПБ |

Рисунок 5. Соединительные линии

A1 |

|

|

|

|

|

|

B1 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ПБ |

Рисунок 6. Переключательный блок

|

An |

Bn |

EA/EB |

& |

|

|

|

|

EO |

|

|

|

& |

|

Рисунок 7. Блок ввода-вывода