МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

ЧЕРНІВЕЦЬКИЙ НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ

ІМЕНІ ЮРІЯ ФЕДЬКОВИЧА

Кафедра комп’ютерних систем та мереж

Конспект лекцій з курсу «Мікроконтролери»

зі спеціальності 6.091501 «Комп’ютерні системи та мережі»

за напрямом підготовки бакалавра 0915 «Комп’ютерна інженерія»

Чернівці, 2009

Укладач: Рощупкін О.Ю. асистент кафедри комп’ютерних систем та мереж

Розглянуто та схвалено на засіданні кафедри комп’ютерних систем та мереж

Протокол № _ від “___” _________ 200__ р.

Завідувач кафедри

д.фіз.-мат.н., професор ________________ Мельничук С.В.

Секретар кафедри КСМ ________________ Гордіца В.Е.

Мікроконролери

Вступ

Дані методичні вказівки містять необхідні рекомендації для проектування мікропроцесорних систем автоматики і управління з використанням однокристальної ЕОМ (ОЕОМ) типуMCS-51.

Розглянуті архітектура ОЕОМ, особливості використання її паралельних і послідовного портів введення-виводу, таймерів-лічильників зовнішніх подій, системи переривань.

Приведені основні відомості про способи адресації, систему команд і особливості програмування мікропроцесорних систем на базі даної ОЕОМ.

Розглянуті приклади побудови мікропроцесорних систем на основі розглянутої ОЕОМ.

1. Загальна характеристика ОЕОМ MCS-51

Восьмирозрядні високопродуктивні однокристальні ОЕОМ (ОЕОМ) сімейства МК51 виконані по високоякісній N-МОП технології (серія 1816) і КМОП технології (серія 1830).

Використання ОЕОМ сімейства МК51 в порівнянні з МК48 забезпечує збільшення об'єму пам'яті команд і пам'яті даних. Нові можливості введення-виводу і периферійних пристроїв розширюють діапазон застосування і знижують загальні витрати системи. Залежно від умов використання, швидкодія системи збільшується мінімум в два з половиною рази і максимум вдесятеро [1].

Сімейство МК51 включає п'ять модифікацій ОЕОМ (що мають ідентичні основні характеристики), основна відмінність між якими полягає в реалізації пам'яті програм і потужності споживання.

ОЕОМ КР1816ВЕ51 і КР1830ВЕ51 містять масочно-программируемое в процесі виготовлення кристала ПЗП пам'яті програм ємкістю 4096 байт і розраховані на застосування в масовій продукції. За рахунок використання зовнішніх мікросхем пам'яті загальний об'єм пам'яті програм може бути розширений до 64 Кбайт.

ОЕОМ КМ1816ВЕ751 містить ППЗУ ємкістю 4096 байт із стиранням ультрафіолетовим випромінюванням і зручна на етапі розробки системи при відладці програм, а також при виробництві невеликими партіями або при створенні систем, що вимагають в процесі експлуатації періодичного підстроювання. За рахунок використання зовнішніх мікросхем пам'яті загальний об'єм пам'яті програм може бути розширений до 64 Кбайт.

ОЕОМ КР1816ВЕ31 і КР1830ВЕ31 не містять вбудованої пам'яті програм, проте можуть використовувати до 64 Кбайт зовнішньої постійної або перепрограмованої пам'яті програм і ефективно використовуватися в системах, що вимагають істотно більшого за об'ємом (чим 4 Кбайт на кристалі) ПЗП пам'яті програм.

Кожна з перерахованих вище мікросхем є відповідно аналогом БІС 8051, 80С51, 8751, 8031, 80С31 сімейство MCS-51 фірми Intel (США).

Порівняльні дані мікросхем приведені в таблиці 1.

Кожна ОЕОМ даного сімейства містить вбудоване ОЗУ пам'яті даних ємкістю 128 байт з можливістю розширення загального об'єму оперативної пам'яті даних за рахунок використання зовнішніх мікросхем ЗУПВ об'ємом 64 Кбайт.

Загальний об'єм пам'яті ОЕОМ сімейства МК51 може складати 64 Кбайт пам'яті програм, 64 Кбайт зовнішньої пам'яті даних, 128 байт внутрішньої пам'яті даних плюс регістри спеціальних функцій.

При розробці на базі ОЕОМ складніших систем можуть бути використані стандартні ІС з байтовою організацією, наприклад, серії КР580. Надалі позначення “МК51” буде загальним для всіх моделей сімейства, за винятком випадків, які будуть обумовлені особливо.

ОЕОМ містять всі вузли, необхідні для автономної роботи:

1. Центральний восьмирозрядний процесор;

2. Пам'ять програм об'ємом 4 Кбайт (лише КМ1816ВЕ751, КР1816ВЕ51 і КР1830ВЕ51);

3. Пам'ять даних об'ємом 128 байт;

4. Чотири восьмирозрядні програмовані канали введення-виводу;

5. Два 16-бітових багаторежимних таймера/счетчика;

6. Систему переривань з п'ятьма векторами і двома рівнями пріоритетів;

7. Послідовний інтерфейс;

8. Тактовий генератор.

Система команд ОЕОМ містить 111 базових команд з форматом 1, 2 або 3 байти.

Таблиця 1 – Порівняльні дані мікросхем сімейства МК51

|

Мікросхеми

|

Аналог

|

Об'єм внутрішньої пам'яті програм байт

|

Тип пам'яті програм

|

Об'єм внутрішньої пам'яті даних, байт

|

Максимальна частота дотримання тактових сигналів, Мгц

|

Струм споживання мА

|

|

КР1816ВЕ31 КР1816ВЕ51 КМ1816ВЕ751 КР1830ВЕ31 КР1830ВЕ51

|

8031АН 8051АН 8751Н 80С31ВН 80С51ВН

|

- 4До 4До - 4До

|

Внешн. ПЗП ППЗУ Внешн. ПЗП

|

128 128 128 128 128 |

12,0 12,0 12,0 12,0 12,0 |

150,0 150,0 220,0 18,0 18,0 |

ОЕОМ також має:

- 32 Рона (регістра загального призначення);

- 128 визначуваних користувачем програмно-керованих прапорів;

- набір регістрів спеціальних функцій, частина яких допускає побітову адресацію.

Рони і визначувані користувачем програмно-керовані прапори розташовані в адресному просторі внутрішнього ОЗУ даних. Регістри спеціальних функцій (SFR, SPECIAL FUNCTION REGISTERS) з вказівкою їх адрес приведені в таблиці 2.

Таблиця 2 – Регістри спеціальних функцій

|

Позначення

|

Найменування

|

Адреса

|

|

* ACC

|

Акумулятор

|

0E0H

|

|

* B

|

Регістр В

|

0F0H

|

|

* PSW

|

Регістр стану програми

|

0D0H

|

|

SP

|

Вказівник стека

|

81H

|

|

DPTR

|

Вказівник даних. 2 байти:

|

|

|

DPL

|

Молодший байт

|

82H

|

|

DPH

|

Старший байт

|

83Н

|

|

* P0

|

Порт 0

|

80H

|

|

* P1

|

Порт 1

|

90H

|

|

* P2

|

Порт 2

|

0A0H

|

|

* P3

|

Порт 3

|

0B0H

|

|

* IP

|

Регістр пріоритетів переривань

|

0B8H

|

|

* IE

|

Регістр дозволу переривань

|

0A8H

|

|

TMOD

|

Регістр режимів таймера/счетчика

|

89H

|

|

* TCON

|

Регістр управління таймера/счетчика

|

88H

|

|

TH0

|

Таймер/счетчик 0 (старший байт)

|

8CH

|

|

TL0

|

Таймер/счетчик 0 (молодший байт)

|

8AH

|

|

TH1

|

Таймер/счетчик 1 (старший байт)

|

8DH

|

|

TL1

|

Таймер/счетчик 1 (молодший байт)

|

8BH

|

|

* SCON

|

Управління послідовним портом

|

98H

|

|

SBUF

|

Буфер послідовного порту

|

99H

|

|

PCON

|

Управління енергоспоживанням

|

87H

|

* - регістри, що допускають побітову адресацію.

Нижче коротко описуються функції регістрів, приведених в таблиці 2. Детально ці регістри розглядаються у відповідних розділах справжнього опису.

Акумулятор. АСС – регістр акумулятора. Команди, призначені для роботи з акумулятором, використовують його ім'я «А», наприклад, MOV A, P2. Ім'я «АСС» використовується, наприклад, при побітовій адресації акумулятора. Так, символічне ім'я п'ятого біта акумулятора при використанні асемблера ASM51 буде наступним: АСС. 5.

Регістр В. Іспользуєтся під час операцій множення і ділення. Для інших інструкцій регістр В може розглядатися як додатковий регістр внутрішньої надоперативної пам'яті (СОЗУ).

Регістр стану програми. Регістр PSW містить інформацію про стан програми. Формат регістра PSW (ССП) приведений в таблиці 3.

Таблиця 3 – Формат регістра ССП

|

Позиція

|

Символ

|

Ім'я і призначення

|

|

PSW.7

|

C

|

Прапор перенесення. Встановлюється і скидається апаратурними засобами при виконанні арифметичних і логічних операцій. Програмно доступний.

|

|

PSW.6

|

AC

|

Прапор допоміжного перенесення. Встановлюється і скидається апаратурними засобами при виконанні команд складання і віднімання і сигналізує про перенесення або позику в біті 3 (вважаючи молодший біт нульовим). Програмно доступний.

|

|

PSW.5

|

F0

|

Прапор F0. Може бути встановлений, скинутий або перевірений програмою як прапор, специфируемый користувачем.

|

|

PSW.4

|

RS1

|

Вибір банку регістрів. Встановлюється і скидається

|

|

PSW.3

|

RS0

|

програмою для вибору робочого банку регістрів (див. Рисунок 5).

|

|

PSW.2

|

OV

|

Прапор переповнювання. Встановлюється і скидається апаратний при виконанні арифметичних операцій. Програмно доступний.

|

|

PSW.1

|

- |

Не використовується.

|

|

PSW.0

|

P

|

Прапор пріоритету. Встановлюється і скидається апаратурно в кожному циклі команди і фіксує нечетное/четное (1/0) число одиничних біт в акумуляторі, тобто виконує контроль по парності.

|

Вказівник стека SP. 8-бітовий регістр, вміст якого инкрементируется перед записом даних в стек при виконанні команд PUSH і CALL. При початковому скиданні Вказівник стека встановлюється в 07Н, а область стека в ОЗУ даних починається з адреси 08Н. При необхідності шляхом перевизначення Вказівника стека область стека може бути розташована в будь-якому місці внутрішнього ОЗУ даних ОЕОМ.

Вказівник даних. Вказівник даних (DPTR) складається із старшого байта (DPH) і молодшого байта (DPL). Містить 16-бітову адресу при зверненні до зовнішньої пам'яті. Може використовуватися як 16-бітовий регістр або як два незалежні восьмибітові регістри.

Порт 0 – Порт 3. Регістрами спеціальних функцій Р0, Р1, Р2, Р3 є регістри - “клямки” відповідно портів Р0, Р1, Р2, Р3.

Буфер послідовного порту. SBUF є двома окремим регістром: буфер передавача і буфер приймача. Коли дані записуються в SBUF, вони поступають в буфер передавача, причому запис байта в SBUF автоматично ініціює його передачу через послідовний порт. Коли дані читаються з SBUF, вони вибираються з буфера приймача.

Регістри таймера. Регістрові пари (TH0, TL0) і (TH1, TL1) утворюють 16-бітові регістри – лічильники відповідно таймера / лічильника 0 і таймера / лічильника 1.

Регістри управління. Регістри спеціальних функцій IP, IЕ, TMOD, TCON, SCON і PCON містять біти управління і біти стану системи переривань, таймерів / лічильників, послідовного порту, схеми управління вжитком енергії від джерела живлення.

ОЕОМ при функціонуванні забезпечує:

мінімальний час виконання команд складання – 1 мкс (при fтакт = 12 Мгц);

апаратне множення і ділення з мінімальним часом виконання команд множення / ділення – 4 мкс (при fтакт = 12 Мгц).

У ОЕОМ передбачена можливість завдання частоти внутрішнього генератора за допомогою кварцу, LC-цепочки або зовнішнього генератора.

Архітектура сімейства МК51 не дивлячись на те, що вона заснована на архітектурі сімейства МК48, все ж не є повністю сумісною з нею. У новому сімействі є ряд нових режимів адресації, додаткові інструкції, розширений адресний простір і ряд інших апаратних відмінностей. Розширена система команд забезпечує побайтову і побітову адресацію, двійкову і двійково-десяткову арифметику, індикацію переповнювання і визначення парності / непарності, можливість реалізації логічного процесора.

Найважливішою і відмітною рисою архітектури сімейства МК51 є те, що АЛУ може разом з виконанням операцій над 8-розрядними типами даних маніпулювати однорозрядними даними. Окремі програмно-доступні біти можуть бути встановлені, скинуті або замінені їх доповненням, можуть пересилатися, перевірятися і використовуватися в логічних обчисленнях. Тоді як підтримка простих типів даних (при існуючій тенденції до збільшення довжини слова) може з першого погляду здатися кроком назад, ця якість робить ОЕОМ сімейства МК51 особливо зручними для вживань, в яких використовуються контроллери. Алгоритми роботи останніх за своєю суттю передбачають наявність вхідних і вихідних булевих змінних, які складно реалізувати за допомогою стандартних мікропроцесорів. Всі ці властивості в цілому називаються булевим процесором сімейства МК51. Завдяки такому потужному АЛУ набір інструкцій мікро ЕОМ сімейства МК51 однаково добре личить як для управління в реальному масштабі часу, так і для реалізації алгоритмів з великим об'ємом даних.

2. Умовне графічне позначення ОЕОМ MCS-51

і призначення її окремих виводів

Мікросхеми сімейства КМ1816ВЕ751 конструктивно виконані в металокерамічному корпусі типа 2123.40-6 з прозорою для ультрафіолетового випромінювання кришкою. Що останні розглядаються в даному описі ОЕОМ сімейства МК51 конструктивно виконані в пластмасових корпусах типа 2123.40-2 [1]. Умовне графічне позначення мікросхем на електричних схемах показане на рисунку 1, а призначення виводів приведене в таблиці 4.

Рисунок 1 – Умовне графічне позначення ОЕОМ на електричних схемах

Таблиця 4 – Призначення виводів ОЕОМ

|

N виводу

|

Обозн.

|

Призначення

|

Тип

|

|

1-8 |

Р1.0 - Р1.7

|

8-розрядний двонаправлений порт Р1. Вхід адреси А0 - А7 при проверке внутрішнього ПЗП (РПЗУ)

|

вхід / вихід

|

|

9 |

(

|

Сигнал загального скидання Виведення резервного живлення ОЗУ від зовнішнього джерела (для 1816)

|

вхід

|

|

10-17 |

Р3.0 - Р3.7

|

8-розрядний двонаправлений порт Р3. з додатковими функціями:

|

вхід / вихід

|

|

|

Р3.0

|

Послідовні дані приймача - RXD

|

вхід

|

|

|

Р3.1

|

Послідовні дані передавача - Тxd

|

вихід

|

|

|

Р3.2

|

Вхід зовнішнього переривання 0-

|

вхід

|

|

|

Р3.3

|

Вхід зовнішнього переривання 1-

|

вхід

|

|

|

Р3.4

|

Вхід таймера/счетчика 0: - Т0

|

вхід

|

|

|

Р3.5

|

Вхід таймера/счетчика 1: - Т1

|

вхід

|

|

|

Р3.6

|

Вихід стробуючого сигналу при записі в зовнішню пам'ять даних:

-

|

вихід

|

|

|

Р3.7

|

Вихід стробуючого сигналу при читанні із зовнішньої пам'яті даних

-

|

вихід

|

|

18 19 |

BQ2 BQ1

|

Виводи для підключення кварцевого резонатора

|

вихід вхід

|

|

20 |

0 У

|

Загальний вивід

|

|

|

21-28 |

Р2.0 - Р2.7

|

8-розрядний двонаправлений порт Р2. Вихід адреси А8 - А15 в режимі роботи із зовнішньою пам'яттю В режиме перевірки внутрішнього ПЗП виводи Р2.0 - Р2.3 використовуються як вхід адреси А8 - А11 Виведення Р2.7 - дозвіл читання ПЗП: - (вхідний)

|

вхід / вихід

|

|

29 |

РМЕ (РВПП)

|

Дозвіл зовнішній програмній пам'яті (активний сигнал – логічний 0)

|

вихід

|

|

30 |

ALE / (САВП / )

|

Вихідний сигнал дозволу фиксации адреси. При программировании РПЗУ сигнал: - (вхідний)

|

вхід / вихід

|

|

31 |

(

|

Блокування роботи з внутрішньою пам'яттю програм. При програмуванні РПЗУ подається сигнал UPR

|

вхід

|

|

32-39 |

Р0.7 – Р0.0

|

8-розрядний двонаправлений порт Р0. Шина адреси / даних при роботі із зовнішньою пам'яттю. Вихід даних D7 – D0 в режимі перевірки внутрішнього ПЗП (РПЗУ)

|

вхід / вихід

|

|

40 |

UCC

|

Виведення живлення від джерела напруги +5 У

|

вхід

|

3. Структура ОЕОМ MCS-51 і її опис

Структура ОЕОМ приведена на рисунку 2.

Рисунок 2 – Структурна схема ОЕОМ ВЕ751

ОЕОМ складається з наступних основних функціональних вузлів: блоку управління і синхронізації; блоку арифметико-логічного пристрою (АЛУ); резидентній пам'яті даних (РПД) об'ємом 128 байт; резидентній пам'яті програм (РПП) об'ємом 4 Кбайт; блоку переривань, таймерів і послідовного порту; чотирьох програмованих паралельних портів введення-виводу; схеми десяткової корекції вмісту акумулятора (СДКА); внутрішнього генератора тактових імпульсів (OSC); резидентної шини даних (РШД) і групи регістрів:

А – акумулятор;

B– регістр розширення акумулятора;

Т1, Т2 – регістри тимчасового зберігання операндів;

ССП (PSW) – регістр стану програми (прапорів);

РК (IR) – регістр команд;

СЬК (РС) – лічильник команд (програмний лічильник);

РУД (DPTR) – регістр-Вказівник даних, що складається з 2-х частин: молодшою – DPL і старшою – DPH;

РУСЯВИЙ (SP) – регістр-Вказівник стека;

РА (RAR) – регістр адреси;

РРТС (TMOD) – регістр режимів таймерів-лічильників;

РУСТ (TCON) – регістр управління-статусу таймерів-лічильників;

РУПП (SCON) – регістр управління приймачем послідовного порту;

SBUF(буфер ПРМ і буфер ПД) – буфери приймача і передавача послідовного порту;

РМП (IЕ) – регістр масок переривань;

РП (IP) – регістр пріоритетів переривань;

РУМ (PCON) – регістр управління потужністю споживання енергії від джерела

живлення.

3.1. Блок управління і синхронізації ОЕОМ

Блок управління і синхронізації призначений для вироблення синхронізуючих і таких, що управляють сигналів, що забезпечують координацію спільної роботи блоків ОЕОМ у всіх допустимих режимах її роботи.

До складу блоку управління входять: пристрій вироблення тимчасових інтервалів, логіка введення-виводу, регістр команд, дешифратор команд, ПЛМ і логіка управління ЕОМ.

Пристрій вироблення тимчасових інтервалів призначений для формирования і видач внутрішніх синхросигналів станів, фаз і циклів. Кількість машинних циклів визначає тривалість виконання команд. Практично всі команди ОЕОМ виконуються за один або два машинні цикли, окрім команд множення MUL А, В і ділення DIV А, В, тривалість виконання которых складає чотири машинні цикли. Машинний цикл має фіксовану тривалість і містить шість станів S1-S6, кожне з яких складається з двох тимчасових інтервалів, визначуваних фазами Р1 і Р2. Тривалість фази дорівнює періоду дотримання зовнішнього сигналу BQ, що є первинним сигналом синхронізації ОЕОМ. Сигнал BQ виробляється або вбудованим тактовим генератором ОЕОМ при підключенні до її виводів 18 (BQ2) і 19 (BQ1) кварцевого резонатора або LC-цепочки, або зовнішнім джерелом тактових сигналів.

Схема підключення кварцевого резонатора до виводів BQ2 і BQ1 показана на рисунку 3.

Рисунок 3 – Підключення кварцевого резонатора

Рисунок 4 – Діаграма формування машинних циклів ОЕОМ

Рисунок 4 ілюструє формування машинних циклів в ОЕОМ. Всі машинні цикли однакові, складаються з 12 періодів сигналу BQ, починаються фазою S1 P1 і закінчуються фазою S6 P2. Двічі за один машинний цикл формується сигнал ALE, що видається на однойменний вивід. Якщо, наприклад, зовнішня частота fBQ = 12 Мгц, то тривалість машинного циклу ТМЦ = 1 мкс.

У регістр команд (РК) пересилається з пам'яті програм код операції чергової виконуваної команди. Дешифратор команд декодує код операції і ідентифікує типа команди, що підлягає виконанню. Після цього з програмованої логічної матриці (ПЛМ) викликається послідовність сигналів, що управляють, для виконання команди.

3.2. Блок арифметико-логічного пристрою (АЛУ)

АЛУ є паралельним восьмирозрядним пристроєм, що забезпечує виконання арифметичних і логічних операцій, а також операцій логічного зрушення, обнулення, установки і тому подібне

Блок АЛУ складається з регістрів тимчасового зберігання операндів Т1, Т2, ПЗП констант, суматора, додаткового регістра (регістра В), акумулятора, регістра стану програми.

Регістри тимчасового зберігання операндів Т1, Т2 - восьмирозрядні регістри, призначені для прийому і зберігання операндів на час виконання операцій над ними. Програмно не доступні.

ПЗП констант забезпечує вироблення коди, що коректує, при двійково-десятковому представленні даних, коди маски при бітових операціях і коди констант.

Паралельний восьмирозрядний суматор є схемою комбінаційного типа з послідовним перенесенням, призначеною для виконання арифметичних операцій складання, віднімання і логічних операцій складання, множення, нерівнозначності і ін.

Регістр В - восьмирозрядний регістр, використовуваний під час операцій множення і ділення. Для інших інструкцій він може розглядатися як додатковий надоперативний регістр.

Акумулятор є восьмирозрядним регістром, призначеним для прийому і зберігання результату, отриманого при виконанні арифметико-логічних операцій або операцій пересилки.

Регістр стану програми (PSW) призначений для зберігання інформації про стан АЛУ при виконанні програми. Позначення розрядів регістра PSW і призначення розрядів приведені відповідно в таблицях 5 і 6.

Таблиця 5 – Позначення розрядів регістра ССП (PSW)

|

Біти

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Позначення

|

CY

|

AC

|

F0

|

RS1

|

RS0

|

0V

|

- |

Р

|

Таблиця 6 – Призначення окремих розрядів регістра ССП (PSW)

|

Біти

|

Наїменов.

|

Призначення бітів

|

Доступ до біта

| |

|

7 |

CY

|

Прапор перенесення. Змінюється під час виконання деяких арифметических і логічних інструкцій.

|

апаратний або програмно

| |

|

6 |

AC

|

Прапор додаткового перенесення. Апаратний встановлюється / скидається під час виконання інструкцій складання або віднімання для вказівки перенесення або позики в біті 3 при утворенні молодшого півбайта результату (D0-D3).

|

апаратний або програмно

| |

|

5 |

F0

|

Прапор 0. Прапор стану, определяемый користувачем.

|

програмно

| |

|

4 |

RS1

|

Вказівник банку робочих регістрів РПД

|

програмно

| |

|

3 |

RS0

|

Вказівник банку робочих регістрів РПД

|

програмно

| |

|

|

RS1

|

RS0

|

Банк 0 з адресами (00Н - 07Н) Банк 1 з адресами (08Н - 0FH) Банк 2 з адресами (10Н - 17Н) Банк 3 з адресами (18Н - 1FH)

|

|

|

0 0 1 1 |

0 1 0 1 | |||

|

2 |

0V

|

Прапор переповнювання. Апаратний устанавливается/сбрасывается під час виконання арифметичних инструкций для вказівки стану переповнювання

|

апаратний або програмно

| |

|

1 |

- |

Резервний. Містить тригер, доступный по запису ("0" і "1") і читанню, який можна використовувати

|

| |

|

0 |

Р

|

Біт парності. Апаратний скидається / встановлюється в кожному циклі інструкцій для вказівки парного / непарної кількості разрядов акумулятора, що знаходяться в змозі "1".

|

апаратний або програмно

| |

3.3 Резидентна пам'ять даних

Пам'ять даних призначена для прийому, зберігання і видачі інформації, використовуваній в процесі виконання програми. Пам'ять даних ділиться на внутрішню (резидентну) –РПД і зовнішню – ВПД. До складу вузла, названого на рисунку 2 РПД, входить ОЗУ ємкістю 128 байт і дешифратор адреси. Управляють роботою РПД два регістри: РА (RAR) – регістр адреси; РУСЯВИЙ (SP) – Вказівник стека.

Регістр адреси ОЗУ (РА) призначений для прийому і зберігання адреси вибираної за допомогою дешифратора вічка пам'яті, яка може містити як біт, так і байт інформації.

ОЗУ є 128 восьмирозрядними регістрами, призначеними для прийому, зберігання і видачі різній інформації. 16 з цих регістрів допускають побітову адресацію.

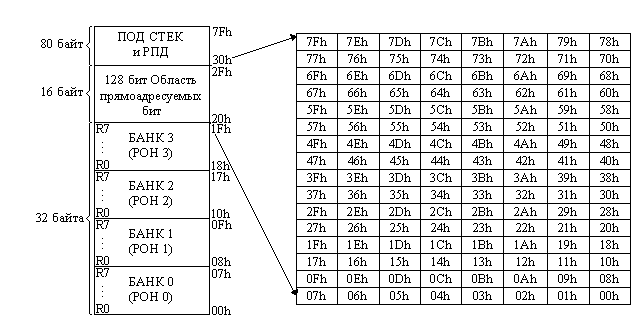

На рисунку 5 приведений розподіл адресного простору РПД і область прямоадресуемых біт.

Рисунок 5 – Розподіл адресного простору РПД і область прямоадресуемых біт

Вказівник стека є восьмирозрядним регістром, призначеним для прийому і зберігання адреси вічка стека. При виконанні команд LCALL, ACALL вміст Вказівника стека збільшується на 2. При виконанні команд RET, RETI вміст Вказівника стека зменшується на 2. При виконанні команди PUSH direct вміст Вказівника стека збільшується на 1. При виконанні команди POP direct вміст Вказівника стека зменшується на 1. Після скидання в Вказівнику стека встановлюється адреса 07Н, що відповідає початку стека з адресою 08Н.

Детальніше організація пам'яті даних мікропроцесорних систем, що використовують дану ОЕОМ, розглянута в розділі 4.6.

3.4 Резидентна пам'ять програм

Пам'ять програм призначена для зберігання програм і має окреме від пам'яті даних адресний простір об'ємом до 64 Кбайт, причому, для мікросхем КР1816ВЕ51, КМ1816ВЕ751 і для КР1830ВЕ51 частина пам'яті програм з адресами 0000Н - 0FFFH розташована на кристалі ОЕОМ. Пам'ять програм, розташована на кристалі (РПП), складається з 12-розрядного дешифратора і ПЗП ємкістю 4К*8 біт для мікросхем КР1816ВЕ51, КР1830ВЕ51 або ППЗУ з ультрафіолетовим стиранням ємкістю 4К*8 біт для КМ1816ВЕ751. Запис програм в ПЗП відбувається під час виготовлення кристалів.

Якщо на виведення ОЕОМ DEMA (ОРПП) подана напруга живлення UСС (логічна 1), то звернення до зовнішньої пам'яті програм відбувається автоматично при виробленні лічильником команд адреси, 0FFFH, що перевищує. Якщо адреса знаходиться в межах 0000Н—0FFFH, звернення відбувається до пам'яті програм, розташованої на кристалі (резидентній пам'яті програм).

Якщо на вивід ОЕОМ DEMA (ОРПП) поданий "0", внутрішня пам'ять програм відключається, і, починаючи з адреси 0000Н, всі звернення виконуються до зовнішньої пам'яті програм.

Для формування поточної 16-розрядної адреси пам'яті програм служить лічильник команд (програмний лічильник) – СЬК (РС). 12 молодших розрядів цього регістра використовуються при адресації вічок РПП об'ємом 212 = 4 Кбайт.

Детальніше організація пам'яті програм мікропроцесорних систем, що використовують дану ОЕОМ, розглянута в розділі 4.6.

3.5 Блок переривань

ОЕОМ має систему переривань з п'ятьма векторами (адресами підпрограм обробки переривань) і двома рівнями пріоритетів. Джерелами переривань є: два зовнішні переривання, що поступають через порт 3; два переривання від переповнювання таймерів – лічильників Т/Сnt 0 і T/CNT 1 і переривання при завершенні передачі або прийому даних при обміні через послідовний порт.

Для програмування і управління роботою системи переривань служать два регістри: РМП (IE) – регістр масок переривань і РП (IP) – регістр пріоритетів переривань, а також чотири молодших біта регістра РУСТ (TCON), див. таблицю 12, 13.

Регістр пріоритетів переривань (IP) призначений для установки рівня пріоритету переривання для кожного з п'яти джерел переривань. Позначення розрядів регістра IP показане в таблиці 7, а їх призначення вказане нижче.

РХ0 – установка рівня пріоритету переривання від зовнішнього джерела .

РТ0 – установка рівня пріоритету переривання від Т/С 0.

РХ1 – установка рівня пріоритету переривання від зовнішнього джерела .

РТ1 – установка рівня пріоритету переривання від Т/С 1.

PS– установка рівня пріоритету переривання від послідовного порту.

Х – резервний розряд.

Таблиця 7 – Позначення розрядів регістра IP

|

Біти

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Позначення

|

Х

|

Х

|

Х

|

PS

|

РТ1

|

РХ1

|

РТ0

|

РХ0

|

Наявність в розряді IP "1" встановлює для відповідного джерела високий рівень пріоритету, а наявність в розряді IP "0" – низький рівень пріоритету. При читанні резервних розрядів відповідні лінії магістралі даних не визначені. Користувач не повинен записувати "1" в резервні розряди, оскільки вони зарезервовані під подальше розширення сімейства МК51.

Регістр дозволу переривань (IE) призначений для дозволу або заборони переривань від відповідних джерел. Позначення розрядів регістра IE показане в таблиці 8, а їх призначення вказане нижче.

Таблиця 8 - Позначення розрядів регістра IE

|

Біти

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Позначення

|

ЕА

|

X

|

X

|

ES

|

ЕТ1

|

ЕХ1

|

ЕТ0

|

ЕХ0

|

ЕА – управління всіма джерелами переривань одночасно. Якщо ЕА = 0, то переривання заборонені. Якщо ЕА = 1, то переривання можуть бути дозволені індивідуальними дозволами ЕХ0, ЕТ0, ЕХ1, ЕТ1, ES.

Х – резервний розряд.

ES – управління перериванням від послідовного порту. ES = 1 – дозвіл. ES = 0 – заборона.

ЕТ1 – управління перериванням від Т/С 1. ЕТ1 = 1 – дозвіл. ЕТ1 = 0 – заборона.

ЕХ1 – управління перериванням від зовнішнього джерела . ЕХ1 = 1 – дозвіл. ЕХ1 = 0 – заборона .

ЕТ0 – управління перериванням від Т/С 0. ЕТ0 = 1 – дозвіл. ЕТ0 = 0 – заборона.

ЕХ0 – управління перериванням від зовнішнього джерела . ЕХ0 = 1 – дозвіл. ЕХ0 = 0 – заборона.

При читанні резервних розрядів відповідні лінії магістралі не визначені. Користувач не повинен записувати "1" в резервні розряди, оскільки вони зарезервовані під подальше розширення сімейства МК51.

Блок переривань містить також схему логічної обробки прапорів переривань, яка здійснює пріоритетний вибір запиту переривання, скидання його прапора і ініціює вироблення апаратний реалізованою команди переходу на підпрограму обслуговування переривання LCALL.

Схема вироблення вектора переривання формує двобайтові адреси підпрограм обслуговування переривання залежно від джерела переривання, які приведені в таблиці 9.

Таблиця 9 - Джерела переривань і адреси обслуговуючих їх підпрограм

-

Джерело переривання

Вектор переривання

Зовнішнє переривання

0003Н

Таймер / лічильник Т/С 0

000ВН

Зовнішнє переривання

0013Н

Таймер / лічильник Т/С 1

001ВН

Послідовний порт

0023Н

Детальніше система переривань описана в розділі 4.4.

3.6. Блок таймерів – лічильників

Таймери – лічильники (Т/С) призначені для підрахунку зовнішніх подій, для здобуття програмно керованих тимчасових затримок і виконання времязадающих функцій ОЕОМ.

До складу блоку Т/С входять:

два 16-розрядні регістри Т/С 0 і Т/С 1;

восьмирозрядний регістр режимів Т/С (TMOD);

восьмирозрядний регістр управління (TCON);

схема інкремента;

схема фіксації,, Т0, Т1;

схема управління прапорами;

логіка управління Т/С.

Два 16-розрядні регістри Т/С 0 і Т/С 1 виконують функцію зберігання вмісту рахунку. Кожен з них складається з пари восьмирозрядних регістрів, відповідно ТН0, TL0 і ТН1, TL1. Причому регістри ТН0, ТН1 – старші, а регістри TL0, TL1 – молодші 8 розрядів. Кожен з восьмирозрядних регістрів має свою адресу і може бути використаний як РОН, якщо Т/С не використовуються (біт TR0 для Т/С 0 і біта TR1 для Т/С 1 в регістрі управління TCON рівні "0").

Код величини початкового рахунку заноситься в регістри Т/С програмно. В процесі рахунку вміст регістрів Т/С инкрементируется. Ознакою закінчення рахунку, як правило, є переповнювання регістра Т/С, тобто перехід його вмісту із стану "всі одиниці" в стан "всі нулі". Всі регістри ТН0, ТН1, TL0, TL1 доступні по читанню, і, при необхідності, контроль досягнення необхідної величини рахунку може виконуватися програмно.

Регістр режимів Т/С (TMOD) призначений для прийому і зберігання коди, що визначає:

— один з 4-х можливих режимів роботи кожного Т/С;

— працю таймерами або лічильниками;

— управління Т/С від зовнішнього виводу.

Позначення розрядів регістра TMOD приведене в таблиці 10, а призначення розрядів – в таблиці 11.

Таблиця 10 – Позначення розрядів регістра TMOD

|

Біти

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Обозн.

|

GATE1

|

|

Ml.1

|

М0.1

|

GATE0

|

|

М1.0

|

М0.0

|

Таблиця 11 – Призначення розрядів регістра TMOD

|

Біти

|

Найменування

|

Призначення бітів

|

Примітка

| ||

|

0-1 4-5 |

М0 - М1

|

Визначають один з 4-х режимів роботи, окремо для Т/С 1 і Т/С 0

|

Всі біти устанавливаются програмно; біти 0-3 визначають режим роботи Т/С 0, біти 4-7 визначають режим роботи Т/С 1.

| ||

|

М1

|

М0

|

Режим

| |||

|

0 |

0 |

0 | |||

|

0 |

1 |

1 | |||

|

1 |

0 |

2 | |||

|

1 |

1 |

3 | |||

|

2, 6 |

С/Т 0 С/Т 1

|

Визначають роботу в якості: С/Т 0, С/Т 1 = 0 – таймера С/Т 0, С/Т 1 = 1 – лічильника

|

| ||

|

3, 7 |

GATE

|

Дозволяє управляти таймером від зовнішнього виводу ( - для Т/С 0, - для Т/С 1). GATE= 0 – управління забороненеGATE= 1 – управління дозволене

|

| ||

При роботі таймером вміст регістра Т/С инкрементируется в кожному машинному циклі, тобто Т/С є лічильником машинних циклів ОЕОМ. Оскільки машинний цикл складається з 12 періодів частоти синхронізації ОЕОМ fBQ, то частота рахунку в даному випадку рівна fBQ / 12.

При роботі Т/С лічильником зовнішніх подій вміст регістра Т/С инкрементируется у відповідь на перехід з "1" в "0" сигналу на рахунковому вході ОЕОМ (виведення Т0 для Т/С 0 і виведення Т1 для Т/С 1). Рахункові входи апаратний перевіряються у фазі S5P2 кожного машинного циклу. Коли перевірки показують високий рівень на рахунковому вході в одному машинному циклі і низький рівень в іншому машинному циклі, регістр Т/С инкрементируется. Нове (инкрементированное) значення заноситься в регістр Т/С у фазі S3P1 машинного циклу, безпосередньо наступного за тим, в якому був виявлений перехід з "1" в "0" на рахунковому вході ОЕОМ. Т. до. для розпізнавання такого переходу потрібно два машинні цикли (24 періоди частоти синхронізації ОЕОМ fBQ), то максимальна частота рахунку Т/С в режимі лічильника рівна fBQ / 24.

Аби рівень сигналу на рахунковому вході був гарантовано зафіксований, він повинен залишатися незмінним в перебіг як мінімум одного машинного циклу.

Регістр управління (TCON) призначений для прийому і зберігання коди слова, що управляє. Позначення розрядів регістра TCON приведене в таблиці 12, а призначення розрядів – в таблиці 13.

Таблиця 12 – Позначення розрядів регістра TCON

|

Біти

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Позначення

|

TF1

|

TR1

|

TF0

|

TR0

|

IE1

|

IT1

|

IE0

|

IT0

|

Таблиця 13 – Призначення розрядів регістра TCON

|

Біти

|

Найменування

|

Призначення бітів

|

Примітка

|

|

6 4 |

TR1 TR0

|

Біти включення Т/С, окремо для Т/С 0 і Т/С 1. TR = 0 – вимкнений TR = 1 – включений.

|

Біти встановлюються і скидаються програмно. Доступні по читанню.

|

|

7 5 |

TF1 TF0

|

Прапори переповнювання Т/С.

|

Біти скидаються і встановлюються апаратний і програмно. Доступні по читанню.

|

|

2 0 |

IT1 IT0

|

Біти, що визначають вигляд переривання по входах INT1, INT0. IT= 0 – переривання по рівню (низькому) IT= 1 – переривання по фронту (перехід з "1" в "0")

|

Біти встановлюються і скидаються програмно. Доступні по читанню

|

|

3 1 |

IE1 IE0

|

Прапори запиту зовнішніх переривань по входах INT1, INT0.

|

Біти скидаються і встановлюються апаратний і програмно Доступні по читанню

|

|

|

|

|

Біти 4, 5 відносяться до Т/С 0; біти 6, 7 – до Т/С 1. Біти 0, 1 визначають зовнішні переривання по входу INT0, біти 2, 3 – по входу INT1.

|

Прапори переповнювання TF0 і TF1 встановлюються апаратний при переповнюванні відповідних Т/С (перехід Т/С із стану "всі одиниці" в стан "всі нулі"). Якщо при цьому переривання від відповідного Т/С дозволене, то установка прапора TF викличе переривання. Прапори TF0 і TF1 скидаються апаратний при передачі управління програмі обробки відповідного переривання.

Прапори TF0 і TF1 програмно доступні і можуть бути встановлені / скинуті програмою. Використовуючи цей механізм, переривання по TF0 і TF1 можуть бути викликані (установка TF) і скасовані (скидання TF) програмою.

Прапори IE0 і IE1 встановлюються апаратний від зовнішніх переривань (відповідно входи ОЕОМ INT0 і INT1) або програмно і ініціюють виклик програми обробки відповідного переривання. Скидання цих прапорів виконується апаратний при обслуговуванні переривання лише у тому випадку, коли переривання було викликане по фронту сигналу. Якщо переривання було викликане рівнем сигналу на вході INT0 (INT1), то скидання прапора IE повинна виконувати програма обслуговування переривання, впливаючи на джерело переривання для зняття ним запиту.

Схема інкремента призначена:

— для збільшення на 1 в кожному машинному циклі вмісту регістрів Т/С 0, Т/С 1, для яких встановлений режим таймера і рахівниць дозволений;

— для збільшення на 1 вмісту регістрів Т/С 0, Т/С 1, для яких встановлений режим лічильника, рахунок дозволений і на відповідному вході ОЕОМ (Т0 для Т/С 0 і Т1 для Т/С 1) зафіксований рахунковий імпульс.

Схема фіксації INT0, INT1, Т0, Т1 є чотирма тригером В кожному машинному циклі у момент S5P2 в них запам'ятовується інформація з виводів ОЕОМ INT0, INT1, Т0, Т1.

Схема управління прапорами виробляє і знімає прапори переповнювання Т/С і прапори запитів зовнішніх переривань.

Логіка управління Т/С синхронізує роботу регістрів Т/С 0 і Т/С 1 відповідно до запрограмованих режимів роботи і синхронізує роботу блоку Т/С з роботою

ОЕОМ.

Детальніше режими роботи і особливості застосування таймерів – лічильників розглянуті в розділі 4.1.

3.7. Блок послідовного порту (інтерфейсу)

Блок послідовного інтерфейсу призначений для організації введення-виведення послідовних даних.

До складу блоку входять: буфер інтерфейсу, логіка управління інтерфейсом, регістр управління, буфер передавача, буфер приймача, приймач – передавач послідовного порту.

Буфер інтерфейсу забезпечує побайтовий обмін інформацією між внутрішньою (резидентною) магістраллю даних і шиною інтерфейсу.

Логіка управління інтерфейсом призначена для вироблення сигналів управління, що забезпечують чотири режими роботи послідовного інтерфейсу.

Регістр управління (SCON) призначений для прийому і зберігання коди восьмибітового слова, керівника послідовним інтерфейсом. Позначення розрядів регістра SCON приведене в таблиці 14. Всі розряди регістра SCON програмно доступні по запису ("0" і "1") і читанню.

Розряди SM0, SM1 визначають режим роботи інтерфейсу, як вказано в таблиці 15.

Таблиця 14 – Позначення розрядів регістра SCON

|

Біти

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Позначення

|

SM0

|

SM1

|

SM2

|

REN

|

ТВ8

|

RB8

|

TI

|

RI

|

Таблиця 15 – Вплив розрядів SM0, SM1 SCON на режим роботи інтерфейсу

|

SM0

|

SM1

|

Режим

|

Найменування

|

Швидкість передачі

|

|

0 |

0 |

0 |

Сдвіговий регістр

|

fBQ / 12

|

|

0 |

1 |

1 |

8-бітовий універсальний асинхронний приймач / передатчик (УАПП)

|

змінна, задається Т/С 1

|

|

1 |

0 |

2 |

9-бітовий УАПП

|

fBQ / 64 або fBQ / 32

|

|

1 |

1 |

3 |

9-бітовий УАПП

|

змінна, задається Т/С 1

|

Останні біти регістра мають наступне призначення:

SM2 – дозвіл багатопроцесорної роботи. У режимах 2 і 3 приSM2 = 1 прапорRIне активізується, якщо дев'ятий прийнятий біт даних рівний "0". У режимі 1 приSM2 = 1 прапорRIне активізується, якщо не прийнятий стоп-біт, рівний "1". У режимі 0 бітSM2 має бути встановлений в "0".

REN– дозвіл прийому послідовних даних. Встановлюється і скидається програмою відповідно для дозволу і заборони прийому.

ТВ8 – дев'ятий біт передаваних даних в режимах 2 і 3. Встановлюється і скидається програмою.

RB8 – дев'ятий біт прийнятих даних в режимах 2 і 3. У режимі 1, якщоSM2 = 0,RB8 є прийнятим стоп-бітом. У режимі 0 бітRB8 не використовується.

TI– прапор переривання передавача. Встановлюється апаратний в кінці часу видачі 8-го біта в режимі 0 або на початку стоп-біта в інших режимах. Скидається програмно.

RI– прапор переривання приймача. Встановлюється апаратний в кінці часу прийому 8-го біта в режимі 0 або через половину інтервалу стоп-біта в режимах 1, 2, 3 приSM2 = 0. ПриSM2 = 1 див. опис для бітаSM2.

Буфер передавача призначений для прийому з шини інтерфейсу паралельних даних і видачі їх на передавач послідовного порту.

Буфер приймача служить для прийому даних в паралельній формі від приймача послідовного інтерфейсу.

Буфер приймача і буфер передавача при програмному доступі мають однакове ім'я (SBUF) і адресу (99Н). Якщо команда використовує SBUF як регістр джерела, то звернення відбувається до буфера приймача. Якщо команда використовує SBUF як регістр призначення, то звернення відбувається до буфера передавача.

У всіх режимах роботи послідовного порту передача ініціюється будь-якою командою, яка використовує SBUF як регістр призначення.

Приймач / передавач послідовного порту призначений для прийому послідовного потоку символів з входу послідовного порту, виділення даних і видачі їх в буфер приймача, а також для прийому паралельних даних з буфера передавача, перетворення їх в послідовний потік символів і видачі його на вихід послідовного порту.

Детальніше режими роботи і особливості застосування послідовного інтерфейсу розглянуті в розділі 4.3.

3.8. Паралельні порти введення-виводу

Дана ОЕОМ містить 4 паралельних 8-розрядних програмованих порту введення-виведення дискретної інформації P0, P1, P2, P3.

Порти Р0, Р1, Р2, Р3 є двонаправленими портами введення-виводу і призначені для забезпечення обміну інформацією ОЕОМ із зовнішніми пристроями, утворюючи 32 лінії введення-виводу. Кожен з портів містить фіксатор-клямку, який є восьмирозрядним регістром, що має байтову і бітову адресацію для установки / скидання його розрядів за допомогою відповідних команд.

Фізичні адреси фіксаторів Р0, Р1, Р2, Р3 складають для:

Р0 – 80Н, при бітовій адресації 80Н – 87Н;

Р1 – 90Н, при бітовій адресації 90Н – 97Н;

Р2 – А0Н, при бітовій адресації А0Н – А7Н;

Р3 – В0Н, при бітовій адресації В0Н – В7Н.

Окрім роботі звичайними портами ввода/вывода лінії портів Р0 – РЗ можуть виконувати ряд додаткових функцій, описаних нижче.

Через порт Р0:

— виводиться молодший байт адреси А0 – А7 при роботі із зовнішньою пам'яттю програм і зовнішньою пам'яттю даних;

— видається з ОЕОМ і приймається в ОЕОМ байт даних при роботі із зовнішньою пам'яттю (при цьому обмін байтом даних і виведення молодшого байта адреси зовнішньої пам'яті мультиплексированы в часі);

— задаються дані при програмуванні внутрішнього ППЗУ, і читається вміст внутрішньої пам'яті програм.

Через порт Р1:

— задається молодший байт адреси при програмуванні внутрішнього ППЗУ і при читанні внутрішньої пам'яті програм.

Через порт Р2:

— виводиться старший байт адреси А8 – А15 при роботі із зовнішньою пам'яттю програм і зовнішньою пам'яттю даних (для зовнішньої пам'яті даних – лише при використанні команд МОvХ А, @DРТR і МОvХ @DРТR, А, які виробляють 16-розрядну адресу);

— задаються старші розряди (А8 – А11) адреси при програмуванні внутрішнього ППЗУ і при читанні внутрішньої пам'яті програм.

Кожна лінія порту Р3 має індивідуальну альтернативну функцію:

Р3.0 – RXD, вхід послідовного порту, призначений для введення послідовних даних в приймач послідовного порту;

Р3.1 – Тхd, вихід послідовного порту, призначений для виведення послідовних даних з передавача послідовного порту;

Р3.2 –, використовується як вхід 0 зовнішнього запиту переривання;

Р3.3 –, використовується як вхід 1 зовнішнього запиту переривання;

Р3.4 – Т0, використовується як вхід лічильника зовнішніх подій Т/С 0;

Р3.5 – Т1, використовується як вхід лічильника зовнішніх подій Т/С 1;

Р3.6 –, строб запису в зовнішню пам'ять даних, вихідний сигнал, супроводжуючий виведення даних через порт Р0 при використанні команд

МОVХ @Ri, А і МОvХ @DРТR, А;

Р3.7 –, строб читання із зовнішньої пам'яті даних, вихідний сигнал, супроводжуючий введення даних через порт Р0 при використанні команд

МОvХ А, @Ri і МОvХ А, @DРТR.

Альтернативна функція будь-яка з ліній порту Р3 реалізується лише в тому випадку, якщо у відповідному цій лінії фіксаторі-клямці міститься "1". Інакше на лінії порту Р3 присутній "0".

3.9. Схема десяткової корекції акумулятора (СДКА)

АЛУ ОЕОМ дозволяє виконувати складання двійково-десяткових даних в упакованому форматі (у 1 байт “упаковані” 2 десяткових цифри). При виконанні операції підсумовування таких чисел використовується команда “Складання”, яка підсумовує операнди по правилах двійкової арифметики і результат поміщає в акумулятор. Для виправлення можливої помилки (корекції вмісту акумулятора) застосовують команду десяткової корекції DA A, яка апаратний реалізується схемою десяткової корекції акумулятора.

3.10. Внутрішній тактовий генератор (OSC)

ОЕОМ містить внутрішній тактовий генератор (Рисунок 6), BQ1 і BQ2 є відповідно входом і виходом інвертуючого підсилювача, який може бути включений в режим генератора при підключенні до виводів BQ1 і BQ2 резонатора або LC-цепочки (Рисунок 7).

Рисунок 6 - Внутрішній тактовий генератор

Рисунок 7 - Підключення до виводів BQ1 і BQ2 резонатора і LC-цепочки

3.11. Резидентна шина даних

МІКРОЕВМ містить 8-розрядну внутрішню (резидентну) шину даних (РШД), через яку здійснюється обмін інформацією між різними частинами ОЕОМ.

3.12. Регістри

3.12.1. Акумулятор – 8-розрядний регістр, призначений для прийому і зберігання результату, отриманого при виконанні арифметичних і логічних операцій або операцій пересилки.

3.12.2 Регістр В - 8-розрядний регістр, використовуваний при виконанні операцій множення і ділення. У інших випадках він може розглядатися як додатковий регістр загального призначення (частина СОЗУ).

3.12.3. Регістри Т1, Т2 - 8-розрядні регістри тимчасового зберігання, призначені для прийому і зберігання операндів на час виконання операцій над ними в АЛУ. Програмно недоступні.

3.12.4. Регістр стану програми (PSW) - служить для зберігання інформації про результат виконання операції в АЛУ. Його називають також регістром прапорів (ознак). Позначення окремих розрядів регістра PSW і призначення розрядів приведені відповідно в таблицях 3,5 і 6.

Прапор перенесення СУ може встановлюватися і скидатися як апаратний, так і програмно. Апаратний він встановлюється, якщо при виконанні арифметичних або логічних операцій формується перенесення / заїм в старшому (сьомому) розряді 8-бітових операндів. При виконанні операцій множення і ділення прапор СУ скидається. Крім того, прапор СУ виконує функції “булевого акумулятора” в командах, що працюють з бітами.

Прапор допоміжного перенесення АС встановлюється / скидається апаратний або програмно. Апаратний встановлюється при виконанні операцій складання і віднімання при виникненні переноса/заема в 3-м розряді при утворенні молодшої тетради результату. Найчастіше використовується СДКА при виконанні команди DA A.

Прапор користувача F0 – встановлюється / скидається програмно і може використовуватися програмістом на свій розсуд.

Прапори-Вказівники поточного банку РОНов встановлюються / скидаються програмно і вказують, який з 4-х банків РОНов РПД (Рисунок 5) в даний момент часу є робочим (поточним).

Прапор переповнювання OV встановлюється / скидається програмно або апаратний. Апаратний встановлюється тоді, коли при виконанні операції сложения/вычитания над числами із знаком результат не укладається в діапазон -128 .. +127 і старший, знаковий біт спотворюється. При виконанні операції ділення прапор OV апаратний скидається, а в разі ділення на нуль встановлюється. При множенні прапор OV апаратний встановлюється, якщо результат більше 255.

Прапор парності (паритету) P встановлюється / скидається апаратний. Він доповнює вміст акумулятора до парного числа одиниць. У 9-розрядному слові, що складається з 8 розрядів акумулятора і біта Р, завжди міститься парне число одиничних бітів.

Все 7 названих прапорів програмно доступні по читанню.

3.12.5. Регістр команд РК (IR) призначений для зберігання коди операції (КОП) поточної виконуваної команди.

3.12.6. Лічильник команд СЬК (програмний лічильник (РС)) містить 16-розрядну адресу елементу пам'яті програм. До складу лічильника команд входять 16-розрядні буфер РС, регістр РС, схема інкремента, регістр адреси пам'яті.

Буфер РС здійснює зв'язок між 8-розрядною РШД і 16-розрядним регістром РС, в якому зберігається поточна 16-розрядна адреса пам'яті програм.

Схема інкремента збільшує поточне значення 16-розрядної адреси пам'яті програм на одиницю.

Регістр адреси пам'яті призначений для запису і зберігання виконавської 16-розрядної адреси пам'яті програм або 8/16-разрядного адреси зовнішньої пам'яті даних.

3.12.7. Регістр Вказівник даних РУД (DPTR) призначений для зберігання 16-розрядної адреси зовнішньої пам'яті даних. Складається з двох 8-разядных регістрів DPH і DPL, що входять в блок регістрів спеціальних функцій (таблиця 2). Вони програмно доступні і можуть використовуватися як два незалежних РОНов, якщо немає необхідності в зберіганні 16-розрядної адреси зовнішньої пам'яті даних.

3.12.8. Вказівник стека (SP) адресує вічка спеціальної області пам'яті даних (РПД), званої стеком. SP адресує “верхівку” стека - останній елемент стекової пам'яті, в яку записана інформація. Вказівник стека є 8-розрядним регістром, вміст якого при виконанні команд LCALL, ACALL збільшується на 2. При виконанні команд RET, RETI вміст Вказівника стека зменшується на 2. При виконанні команди PUSH direct вміст SP збільшується на 1, а при виконанні команди POP direct - зменшується на 1.

3.12.9. Регістр адреси РА (RAR) вічка РШД, що адресується. Програмно не доступний.

3.12.10. Регістри РРТС (TMOD) і РУСТ (TCON) служать для програмування і управління роботою таймерів-лічильників і системи переривань. Формати, позначення і призначення їх окремих розрядів приведені в таблицях 10.13.

3.12.11. Регістр РУПП (SCON), буфери ПД і ПРМ (SBUF) призначені для програмування і управління роботою послідовного інтерфейсу. Формати, позначення і призначення їх окремих розрядів приведені в таблицях 14, 15.

3.12.12. Регістри РМП (IE) і РП (IR) програмують і управляють роботою системи переривань ОЕОМ. Формати, позначення і призначення РМП і РП приведені в таблицях 7, 8.

3.12.13. Регістр управління потужністю РУМ (PCON) служить для програмного управління вжитком енергії від джерела живлення, а також швидкістю передачі по послідовному каналу ОЕОМ. Формати, позначення і призначення його окремих розрядів приведені в таблицях 16, 17.

Детальніше застосування цього регістра буде розглянуто в розділах 4.3; 8.

Таблиця 16 – Позначення розрядів регістра PCON

|

Біти

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Позначення

|

SMOD

|

- |

- |

- |

GF1

|

GF0

|

PD

|

IDL

|

Таблиця 17 – Призначення розрядів регістра PCON

|

Біти

|

Наїменов.

|

Призначення бітів

|

Примітка

|

|

7 |

SMOD

|

Біт подвоєння швидкості передачі: при установці в "1" – швидкість передачі подвоюється.

|

При роботі последовательного порту

|

|

6 |

- |

Резервний

|

|

|

5 |

- |

Резервний

|

|

|

4 |

- |

Резервний

|

|

|

3 |

GF1

|

Прапор загального призначення

|

|

|

2 |

GF0

|

Прапор загального призначення

|

|

|

1 |

PD

|

Біт включення режиму микропотребления "1" – режим мікроспоживання

|

Якщо в PD і IDL одночасно записана "1", перевага має PD

|

|

0 |

IDL

|

Біт холостого ходу "1" – режим холостого ходу

|

|

4. Особливості функціонування і застосування ОЕОМ в різних режимах