1.ЦИФРОВІ КОМБІНАЦІЙНІ ПРИСТРОЇ

1.1.Теоретичні відомості і розрахункові співвідношення

Пристрої, що оперують з двійковою (дискретною) інформацією, підрозділяються на два класи: комбінаційні і послідовнісні (часові).

Комбінаційні пристрої характеризуються відсутністю пам'яті. Сигнали на їх виходах у будь-який момент часу однозначно визначаються поєднанням сигналів на входах і не залежать від попередніх станів. Схемними ознаками таких пристроїв служить відсутність ланцюгів зворотного зв'язку, тобто замкнутих петель, для проходження сигналів з виходів на входи. Комбінаційні пристрої характеризуються великою різноманітністю, проте серед них можна виділити ряд типових, таких, що найчастіше зустрічаються на практиці. До них відносяться суматори, дешифратори, шифратори, перетворювачі кодів, мультиплексори, демультиплексори, схеми порівняння код та інші.

Суматори. Суматорами є функціональні цифрові пристрої, що виконують операцію складання чисел. У цифровій техніці додавання здійснюється в двійковому або, рідше, двійково-десятковому коді. По характеру дії суматори підрозділяються на комбінаційні (що не мають елементів пам'яті) і накопичувальні (такі, що зберігають результати обчислень). У свою чергу, кожен з суматорів, що оперує з багаторозрядними числами, залежно від способу їх складання може бути віднесений до послідовного або паралельного типу.

Складання багаторозрядних чисел в послідовних суматорах здійснюється порозрядно, послідовно в часі, а в суматорах паралельного типу — одночасно.

Як послідовні, так і паралельні суматори будуються на основі однорозрядних додавальних схем.

Процедура складання двох n-розрядних чисел ілюструється рис. 1.1. Складання виконується в кожному розряді окремо, але з урахуванням результату складання попереднього розряду. Так, складання цифр А1 і В1 молодшого розряду дає біт суми S1, і біт перенесення Р1. У наступному (другому) розряді відбувається складання цифр Pl, А2

іВ2, яке формує суму S2 і перенесення Р3. Операція триває, поки не буде складена кожна пара цифр в усіх розрядах. Результатом складання буде число S = Pn Sn ...S1 , де Рп

іS1 відображають 1 або 0, отримані в результаті порозрядною складання.

Рис. 1.1. Процедура складання двох n-розрядних чисел

З розглянутого принципу складання виходить, що для побудови п-разрядного суматора необхідно мати два типи однорозрядних схем, званих напівсуматором і повним суматором, або просто суматором. Напівсуматор має два входи А і В для двох доданків і два виходи: S (сума) і Р (перенесення). Позначенням напівсуматора служать букви HS (halfsum — напівсума). Він не враховує результату перенесення з попереднього розряду, тому може використовуватися тільки в першому розряді n- разрядного суматора. Напівсуматори застосовують також для побудови повного суматора.

Повний суматор має три входи: доданків і-го раздяда Ai і Ві, і перенесення з 0- (i −1)-го розряду Pi−1 .

Опис роботи півсуматора і повного суматора здійснюється за допомогою таблиць істинності (відповідності), які складаються відповідно до принципу роботи цих схем для суматора (табл. 1.1).

|

|

Табл. 1.1 |

|

|

|

|

|

|

|

|

Виходи |

|

|

№ |

|

Входи |

|

|

||

Ai |

Ві |

Pi−1 |

Рі |

Sі |

|

|

|

|

|||||

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

2 |

0 |

1 |

0 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

! |

0 |

|

6 |

1 |

1 |

0 |

1 |

0 |

|

7 |

1 |

1 |

1 |

1 |

1 |

|

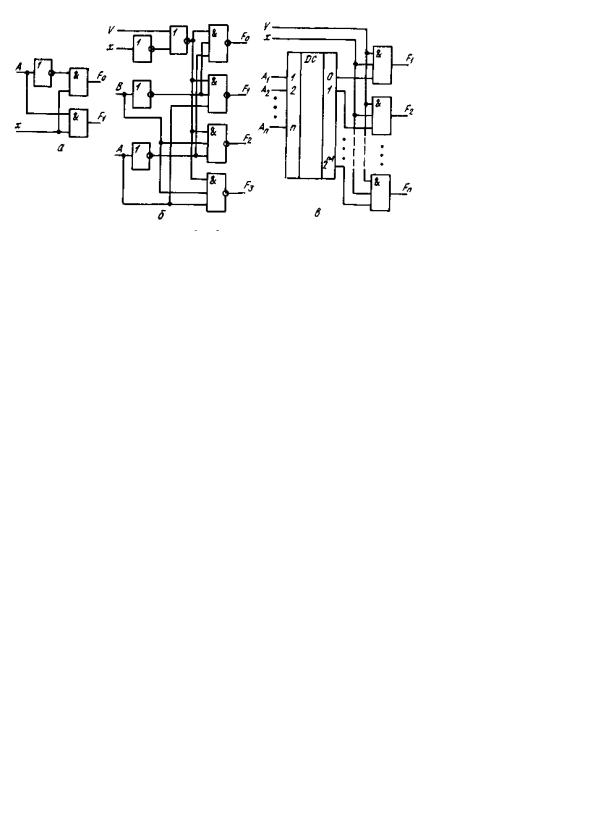

Схема послідовного багаторозрядного суматора приведена на рис. 1.2, а. При послідовному введенні використовується один, загальний для всіх розрядів повний суматор з додатковим ланцюгом затримки. Обидва доданки кодуються послідовностями імпульсів, які синхронно вводяться в суматор через входи А і В, починаючи з молодших розрядів. Ланцюг затримки забезпечує зберігання імпульсу перенесення Pi на час одного такту, тобто до приходу пари доданків наступного розряду, з якими він буде складений. Переваги послідовних суматорів — малі апаратурні витрати. Недолік — порівняно низька швидкодія, оскільки одночасно додається лише пара доданків.

Рис. 1.2. Схема послідовного багаторозрядного суматора

Схема паралельного n-розрядного суматора з послідовним переносом приведена на рис. 1.2, б. Вона складена на однорозрядних суматорах, перший з яких працює в режимі півсуматора, для чого на його вході переносу Pi встановлено потенціал U0. Доданки Ai і Ві; складаються у всіх розрядах одночасно, а перенос Р надходить із закінченням операції складання в попередньому розряді.

Швидкодія таких суматорів обмежується затримкою переносу tn кожного розряду. Сумарний час затримки перенесення tnΣ = n tn , оскільки формування сигналу

переносу на виході старшого розряду не може відбутися до тих пір, поки сигнал переносу молодшого розряду не розповсюдиться послідовно по всій системі.

Час перенесу істотно зменшується в схемах з паралельним (прискореним) перенесенням, принцип якого полягає в тому, що для кожного двійкового розряду додатково формуються два сигнали: утворення переносу G і розповсюдження переносу H, відповідно рівні:

Gi = Ai Bi , Hi = Ai + Bi .

Якщо Gi =1, тобто Ai = Bi =1, в і-му розряді формується сшнал перенос Pі в

наступний вищий розряд незалежно від формування функцій суми в попередніх розрядах. Якщо хоч би один з доданків Ai або Ві, - рівний 1 (тобто Hi = 1), то перенесення в наступний розряд відбудеться за наявності сигналу переносу з попереднього розряду. Якщо функції розповсюдження перенесення в двох сусідніх розрядах рівні 1, тобто Hi = Hi+1 =1, і при цьому існує сигнал переносу Pi−1 з

попереднього розряду, то перенесення проводиться безпосередньо в розряд з номером i + 2.

Процес і схема формування прискореного перенесення описуються рівнянням

Pi = Gi + HiGi−1 + Hi Hi−1Gi−2 +... + Hi Hi−1...H2 H1P0

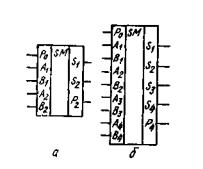

Суматори входять в номенклатуру декількох серіїв мікросхем ТТЛ і КМОН Умовні позначки мікросхем К155ИМ2 і К155ИМЗ приведені на рис 1.3, а і б.

Рис. 1.3. Умовні позначки мікросхем К155ИМ2 і К155ИМЗ

При послідовному з'єднанні мікросхем з метою нарощування розрядності вихід перенесення безпосередньо з’єднують з входом переносу мікросхем, що належать вищим розрядам.

Дешифратори. Дешифратор (декодер) — це комбінаційний пристрій з декількома входами і виходами, у якого певним комбінаціям вхідних сигналів відповідає активний стан одним з виходів. Дешифратори перетворюють двійковий і двійково-десятковий коди в унітарний код, тобто код двійкового п-розрядного числа, представленого 2n розрядами тільки один з розрядів якого рівний 1.

Дешифратори можуть бути повними і неповними У повного дешифратора n входам відповідає 2n виходів. У неповного дешифратора число виходів m < 2n.

Відомі три основні структури дешифраторів: матрична (лінійна), каскадна і пірамідальна.

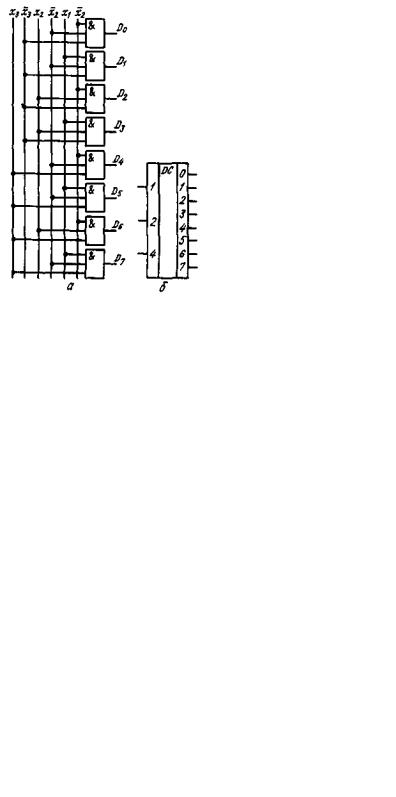

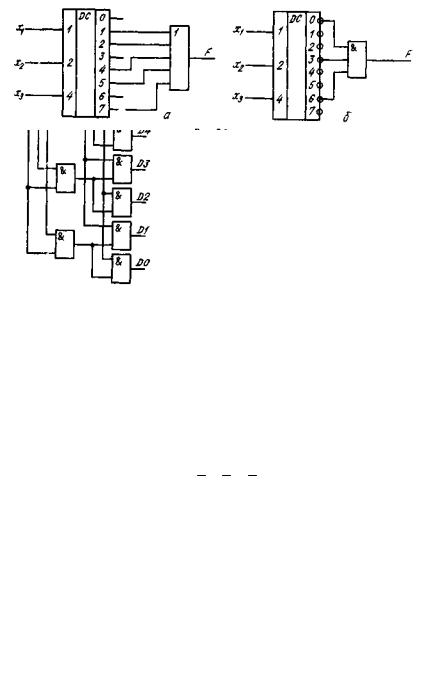

Матричні (лінійні) дешифратори складаються з 2n логічних схем збігу кожна з яких має n входів. На входи цих логічних елементів подаються всі можливі комбінації прямих і інверсних розрядів числа X, що дешифрується. Приклад матричного дешифратора 3×8 приведений на рис. 1.4, а, а його умовне позначення — на рис 1.4, б.

Рис. 1.4

Матричні дешифратори мають найвищу швидкодію. Час затримки появи сигналу на виході в дешифраторах з n-вхідними логічними елементами складає час

затримки одного елементу (tЗΣ = tЗ ), але їх недолік — велике число входів логічних

елементів із зростанням розрядності Цей недолік є менш істотним при використанні діодної логіки. Приклад схеми дешифратора 3×8, виконаного на діодній логіці, приведений на рис. 1.5. Для того, щоб такий дешифратор мав властивість наращуваності для збільшення розрядності вхідного числа, він повинен будуватися з однакових схем (на рис. 1.5 обведені пунктирною лінією). Так, матричний дешифратор 2×4 може бути побудований на основі двох таких схем, дешифратор 3×8 — на основі трьох схем, дешифратор 4×16 — на основі 8 схем, дешифратор 5×32 — на основі 20 схем і т. д.

Рис. 1.5. Схема дешифратора 3×8, виконаного на діодній логіці

При каскадній побудові дешифраторів вхідне число розбивається на декілька

підчисел, кількість яких може знаходитися в діапазоні від 2 до n |

|

. При непарному |

2 |

|

|

значенні n кількість підчисел округляється у бік найближчого більшого цілого числа. Для кожною підчисла формуються всі його мінтерми шляхом побудови окремих матричних дешифраторів. Всі дешифратори підчисел складають перший каскад дешифратора. У кожному подальшому каскаді утворюють кон'юнкції мінтермів з

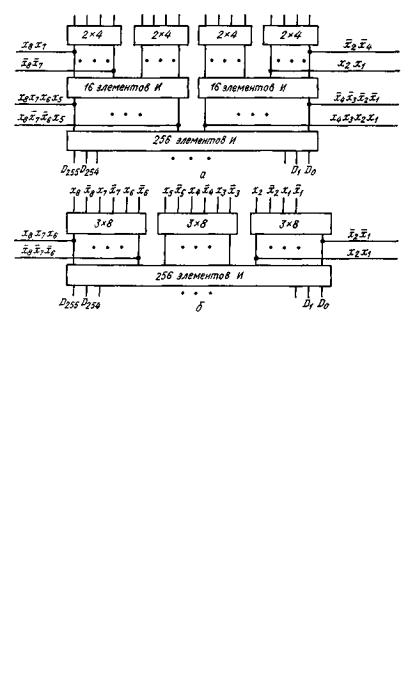

попереднього каскаду. Залежно від n і числа входів логічних елементів каскадний дешифратор можна виконувати в різних варіантах що відрізняються числом каскадів, числом матричних дешифраторів і т. iн. Приклади каскадного дешифратора на дво- і тривходовых елементах при n = 8 приведені на рис. 1.6, а і б.

Рис. 1.6. Каскадні дешифратори: а - на двохвходовых елементах, б – на трьохвходовых елементах

Швидкодія каскадних дешифраторів визначається числом каскадів m, а сумарний час затримки tЗΣ = m tЗ .

Пірамідальний дешифратор відрізняється від каскадного тим, що в його каскадах кожна конституента одиниці формується як кон'юнкція однієї з конституент попереднього каскаду і одного з розрядів вхідного числа, яке ще не використовувалось для формування конституент. Принцип побудови пірамідального дешифратора ілюструється рис. 1.7. Кількість каскадів пірамідального дешифратора рівна n −1, а

сумарний час затримки сигналу tЗΣ = tЗ (n −1).

Рис. 1.7. Побудова пірамідального дешифратора

У інтегральній схемотехніці особливий інтерес представляють методи синтезу дешифраторів на однотипних модулях. Для реалізації дешифратора на n входів з набору однотипних модулів будується багатокаскадна схема. Принцип її побудови пояснюється рис. 1.8. До входів, що керують, кожним з модулів М1, М2,…, M

увімкнено по одному виходу від кожного дешифратора DC1, DC2,…, DCr, де s — число інформаційних входів модуля, r — число керуючих входів модуля.

Рис. 1.8. Багатокаскадна схема побудови дешифратора

Дешифратори можна використовувати для реалізації логічних функцій згідно заданій таблиці істинності. Хай, наприклад, функція F (x1, x2 , x3 ) задана одиничними

значеннями на номерах наборів 1, 2, 4, 5, 7 і нульовими на наборах 0, 3 і 6. Досконала диз'юнктивна форма цієї функції має вигляд

F = m1 +m2 +m4 +m5 +m7 |

(1.1) |

||||||||

де mi — конституента одиниці i-гo набору. |

|

||||||||

Досконала кон'юнктивна форма функції |

|

||||||||

|

|

|

|

|

|

|

|

|

|

F |

= |

m |

0 |

m |

3 |

m |

6 |

(1.2) |

|

Для побудови схеми досить мати дешифратор 3×7 і з'єднати його прямі виходи відповідно рівняння (1.1) (рис. 1.9, а) або інверсні виходи згідно рівнянню (1.2) (рис. 1.9, б).

Рис. 1.9. Приклад реалізації логічної функції за допомогою дешифратора

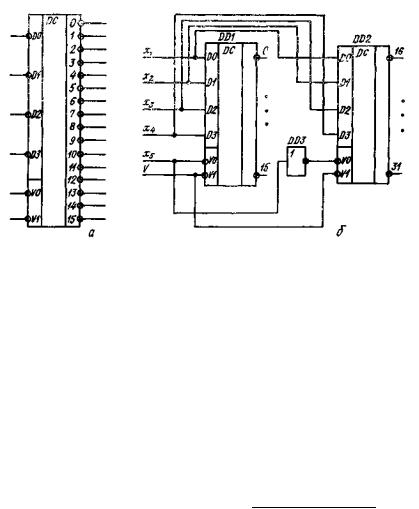

Дешифратори входять у вигляді функціональних вузлів до складу декількох серіїв ТТЛ і КМОН. Як приклад на рис. 1.10, а приведено умовне позначення мікросхеми дешифратора 4×16 типу К155ИД3. Мікросхема має чотири адресні входи D0…D3, два входи дозволу і 16 виходів, пронумеровані від 0 до 15. Якщо на обох входах дозволу підтримується рівень V0 = V1 = 0, мікросхема працює як дешифратор. Потенціал U1 на будь-якому з входів дозволу встановить рівень U1 на всіх виходах незалежно від стану входів. Для нарощування розрядності (наприклад, отримання дешифратора 5×32) шини молодших чотирьох розрядів з’єднують з входами D0…D3 обох мікросхем, а сигнали старшого розряду подають в прямому вигляді на один з входів дозволу першої мікросхеми, в інверсному — на вхід дозволу другої. Інші входи дозволу заземлюють.

Рис. 1.10. Дешифратори: а – умовна позначка мікросхеми дешифратора 4×16 типа К155ИД3, б - нарощування розрядності дешифратора до 5×34 (б)

Шифратори. Шифратором називається комбінаційний пристрій, що перетворює унітарний код, який подається на вхідні шини, у відповідний код на вихідних шинах. Таким чином, шифратори виконують функцію, зворотну тій, що виконується дешифратором. Якщо з вихідних шин шифратора знімається n-розрядний код, то максимальне число вхідних шин визначається числом можливих кодових комбінації і складає 2n.

Розглянемо як приклад синтез шифратора з п'ятьма входами, що перетворює унітарний код в двійковий. Фрагмент таблиці істинності цього шифратора приведений у вигляді табл. 1.2. На решті наборів вхідних змінних вихідні функції мають байдужі значення.

Табл. 1.2

|

|

Входи |

|

|

|

Виходи |

|

|||

х1 |

х2 |

х3 |

|

х4 |

х5 |

F1 |

|

F2 |

|

F3 |

0 |

0 |

0 |

|

0 |

1 |

0 |

|

0 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

|

1 |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

|

1 |

|

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

|

0 |

|

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

|

0 |

|

1 |

Рівняння, що описують функції F1, F2 і F3, найзручніше представити у вигляді

F1 = x5 + x3 + x1, |

|

|

F2 |

= x4 + x3, |

(1.3) |

F3 |

= x2 + x1. |

|

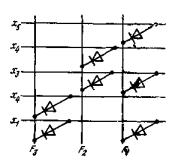

Найпростіше шифратори реалізуються на діодній логіці. Так, для приведеного прикладу діодний шифратор повинен мати п'ять вхідних і три вихідних шини, причому кожна вхідна шина з'єднується через діоди з вихідними відповідно до рівнянь (1.3) (рис. 1.11) або безпосередньо по таблиці істинності (табл. 1.2).

Рис. 1.11. Шифратор з п’ятьма входми

Якщо шифратори, що розробляються на окремих логічних елементах, перетворюють унітарний вхідний код практично в будь-який вихідний паралельний код відповідної розрядності, то шифратори, виконані у вигляді мікросхем, як правило, перетворюють сигнал, поданий тільки на один вхід (наприклад, 9), у вихідний паралельний двійковий код (в даному випадку 1001)

У мікросхемах шифраторів для того, щоб він відгукувався на сигнал тільки одного входу, його схему роблять пріоритетною. Тоді вихідний код повинен відповідати номеру «старшого» входу, що отримав сигнал. Припустимо що активні рівні поступили на входи з номерами 3, 4 і 9 Старший по номеру вхід тут 9, він має пріоритет, тому вихідний код шифратора 1001.

Перетворювачі кодів (ПК). Призначені для перетворення одного паралельного коду в іншій. Вони використовуються для шифруванняі дешифрування цифрової інформації і можуть мати n входів і k виходів Співвідношення між числами n і k можуть бути будь-якими n = k, n < k, n > k.

За призначенням ПК можна розділити на два типи з неваговим і з ваговим перетворенням кодів. У перетворювачах першого типу відсутній числовий взаємозв'язок вхідного і вихідного коду, а має місце символьний взаємозв'язок наприклад перетворення двійково-десяткового коду в код семисегментного індикатора десяткових цифр. Перетворювачі другого типу використовуються, як правило, для перетворення числової інформації, тоді між числами вхідного і вихідного коду має місце заданий математичний взаємозв'язок.

Перетворення n-елементного коду в k-елементний можна здійснити з попереднім дешифруванням першого коду і без нього. В першому випадку спочатку дешифрується n-елементний код і на кожній з 2n вихідних шин виходить сигнал, відповідний одній з вхідних кодових комбінацій. Потім кожен з вихідних сигналів кодується в k-елементному коді за допомогою шифратора.

Розглянемо як приклад перетворення трьохелементного коду в п'ятиелементний згідно табл. 1.3. Схема, що реалізовує такий ПК, показана на рис. 1.12. Як дешифратор використовується повний дешифратор 3×8, а як шифратор — діодний матричний шифратор.

Табл. 1.3

Трьохелементний код |

|

П’ятиелементнийкод |

|

||||

х1 |

х2 |

х3 |

y1 |

y2 |

y3 |

y4 |

y5 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

G |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

У другому випадку при побудові ПК без попереднього дешифрування вхідного коду досить відповідно до заданих умов перетворення скласти структурні формули для кожного з елементів того коду в якому слід перетворити заданий код, і потім скласти схему ПК.

ПК з неваговим перетворенням коду, як правило описуються таблицями істинності що однозначно визначають вхідний і вихідний коди.

Рис. 1.12. Схема перетворювача трьохелементного коду в п'ятиелементний

ПК з ваговим перетворенням достатньо часто використовуються для числового перетворення однієї безперервної функції в іншу (наприклад, sinα в cosα ) шляхом їх дискретизації, визначення вхідних і вихідних кодів кожної функції в одні і ті ж моменти дискретизації, а вже на підставі цих кодів будується схема ПК. У цих випадках розрядність кодів визначає точність перетворення, оскільки з її збільшенням збільшується точність апроксимації безперервної функції її дискретним еквівалентом.

Myльтиплексори. Myльтиплексором називається комбінаційний пристрій призначений для комутації у бажаному порядку сигналів з декількох вхідних шин на одну вихідну. За допомогою мультиплексора здійснюється часове розділення інформації, що поступає по різних каналах. Його можна уподібнити безконтактному багатопозиційному перемикачу.

Входи мультиплексора діляться на інформаційні, адресні і вирішуючі (стробувальні). На інформаційні входи подається інформація передавана на вихід мультиплексора. Адресні входи допомагають вибрати потрібний інформаційний вхід, а на вирішуючий вхід подається стробуючий сигнал, що вирішує підключення вибраного входу на один загальний вихід (рідше два взаємоінверсних). Вирішуючий вхід, як правило, один, а число інформаційних і адресних входів взаємозв'язане. Якщо число адресних входів n, то з їх допомогою можна комутувати 2n каналів тобто число інформаційних входів 2n.

Наявність вирішуючого входу дозволяє синхронізувати роботу мультиплексора з роботою інших вузлів, а також нарощувати його розрядність.

Робота мультиплексора описується наступним логічним рівнянням

2n −1

F =V Dimi (1.4)

i=0

де Di — вхідні інформаційні сигнали мультиплексора, mi — мінтерми утворені змінними адресних шин, V — стробуючий сигнал.

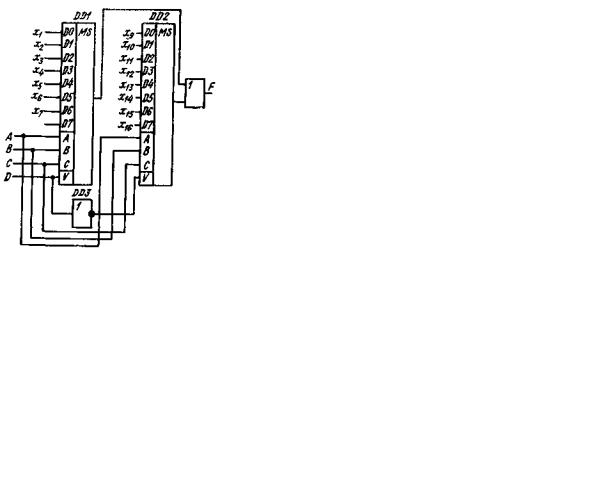

З цього рівняння виходить, що структура мультиплексора складається з 2n схем збігу кожна з яких має n адресних, один інформаційний і один стробуючій входи, та однієї схеми АБО з n входами, яка підсумовує всі вихідні сигнали схем збігу. Вихід схеми АБО є виходом мультиплексора. Приклад схеми мультиплексора з чотирма інформційними входами «чотири лінії до однієї» (4×1) приведений на рис. 1.13, а і

умовні позначки мікросхем мультиптексоров К155КП7, К155КП1 і К155КП5 — на рис. 1.13, б, в, г

Рис. 1.13. Схема мультиплексора 4×1(а), та умовні позначки мікросхем мультиптексоров К155КП7 (б),

К155КП1 (в) і К155КП5 (г)

Мультиплексори КМОН будуються на основі дешифраторів і двоспрямованих вентильних ключів. Оскільки ключі КМОН можуть проводити струм в двох напрямках, мультиплексори на них можуть бути використані і в оберненому режимі в якості демультиплексорів — пристроїв, комутуючих сигнали від однієї шини до декількох. Загальне вхід інформаційних сигналів використовується як вихідний для мультиплесора використовується як вихідний для мультиплексора і вхідний для демультиплексора. Ці пристрої нерідко називають мультиплексордемультиплексорами, комутаторами, селекторами.

Мультиплексори, що випускаються у вигляді окремих мікросхем, мають обмежене число інформаційних входів (не більше 16). Для збільшення числа входів мультиплексори нарощують об'єднанням декількох мультиплексорів в пірамідальну (деревовидну) або паралельну системи.

Рис. 1.14. Структура пірамидального мультиплексора

Пірамідальні мультиплексори будуються за каскадним принципом. Число каскадів визначається необхідним числом входів і числом входів реальних мікросхем та може бути 2, рідше 3 або більше. На адресні входи мультиплексорів першого каскаду подаються молодші розряди коду адреси. Виходи мультиплексорів першого каскаду

подаються на інформаційні входи мікросхем другого каскаду. На адресні входи цих мікросхем вмикаються наступні за старшинством розряди коди адреси і так далі. В останньому k-му каскаді опиняється одна мікросхема мультиплексора, на інформаційні

входи якої підключаються виходи всіх мультиплексорів (k −1)-го каскаду, а на адресні

— старші розряди коду адреси. За наявності стробуючих входів всі вони об'єднуються загальною шиною. Приклад пірамідальної структури приведений на рис. 1.14. Недоліками пірамідальних структур є підвищена витрата мікросхем і зменшення швидкодії.

Якщо мікросхема мультиплексора має вирішуючий вхід, то за рахунок його використання як інформаційного можна наростити розрядність, вмикаючі окремі мікросхеми паралельно. В цьому випадку вирішувальні входи всіх мультиплексорів вмикаються до виходів дешифратора, на входи якого подаються старші розряди коду адреси. Адресні шини молодших розрядів об'єднуються через схему АБО. Приклад об'єднання двох мультиплексорів 8×1 в один 16×1 приведений на рис. 1.15. Для цієї схеми достатній дешифратор 1×2, який реалізується на інверторі.

Рис. 1.15. Об’єднання двох мультиплексорів

Швидкодія таких мультиплексорів істотно вище і не залежить від розрядності. Час затримки вхідного сигналу tЗΣ практично рівний часу затримки одного корпусу,

тобто tЗΣ ≈ tЗ .

Мультиплексори можуть використовуватися не тільки як комутатори, але і з іншою метою. Одна з перспективних областей їх використання — реалізація комбінаційних, а у ряді випадків і послідовнісних логічних схем. На мультиплексорах

можна реалізувати будь-яку логічну функцію, що містить до (n +1) змінних, де n —

число адресних входів. Розглянемо, наприклад, логічну функцію F трьох змінних, задану табл. 1.4.

Табл. 1.4

№ |

х2 |

x1 |

х0 |

F |

Рівняння виходу |

|

0 |

0 |

0 |

0 |

1 |

F = x0 |

|

1 |

0 |

0 |

1 |

0 |

||

|

||||||

2 |

0 |

1 |

0 |

1 |

F =1 |

|

3 |

0 |

1 |

1 |

1 |

||

|

||||||

4 |

1 |

0 |

0 |

0 |

F = x0 |

|

5 |

1 |

0 |

1 |

1 |

||

|

||||||

6 |

1 |

1 |

0 |

1 |

F = x0 |

|

7 |

1 |

1 |

1 |

0 |

||

|

Якщо змінні х1 і х2 взяти за адресні сигнали, то значення функції F залежить від значення сигналів, встановлених на відповідних інформаційних входах мультиплексора. При x1 = x2 = 0 з табл. 1.4 видно, що F = x0 . При x1 =1 , x2 = 0

незалежно від значення х0 F =1. При x1 = 0 , x2 =1 F = x0 , при x1 = x2 =1 F = x0 . Таким чином, якщо на інформаційні входи подати інформацію D0 = x0 , D1 =1,

D2 = x0 , D3 = x0 , то така схема реалізує шукану функцію (рис. 1.16).

Рис. 1.16. Реалізація логічної функції на мультиплексорі

Демультиплексори. Демультиплексори у функціональному відношенні протилежні мультиплексорам. У них сигнали з одного інформаційного входу розподіляються в необхідній послідовності по декількох виходах відповідним кодам на адресних входах. При n адресних входах демультиплексор може мати до 2n виходів.

Принцип роботи демультиплексора пояснює рис. 1.17, а, де х — інформаційний, А — адресний входи. Залежно від сигналу А по адресному входу відкритий верхній або нижній логічний елемент і через нього сигнал х підключається або до виходу F0, або до виходу F1. Як і мультиплексори, демультиплексори доповнюються керуючім входом V. Приклад демультиплексора 1×4 представлений на рис. 1.17, б. Демультиплексори можуть також бути виконані з використанням дешифратора і додаткової логіки (рис. 1.17, в). В цій схемі дешифратор виконує роль адресного пристрою, за допомогою якого вибирається відповідна схема І, на інші входи кожної схеми І подаються загальні інформаційний х і сигнал дозволу V.

Рис. 1.17. Демультиплексор 1×2 (а), 1×4 (б), на дешифраторі з додатковою логікою

Якщо у демультиплексора 1×4 на інформаційний вхід подати сигнал U 0 або на

вирішуючий вхід U1 , то він працюватиме як дешифратор 2×4. Отже, дешифратор можна розглядати як обернений по входах демультиплексор, у якого адресні входи стали інформаційними, а інформаційний вхід — входом дозволу.

Нарощування розрядності демультиплексора принципіально не відрізняється від аналогічного завдання у мультиплексорів. Так в пірамідальній (каскадній) схемі нарощування проводиться ступенями, і кожна подальша ступінь має більше елементів, ніж попередня, а число елементів подальшої ступені визначається числом інформаційних виходів попередньої ступені. Приклад складання демультиплексора 1×32 з демультиплексора 1×4 і чотирьох 1×8 показаний на рис. 1.18.