- •Міністерство транспорту та зв'язку України Державний економіко-технологічний університет транспорту Кафедра “Інформаційні системи й технології”

- •Київ-2007

- •1.Завдання Розробити спеціалізовану мікропроцесорну систему у складі *

- •2. Основні функціонально-конструктивні пристрої

- •2.1. Мікропроцесор.

- •2.1.1. Загальні відомості.

- •2.1.2. Призначення виводів мікропроцесора (на прикладі мпс к1810вм86).

- •2.1.3. Структура мікропроцесора

- •2.1.4. Функціонування мікропроцесора

- •2.2Арифметичний співпроцесор.

- •2.2.1. Призначення виводів віс к1810вм87

- •2.2.2. Функціонування арифметичного співпроцесора

- •2.2.3. Спеціальнє використання арифметичного співпроцесора

- •2.3.Спвб:

- •2.3.1. Структура спвб

- •2.3.2Функціонування спвб

- •Поле р визначає пріоритет каналу. •

- •2.3.3. Система команд спвв

- •3. Розрахунок адресного простору пам’яті та портів

- •4. Організація переривань

- •5. Структура однопроцесорної системи

- •7.1. Генератор тактових імпульсів

- •7.2. Буферні регістри й шинні формувачі.

- •7.3. Контролер системної шини

- •7.4. Арбітр шин

- •8.1. Контролер прямого доступу пам'яті.

- •10 Література

- •03049, М. Київ-49, вул. Миколи Лукашевича, 19

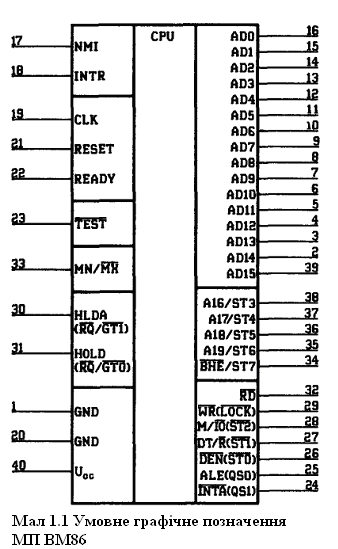

2.1.2. Призначення виводів мікропроцесора (на прикладі мпс к1810вм86).

Призначення виводів ВІС залежить від режиму роботи МП (мал. 1.1). Вісім виводів має подвійне позначення, причому позначення в дужках відповідають максимальному режиму. У табл. 1.5 наведені призначення виводів МП, що є загальними для обох режимів, у табл. 1.6 – призначення виводів, використовуваних тільки в мінімальному режимі, а в табл. 1.7 – використовуваних тільки в максимальному режимі. Буквою Z відзначені три стабільні виходи, які переводяться в третій (високоомний) стан при переході МП у режим стан захоплення; у дужках наведені альтернативні позначення виводів, що зустрічаються в літературі.

Розглянемо докладніше функціональне призначення сигналів МП і особливості їхнього використання спочатку в мінімальному режимі.

AD15—AD0 – мультиплексна (сполучена) двонаправленна шина адреси/даних, по якій з поділом у часі передаються адресна інформація й дані. У першому такті циклу шини – циклу звертання до ЗУ або зовнішнього пристрою (ВУ) – МП видає на цю шину молодші 16 біт адреси пам'яті або повну адресу зовнішнього пристрою. Ця адреса обов'язково повинна бути зафіксована і збережена протягом усього циклу, для чого використовується зовнішній регістр-засувка, куди записується адресна інформація за допомогою строба адреси ALE. Регістр-засувка повинен мати три стабільні вихідні буфери й забезпечувати малий час перемикання при великій навантажувальній здатності. У другій половині циклу шини по лініях AD15-AD0 передаються адреси даних або байти команд, супроводжувані стробом даних DEN.

A19/S6-A16/S3 – мультиплексні вихідні лінії адреси/стану. У першому такті на ці лінії видаються старші 4 біт адреси пам'яті, а при адресації ВУ – нулі. В інших тактах циклу шини МП видає на ці лінії сигнали стану S6-S3. Код на лініях S4, S3 визначає сегментний регістр, що бере участь у формуванні фізичної адреси пам'яті, тобто вказує сегмент пам'яті, до якого виробляється обіг у поточному циклі (табл. 1.8). Слід зазначити, що при звертанні до ВУ, коли сегментні регістри не беруть участь у формуванні адреси, установлюється значення S4=l, S3=0.

Таблиця 1.2

|

Позначення |

Призначення |

Тип |

|

AD15-AD0 |

Лінії шини адреси/даних (ШАЛ) |

Вихід (z) |

|

A16/S3 A17/S4 A18/S5 A19/56 |

Лінії адреси/стану. Протягом такту Т1 включають старші біти, адреси при звороті до пам’яті або ОП, протягом Т2, Т3, TW и T4 – інформацію про стан мікропроцесора (МП) |

Вихід (z) |

|

BNE/S7 |

Дозвіл старшого байту шини/стану |

Вихід (z) |

|

RD |

Читання, строб, що вказує на те, що МП виконує цикл читання |

Вихід (z) |

|

RDY |

Готовність, підтвердження того, що адресований пристрій готовий до взаємодії з МП при передачі даних |

Вхід |

|

INTR |

Запит переривання, по якому МП переходить на підпрограму обробки переривання, якщо є дозвіл |

Вхід |

|

NMI |

Немаскуєме переривання, викликає переривання по фіксованому вектору (тип 2); не може бути заборонено внутрішніми засобами МП (програмно) |

Вхід |

|

TEST |

Вхідний сигнал, який перевіряється командою WAIT, що переводить МП в стан чекання, якщо TEST = 1 |

Вхід |

|

CLK, (CLC) |

Тактові імпульси, які забезпечують синхронізацію роботи МП |

Вхід |

|

RESET (CLR) |

Сброс, примушує МП швидко зупинити дії, що виконуються і потім поновити виконання програми спочатку |

Вхід |

|

MN/MX |

Мінімальний/максимальний, він забезпечує відповідний режим роботи МП |

Вхід |

Сигнали S4, S3 можуть використовуватися для розширення адресного простору системи. У цьому випадку окремий банк пам'яті обсягом 1 МБ виділяється кожному із чотирьох сегментів. До ліній S4, S3 підключається дешифратор, що вибирає відповідний банк пам'яті. Такий прийом забезпечує

розширення адресної пам'яті до 4 МБ і захист від помилкового запису в сегмент, що перекривається з іншими сегментами.

Сигнал S5 відповідає стану прапора дозволу переривань IF:0 – переривання заборонені, 1 – переривання дозволені. Цей сигнал аналогічний виходу дозволу переривання INTR мікропроцесора ВМ80. Сигнал S6 не

Таблиця 1.3

|

Позначення |

Призначення |

Тип |

|

INTA |

Підтвердження переривання, стробірує зчитування вектору (типу) переривання |

Вихід

|

|

ALE (STB) |

Дозвіл регістру-прищеплення адреси, стробірує появу адресної інформації у такті Т1 на ШАД |

Вихід |

|

DEN (DE) |

Дозвіл даних, стробірує появу даних на шині адреси/даних |

Вихід (z)

|

|

DT/R (OP/IP) |

Передача/прийом даних, з’ясовує напрям пересилки даних по ШАД |

Вихід (z)

|

|

М/IO |

Звернення до ЗП чи ВП у даному циклі шини |

Вихід (z) |

|

WR |

Запис, строб, що вказувє на те, що МП виконує цикл запису |

Вихід (z) |

|

HOLD |

Запит захвату, вказує на те, що деякий пристрій запитує шини МП |

Вхід |

|

HLDA |

Підтвердження захвату, вказує на те, що КП перевів свої шини адреси/даних, адреси/стану та управління ж z-стану |

Вихід |

використовується й завжди дорівнює нулю. Дозвіл старшого байта формується в першому такті циклу одночасно з адресною інформацією.

Активний сигнал нульового рівня означає, що по старшій половині AD15-AD8шини адреси/даних передаються 8-бітові дані. СигналHLDAзамикається в зовнішньому регістрі адреси й використовується як додатковий адресний вихід, що визначає доступ до старшого банку пам'яті або до ВУ з байтовою організацією, підключеній до старшої половини шини AD. Спільне використанняHLDAй молодшою лінією адресиАТдля дешифрації адресу дозволяє здійснювати передачу слів або окремих байтів по шиніAD(табл. 1.9). Відзначимо, що після закінчення сигналуHLDAна вихід подається резервний сигнал стануS7, що не має певного значення

ALE – строб адреси (дозвіл замикання адреси), видається на початку кожного циклу шини й використовується для запису адреси в регістр-засувку, тобто для демультиплексування шини AD.

DEN (або DE) – строб даних (дозвіл передачі даних). Видається в циклах читання, записи й дозволи виходу шинних формувачів.

RD – читання, ідентифікує виконання циклу читання із ЗУ або ВУ (залежно від значення сигналу М/IO). Указує цим пристроям на необхідність видачі даних на шину.

|

Таблиця 1.4 | ||

|

Позначення |

Призначення |

Тип |

|

S2, S1, S0 (ST2-ST0) |

Лінії стану, характеризують тип виконуваного циклу; необхідні для вироблення керуючого сигналу |

Вихід (z) |

|

RQ/GT0 RQ/GT1 RQ/E0 RQ/E1 |

Запит/надання, використовується для обміну сигналами між процесорами в багатопроцесорній системі, для керування процедурою використання шин |

Вхід/вихід |

|

LOCK |

Блокування (зайнятість) шини, інформує інші процесори та пристрої про те, що вони не повинні опитувати шину |

Вихід |

|

QS1,QS0 |

Стан черги, указує стан внутрішньої 6-байтовой черги команд МП |

Вихід |

|

Таблиця 1.5 | ||

|

S4 |

S3 |

Сегментний регістр |

|

0 |

0 |

ES |

|

0 |

1 |

SS |

|

1 |

0 |

CS |

|

1 |

1 |

DS |

|

Таблиця 1.6 | ||

|

BHE |

А0 |

Розрядність даних |

|

0 |

0 |

Все слово, ( обидва байти) |

|

0 |

1 |

Старший байт D15-D8, непарна адреса |

|

1 |

0 |

Молодший байт D7-D0, парна адреса |

|

1 |

1 |

Нема звернення |

WR – запис, указує на виконання циклу запису в ЗУ або ВУ й супроводжує дані, видавані мікропроцесором на шину.

М/IO є ознакою звертання до ЗУ (М/IO=1) або ВУ (М/IO = 0) і використовується для розподілу адресного простору пам'яті і уведення/виводу. Значення М/IO = 0 з'являється тільки при виконанні команд уведення (IN) і виводу (OUT).

DT/R – передача/прийом даних, визначає напрямок передачі по шині AD:DT/R = 1 – запис даних із МП в ОЗУ або ВУ, DT/R = 0 – читання даних із ЗУ або ВУ в МП. Призначений для керування шинними формувачами й діє протягом усього циклу шини, як і сигнал М/IO. Відмітимо, що напрямок передачі даних через шинні формувачі може також визначатися за допомогою сигналів RD і WR, але вони мають меншу тривалість і тому менш зручні.

HOLD – запит шини (запит захоплення) від зовнішньої підсистеми (ВУ або контролера прямого доступу до пам'яті).

HLDA – підтвердження захоплення шини, видається у відповідь на сигнал HOLD після призупини обчислювального процесу в МП і переведення шини AD і деяких керуючих сигналів в z-стан. При HLDA=1 підсистема, ініціюючий запит захоплення, може використовувати шину самостійно. Після встановлення HOLD = 0 ЦП видає сигнал HLDA = 0, відновляє керування шиною й продовжує роботу із програми.

NMI – немаскуєме переривання, розпізнається мікропроцесором по завершенню поточної команди незалежно від стану прапора дозволу переривання IF. Цей вхід призначений для сигналізації о деяких критичних ситуаціях, наприклад про аварійне відключення мережного живлення.

INTR – запит переривання (маскуєме), опрашивается центральним процесором наприкінці виконання кожної команди, якщо переривання дозволені (IF=1) і фіксується у внутрішньому тригері. Звичайно на вхід INTR подається запит від програмувального контролера переривань К1810ВН59А. Якщо IF = 0, то запит по входу INTR ігнорується.

INTA – підтвердження запиту переривання, формується у відповідь на прийнятий запит переривання INTR, виконує функцію сигналу RD у циклі підтвердження переривання й стробує зчитування покажчика адреси (вектора) переривання. У кожному випадку підтвердження переривання виконуються два цикли INTA, з яких перший є попереднім і не супроводжується читанням інформації.

RDY – готовність, вказує на те, що адресуемий в даному циклі пристрій готовий до обміну даними. Якщо пристрій не готовий до взаємодії із МП, воно видає сигнал RDY = 0, і МП переходить у стан очікування. У цьому випадку між тактами ТЗ і Т4 цикли шини з'являється необхідне число тактів очікування TW. Після установки сигналу RDY= 1 МП виходить зі стану очікування й відновляє роботу.

TEST— перевірка, використовується разом з командою очікування WAIT, виконуючи яку МП перевіряє рівень сигналу TEST. Якщо TEST = 0, МП переходить до виконання наступної один по одному команди. Якщо TEST = 1, МП уводить холості такти TI і періодично, з інтервалом 5Т, перевіряє значення сигналу TEST. Команда WAIT і сигнал TEST забезпечують синхронізацію роботи МП із зовнішніми сигналами: TEST – вхід програмної перевірки, RDY – вхід апаратної перевірки готовності пристроїв у системі.

CLK - Тактова синхронізація (тактування). Сигнал синхронізації від зовнішнього генератора тактових імпульсів, призначений для синхронізації МП. Використовується серія тактових імпульсів CLK з періодом повторення Т, рівним 200-500 нс.

RESET – скидання, переводить МП у певний початковий стан, у якому скинуті сегментні регістри (крім CS, всі розряди якого встановлюються в одиничний стан), покажчик команд IP, всі прапори, регістри черги команд і всі внутрішні тригери в пристрої керування. Сигнал RESET не впливає на стан загальних регістрів, які встановлюються в початковий стан програмним шляхом. На час дії сигналу RESET всі виходи, що мають три стани, переводяться в третій стан, а виходи, що мають два стани, стають пасивними. Мінімальна тривалість сигналу RESET при першому включенні МП становить 50 мкс, а при повторному запуску – чотири такти синхронізації. Після зняття сигналу RESET робота МП відновляється з початкового стану.

MN/MX – мінімальний/максимальний режими. Сигнал на цьому вході визначає режим роботи МП: 1 – мінімальний, 0 – максимальний, коли змінюються функції восьми керуючих сигналів.

У максимальному режимі діють наступні керуючі сигнали:

S2-S0 – сигнали стану, що забезпечують інформацію про тип виконуваного циклу шини (табл. 1.10). Сигнали стану подаються в контролер шини, що дешифрує їх і формує розширений набір керуючих сигналів. Якщо МП не ініціює цикл шини, то сигнали S2-S0 установлюються в пасивний стан 111. Відзначимо, що сигнал S2 логічно еквівалентний сигналу М/IO, a S1 – сигналу DT/R.

QS1 – QS0 – стан черги. Ідентифікує стан внутрішньої 6-байтовой черги команд МП (табл. 1.11) і діє протягом такту синхронізації після виконання операції над чергою. Сигнали QS1 – QS0 призначені для співпроцесора, що сприймає команди й операнди за допомогою команди ESC. Співпроцесор контролює шину AD і фіксує момент, коли із програмної пам'яті вибирається призначена для нього команда ESC, а потім стежить за чергою команд і визначає момент, коли ця команда повинна виконуватися.

RQ/GT1 – RQ/GT0 – запит/подання (підтвердження, дозвіл). Дві однакові двонаправлені лінії, кожна з яких може використовуватися для передачі імпульсних сигналів запиту/дозволу доступу до локальної шини (каналу). Процес доступу до шини здійснюється в наступному порядку:

1) пристрій, підключений до локальної шини і що потребує доступу до загальних ресурсів, формує запитальний (перший) імпульс тривалістю один такт;

2) наприкінці поточного циклу МП видає відповідний (другий) імпульс, що підтверджує можливість доступу до локальної шини. У наступному такті МП переводить шини адреси/даних і керування у високоомний стан і відключається від каналу;

|

Таблиця 1.7 | |||

|

S2 |

SI |

S0 |

Тип циклу шини |

|

0 |

0 |

0 |

Підтвердження переривання |

|

0 |

0 |

1 |

Читання ЗП |

|

0 |

1 |

0 |

Запис ЗП |

|

0 |

1 |

1 |

Зупинка |

|

1 |

0 |

0 |

Вибірка команди |

|

1 |

0 |

1 |

Читання ЗП |

|

1 |

1 |

0 |

Запис ЗП |

|

1 |

1 |

1 |

Циклу шини немає |

|

Таблиця 1.8 | ||

|

QS1 |

QS0 |

Операція над чергою |

|

0 |

0 |

Операції нема, в останньому такті не було вибірки із черги |

|

0 |

1 |

Із черги вибраний перший байт команд |

|

1 |

0 |

Черга порожня, була спустошена командою передачі керування |

|

1 |

1 |

Із черги обраний наступний байт команди |

3) по закінченні роботи з каналом пристрій видає на ту ж лінію імпульс (третій), що вказує на закінчення захоплення каналу. У наступному такті МП відновляє керування шиною й продовжує обчислення.

Всі три імпульси мають однакову тривалість і низький активний рівень. Сигнали на лініях незалежні, однак лінія RQ/GT0 має більше високий пріоритет, чим лінія RQ/GT1, коли запити надходять одночасно. Але якщо на лінії RQ/GT0 з'являється запит у той час, коли МП находиться в стані захоплення по сигналі RQ/GT1, то цей запит захоплення не одержує підтвердження до звільнення шини по лінії RQ/GT1. Таким чином, кожна із двох розглянутих ліній служить для встановлення режиму захоплення шин і щодо цього еквівалентна парі ліній HOLD і HLDA МП К1810ВМ86 у мінімальному режимі.

LOCK – блокування шини, інформує пристрою системи, що вони не повинні намагатися запитувати шину. Формується однобайтовим префіксом LOCK, розташовуваним перед командою, і діє до кінця виконання цієї команди, забороняючи доступ до системної магістралі іншим пристроям, зокрема іншим процесорам. При підтвердженні запиту шини вихідний буфер сигналу LOCK переводиться в третій стан.

Префікс LOCK не впливає на переривання. Якщо при наявності блокування зовнішня система запитує шину по лініях RQ/GT, МП фіксує запит, але не підтверджує його до завершення команди, що має префікс блокування. Програмісти звичайно використовують цей префікс, коли необхідно ідентифікувати стан розподілених ресурсів системи. Префікс LOCK може використовуватися й у мінімальному режимі, коли зовнішній сигнал блокування LOCK відсутній. У цьому випадку генерування підтвердження HLDA на запит шини HOLD затримується до завершення виконуваної команди.