- •Аппаратный и программный подходы к синтезу цифровых устройств

- •201000, 201200, 071700 И направления 550400

- •Введение

- •Рекомендуемая литература

- •1. Аппаратный синтез

- •1.1. Постановка задачи

- •1.2. Решение поставленной задачи

- •1.2.1. Синтез счетчика по модулю n

- •1.2.2. Синтез преобразователя кода

- •1.2.3. Расчет быстродействия и потребляемой мощности

- •2. Программный синтез

- •2.1. Постановка задачи

- •2.2. Решение поставленной задачи

- •2.2.1. Требования к построению блок-схемы алгоритма

- •2.2.2. Требования к написанию программы

- •2.2.3. Пример программного синтеза

- •3. Оформление курсовой работы

- •4. Основные вопросы по защите курсовой работы

- •Приложение 1. Стандарт на размеры структурных блоков

- •Приложение 2. Стандарт на алгоритмические блоки

- •Приложение 3. Основные сведения о процессоре tms320c6x п3.1. Структура

- •П3.2. Система команд для чисел с фиксированной запятой

2.2. Решение поставленной задачи

В данной работе достаточно ограничиться следующими этапами программного синтеза:

1) сформулировать идею решения задачи;

2) разработать детальный алгоритм, отражающую идею решения задачи;

3) описать детальный алгоритм на языке ассемблера TMS320C6x.

2.2.1. Требования к построению блок-схемы алгоритма

Обычно алгоритм представляется блок-схемой, вычерченной в соответствии с требованиями ЕСКД (приложение 2). В каждом блоке в словесной или символической форме описывается операция, выполняемая на данном шаге решения задачи. Алгоритмические блоки, за исключением блоков «начало» и «конец», нумеруются в порядке их следования сверху вниз и слева направо.

Блок-схема алгоритма сопровождается описанием, где отражается содержание и целесообразность использования каждого ее блока.

2.2.2. Требования к написанию программы

Программа представляет собой последовательное описание алгоритмических блоков на выбранном языке программирования.

При написании программы на языке ассемблера необходимо учитывать архитектурные особенности данного процессора. Применительно к TMS320C6x основными из этих особенностей являются:

циклические вычисления реализуются только с помощью команды перехода;

ветвления реализуются с помощью поля условия ассемблерной строки, используемого для каждой команды данной ветви алгоритмического блока «решение»;

условной может быть любая команда;

параллельное выполнение до 8 команд.

Структурно ассемблерная программа состоит из последовательности строк, в каждой из которых размещается только одна команда. Командные строки заполняются в соответствии со структурой ассемблерной строки и не нумеруются. Каждая командная строка сопровождается комментарием, отражающим суть выполняемой операции.

2.2.3. Пример программного синтеза

Задача: в блоке из восьми двухразрядных двоичных слов определить количество единичных бит. Блок в виде полуслова размещен в ячейке 10h процессорной памяти данных. Результат поместить в ячейку 11h процессорной памяти данных.

Для любой задачи существует множество методов решения. В данном случае выберем следующий метод. Над значением каждого разряда блока выполняется операция конъюнкции с единицей. В случае единичного результата содержимое соответствующего счетчика увеличивается на 1. Если же результат конъюнкции равен нулю, содержимое этого счетчика не изменяется. Описанная процедура завершается по окончании блока.

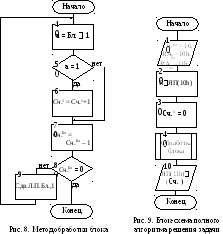

Выбранный метод решения иллюстрируется алгоритмической блок-схемой, представленной на рис. 8. Сначала операция конъюнкции с 1 производится над старшим разрядом блока (Бл.) двоичных слов (блок 4). Если результат этой операции равен 1 (блок 5), содержимое счетчика единиц (Сч.1) увеличивается относительно начального (нулевого) состояния на 1 (блок 6). В противном случае сразу уменьшается на 1 (блок 7) содержимое счетчика длины блока (Сч.Бл), обозначая тем самым, что очередной (первоначально первый справа) бит блока (Бл.) проанализирован. После этого блок двоичных слов логически сдвигается вправо на один разряд (блок 9) и весь процесс обработки блока повторяется, но уже для следующего его разряда. По окончании блока двоичных слов, что индицируется нулевым содержимым Сч.Бл (блок 8), процесс обработки завершается.

На основе рис. 8 нетрудно выработать полный алгоритм решения задачи (рис. 9). Так, для обработки блока двоичных слов его необходимо передать из ячейки памяти 10h в один из регистров (R) общего назначения (блок 2). С этой целью, поскольку TMS320C6x не поддерживает непосредственную адресацию, число 10h следует предварительно ввести в другой регистр общего назначения (блок 1), который назовем регистром адреса блока (RAБл). По этой же причине следует предварительно ввести и адрес ячейки памяти, предназначенной для хранения результата (блок 1). Соответствующий регистр общего назначения назовем регистром адреса результата (RAres). Также очевидно, что перед началом обработки блока двоичных слов все счетчики необходимо установить в соответствующие начальные состояния (блоки 1 и 3).

Т еперь

в соответствии с алгоритмом следует

распределить регистры общего назначения

по функциональному назначению. При этом

необходимо помнить, что регистрами

условия могут быть только регистры А1,

А2, В0, В1 и В2. Выбрав для реализации задачи

сторону А процессора, сделаем следующие

назначения: А0 –RAБл;

А1 – Сч.Бл;

А2 – приемник результата операции

конъюнкции; А3 – RAres;

А4 – приемник обрабатываемого блока

двоичных слов (R);

А5 – счетчик единичных бит блока. Для

вспомогательных операций регистры

будем назначать по мере их выполнения.

еперь

в соответствии с алгоритмом следует

распределить регистры общего назначения

по функциональному назначению. При этом

необходимо помнить, что регистрами

условия могут быть только регистры А1,

А2, В0, В1 и В2. Выбрав для реализации задачи

сторону А процессора, сделаем следующие

назначения: А0 –RAБл;

А1 – Сч.Бл;

А2 – приемник результата операции

конъюнкции; А3 – RAres;

А4 – приемник обрабатываемого блока

двоичных слов (R);

А5 – счетчик единичных бит блока. Для

вспомогательных операций регистры

будем назначать по мере их выполнения.

Наконец, опишем разработанный алгоритм на языке ассемблера TMS320C6x. При этом для удобства чтения программы следует придерживаться структуры ассемблерной строки. Однако поле модуля использовать не будем, предоставляя сделать это диспетчеру процессора. Аналогично поступим и с полем параллельных линий. С учетом сделанных замечаний требуемая программа будет иметь вид:

MVK 16,A1 ; ввод длины блока

MVK 10h,A0 ; ввод адреса ячейки памяти, содержащей

; блок

MVK 11h,A3 ; ввод адреса ячейки памяти результата

LDW *A0,A4 ; загрузка исходного блока

ZERO A5 ; обнуление счетчика единиц

NOP 3 ; задержка, необходимая для завершения

; загрузки А4

L1: AND 1,A4,A2 ; конъюнкция блока с 1

[A2] ADDK 1,A5 ; декремент счетчика единиц

SUBU A1,1,A1 ; инкремент счетчика длины блока

[A1] B L1 ; переход по метке

[A1] SHRU A4,1,A6 ; логический сдвиг вправо на 1 разряд

[A1] MV A6,A4 ; пересылка укороченного блока назад

[A1] NOP 3 ; компенсация оставшихся трех слот задержки

STB A5,*A3 ; сохранение результата решения задачи

При написании программы следует учитывать слоты задержки команд (понятие слота задержки см. в приложении 3).

Как видно, выполнение данной программы требует 1+1+1+1+4+1+(1+1+1+1+5)16+1+4 = 158 тактов.