- •Аппаратный и программный подходы к синтезу цифровых устройств

- •201000, 201200, 071700 И направления 550400

- •Введение

- •Рекомендуемая литература

- •1. Аппаратный синтез

- •1.1. Постановка задачи

- •1.2. Решение поставленной задачи

- •1.2.1. Синтез счетчика по модулю n

- •1.2.2. Синтез преобразователя кода

- •1.2.3. Расчет быстродействия и потребляемой мощности

- •2. Программный синтез

- •2.1. Постановка задачи

- •2.2. Решение поставленной задачи

- •2.2.1. Требования к построению блок-схемы алгоритма

- •2.2.2. Требования к написанию программы

- •2.2.3. Пример программного синтеза

- •3. Оформление курсовой работы

- •4. Основные вопросы по защите курсовой работы

- •Приложение 1. Стандарт на размеры структурных блоков

- •Приложение 2. Стандарт на алгоритмические блоки

- •Приложение 3. Основные сведения о процессоре tms320c6x п3.1. Структура

- •П3.2. Система команд для чисел с фиксированной запятой

1.2.2. Синтез преобразователя кода

Преобразователь кода является комбинационным цифровым устройством. Поэтому для его синтеза следует воспользоваться соответствующей стандартной методикой:

1. Задать закон функционирования в виде расширенной таблицы истинности, отражающей связь i-го состояния счетчика Qi, начиная с начального Qн, с соответствующим двоичным словом на выходе преобразователя кода и учитывающей безразличные входные двоичные наборы.

Например, для суммирующего счетчика по модулю 5 (рис.5) и структуры блока 1110000110b (902) расширенная таблица истинности преобразователя кода будет иметь вид табл. 4.

Таблица 4. Таблица истинности преобразователя кода

|

Порядковый номер состояния |

Состояние счетчика, BIN |

Выходы преобразователя кода, BIN | |||

|

q2 |

q1 |

q0 |

у1 |

у0 | |

|

0 |

0 |

0 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

2 |

0 |

1 |

0 |

0 |

0 |

|

3 |

0 |

1 |

1 |

0 |

1 |

|

4 |

1 |

0 |

0 |

1 |

0 |

|

5 |

1 |

0 |

1 |

|

|

|

6 |

1 |

1 |

0 |

|

|

|

7 |

1 |

1 |

1 |

|

|

2. Получить систему минимальных ФАЛ, одну из которых вывести с помощью графического метода (карты Карно), а другую – с помощью алгебраического метода Квайна. При этом следует учитывать, что данный преобразователь кода является частично определенным КЦУ.

Например, для табл. 4 получим минимальную ФАЛ у1min методом карт Карно, а у0min – методом Квайна.

Метод карт Карно:

у1min

=

![]()

Метод Квайна:

1

2 3 1, 2, 3

у0

=

![]() =

=![]()

у0min

=

![]() .

.

3. Записать минимальные ФАЛ в заданном минимальном базисе.

С этой целью к исходной ФАЛ последовательно применяют законы двойной инверсии и двойственности алгебры логики.

В примере минимальные ФАЛ в базисе И-НЕ будут иметь вид:

у1min

=

![]() ,

у0min

=

,

у0min

=

![]() .

.

4. В соответствии с требованиями ЕСКД (приложение 1) и с учетом приоритетности логических операций (старшей является инверсия, затем операции типа конъюнкции и, наконец, операции типа дизъюнкции) вычертить соответствующую структурную схему, сопровождаемую спецификацией.

При распределении логических элементов схемы по корпусам МС используются свободные компоненты уже определенных МС и даже схемы предыдущего узла устройства.

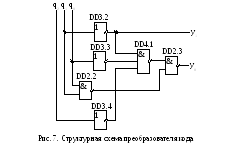

Структурная схема для рассматриваемого примера приведена на рис. 7.

1.2.3. Расчет быстродействия и потребляемой мощности

Быстродействие цифрового устройства определяется максимальным среднем временем задержки распространения сигнала tз,max от одного из входов до одного из выходов. С целью его оценки выделяются вход и выход устройства, связанные наибольшим числом Мmax логических элементов или устройств. Суммарное время их задержки и дает быстродействие всего устройства:

Полная спецификация: №

МС Тип

МС

Мощность

потребления, мВт

Среднее время

задержки, нс 1 К155ИЕ5

265

135 2 К155ЛА3

135

18,5 3 К155ЛН2

165

35 4 К155ЛА4

135

18,5

![]() ,

(2)

,

(2)

где tз,i – среднее время задержки распространения сигнала i-го из Mmax логических элементов.

Следует отметить,

что для логических элементов время

задержки tз

определяется средним временем задержки

включения

![]() и выключения

и выключения![]() :

:

tз

= (

tз

= (![]() +

+![]() )/2.

(3)

)/2.

(3)

В данной работе

tз,max

определяется суммой времени задержки

счетчика по модулю N

![]() и

преобразователя кода

и

преобразователя кода![]() .

Ввиду отсутствия в преобразователе

кода обратных связей оценка

.

Ввиду отсутствия в преобразователе

кода обратных связей оценка![]() проводится в соответствии с (2). Значение

же

проводится в соответствии с (2). Значение

же![]() должно определяться с момента прихода

активного сигнала на счетный вход

счетчика и вплоть до момента снятия

активного сигнала с его входа принудительной

установки.

должно определяться с момента прихода

активного сигнала на счетный вход

счетчика и вплоть до момента снятия

активного сигнала с его входа принудительной

установки.

Мощность Р, потребляемая устройством, складывается из мощностей, потребляемых каждой его микросхемой:

![]() ,

(4)

,

(4)

где L – количество микросхем в устройстве.

В примере:

![]() =

=

![]() +

+![]() +

+![]() +

+![]() =

135+(18,5 + 35)+20+(18,5+35) = 262 нс,

=

135+(18,5 + 35)+20+(18,5+35) = 262 нс,

![]() =

=

![]() +

+![]() +

+![]() =

35+18,5+18,5 = 72 нс,

=

35+18,5+18,5 = 72 нс,

![]() =

=

![]() +

+![]() =

262+72 = 334 нс.

=

262+72 = 334 нс.

Р = Р1+Р2+Р3+Р4 = 265+135+165+135 = 700 мВт.