- •САПР Xilinx Foundation Series

- •ВХОД В СИСТЕМУ

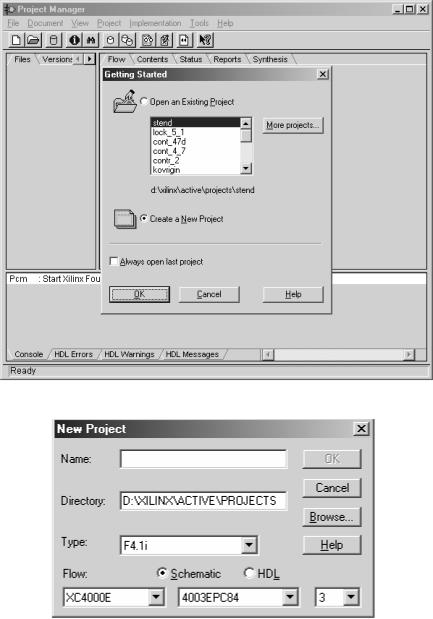

- •Открытие нового проекта

- •ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ

- •Как задать размер листа и присвоить ему имя

- •ОСНОВНЫЕ ОПЕРАЦИИ

- •Выбор элемента

- •Перемещение элемента или фрагмента схемы

- •Удаление элемента

- •Присвоение имени элементу

- •Рисование цепи

- •Перемещение цепи

- •Удаление цепи

- •Присвоение имени цепи

- •Переименование цепи

- •Удаление имени цепи

- •Задание констант 0 и 1

- •ШИННЫЕ СОЕДИНЕНИЯ

- •Пример простого шинного соединения

- •Шинные контакты элемента

- •Правила соединений

- •Простые и сложные шины

- •Примеры шинных соединений

- •Редактирование изображения шины

- •Контроль соединений

- •Сохранение схемы

- •ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ ЭЛЕМЕНТОВ

- •СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ БАЗОВЫХ ЭЛЕМЕНТОВ

- •Создание макроэлемента

- •Выбор макроэлемента из библиотеки

- •Редактирование УГО макроэлемента

- •ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL

- •Ввод описания макроэлемента

- •Ввод описания архитектуры объекта с использованием Language Assistant

- •Сохранение документа

- •Проверка синтаксиса

- •Редактирование текста описания

- •Синтез макроэлемента

- •Создание VHDL-макроса

- •Выбор макроса из библиотеки

- •Редактирование УГО макроэлемента

- •Коррекция VHDL-описания макроэлемента

- •Автоматическое создание модели памяти

- •Редактирование начального состояния памяти

- •ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Окно моделирования схемы

- •Выбор контрольных точек схемы

- •Удаление контрольных точек из окна моделирования

- •Изменение порядка имен в окне моделирования

- •Задание входных воздействий

- •Задание синхросигналов

- •Как отсоединить генератор от внешнего входа схемы

- •Задание входных воздействий в окне моделирования

- •Выполнение моделирования схемы

- •Сохранение результатов моделирования

- •Моделирование макроэлемента

- •РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС

- •ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА ПЛИС

- •Универсальный лабораторный стенд

- •Макроэлементы органов управления стенда

- •Подключение макроэлементов стенда к проекту

- •РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ

- •ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ

- •Измерение задержек на временной диаграмме

- •ЗАГРУЗКА ПРОЕКТА В ПЛИС

- •ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ

- •ВВЕДЕНИЕ В ЯЗЫК VHDL

- •ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL

- •Структура описания объекта проекта

- •Интерфейс объекта проекта

- •Синтаксис

- •Тип сигнала

- •О правилах записи программы

- •Описание архитектуры объекта

- •Синтаксис

- •Параллельные операторы

- •Стили описаний архитектур

- •Элементы потокового проектирования

- •Элементы поведенческого проектирования

- •VHDL-стандарты IEEE

- •Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned

- •Библиотеки и пакеты

- •Логические элементы

- •Триггеры

- •Мультиплексоры

- •Дешифратор

- •Сумматоры

- •Счетчики

- •Регистры

- •Исходные данные

- •Составление программной модели АЛУ

- •СПИСОК ЛИТЕРАТУРЫ

Б.Н. Ковригин

Введение в инструментальные средства проектирования и отладки цифровых устройств на ПЛИС

Москва 2006

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ РФ

МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ (ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ)

Б.Н. Ковригин

ВВЕДЕНИЕ В ИНСТРУМЕНТАЛЬНЫЕ СРЕДСТВА ПРОЕКТИРОВАНИЯ И ОТЛАДКИ ЦИФРОВЫХ УСТРОЙСТВ НА ПЛИС

Учебно-методическое пособие

Москва 2006

УДК 004.896(075) ББК 30.2-5-05я7 К 56

Ковригин Б.Н. Введение в инструментальные средства проектирования и отладки цифровых устройств на ПЛИС: Учебно-методическое пособие. М.:

МИФИ, 2006. — 192 с.

Цель пособия — обеспечение лабораторного практикума и курсового проектирования по курсам «Схемотехника ЭВМ», «Организация систем» и «Функцио- нально-логическое моделирование цифровых устройств».

Изложены инструментальные средства (САПР), используемые при проектировании цифровых устройств на ПЛИС фирмы Xilinx со структурой FPGA. Приведено описание языка VHDL, достаточное для выполнения заданий. Дан пример проектирования устройства на VHDL.

Предназначено для студентов дневного, вечернего и заочного обучения специальности «Вычислительные машины, комплексы и сети» и смежных специальностей, изучающих компьютерную технику.

Рецензент А.Л. Зорин

Рекомендовано к изданию редсоветом МИФИ

ISBN 5-7262-6671-1 |

© |

Московский инженерно-физический институт |

|

|

(государственный университет), 2006 |

|

© |

Б.Н. Ковригин, 2006 |

С О Д Е Р Ж А Н И Е

САПР Xilinx Foundation Series.................................................................................... |

6 |

ВХОД В СИСТЕМУ..................................................................................................... |

6 |

Открытие нового проекта.................................................................................. |

6 |

ВВОД И РЕДАКТИРОВАНИЕ СХЕМЫ.................................................................. |

9 |

Как задать размер листа и присвоить ему имя .............................................. |

12 |

ОСНОВНЫЕ ОПЕРАЦИИ.................................................................................... |

14 |

Выбор элемента................................................................................................ |

14 |

Перемещение элемента или фрагмента схемы.............................................. |

16 |

Удаление элемента........................................................................................... |

17 |

Присвоение имени элементу........................................................................... |

17 |

Рисование цепи................................................................................................. |

18 |

Перемещение цепи........................................................................................... |

18 |

Удаление цепи.................................................................................................. |

18 |

Присвоение имени цепи .................................................................................. |

19 |

Переименование цепи...................................................................................... |

19 |

Удаление имени цепи ...................................................................................... |

19 |

Задание констант 0 и 1..................................................................................... |

20 |

ШИННЫЕ СОЕДИНЕНИЯ................................................................................... |

20 |

Пример простого шинного соединения.......................................................... |

21 |

Шинные контакты элемента............................................................................ |

25 |

Правила соединений........................................................................................ |

26 |

Простые и сложные шины............................................................................... |

27 |

Примеры шинных соединений........................................................................ |

27 |

Редактирование изображения шины .............................................................. |

32 |

Контроль соединений ...................................................................................... |

32 |

Сохранение схемы............................................................................................ |

34 |

ФОРМИРОВАНИЕ СОБСТВЕННОЙ БИБЛИОТЕКИ МОДЕЛЕЙ |

|

ЭЛЕМЕНТОВ.............................................................................................................. |

34 |

СОЗДАНИЕ МАКРОЭЛЕМЕНТА НА ОСНОВЕ |

|

БАЗОВЫХ ЭЛЕМЕНТОВ..................................................................................... |

35 |

Создание макроэлемента................................................................................. |

35 |

Выбор макроэлемента из библиотеки ............................................................ |

37 |

Редактирование УГО макроэлемента............................................................. |

38 |

Просмотр и редактирование внутренней структуры макроэлемента.......... |

41 |

ВВОД И ОТЛАДКА МАКРОЭЛЕМЕНТА НА VHDL........................................ |

41 |

Ввод описания макроэлемента........................................................................ |

41 |

Ввод описания архитектуры объекта с использованием |

|

Language Assistant ............................................................................................ |

47 |

Сохранение документа .................................................................................... |

49 |

3 |

|

Проверка синтаксиса........................................................................................ |

50 |

Редактирование текста описания.................................................................... |

50 |

Синтез макроэлемента..................................................................................... |

53 |

Создание VHDL-макроса................................................................................. |

53 |

Выбор макроса из библиотеки........................................................................ |

54 |

Редактирование УГО макроэлемента............................................................. |

54 |

Коррекция VHDL-описания макроэлемента.................................................. |

55 |

ГРАФИЧЕСКИЙ ДИАЛОГОВЫЙ ИНСТРУМЕНТ СОЗДАНИЯ |

|

ЭЛЕМЕНТА LOGIBLOX....................................................................................... |

56 |

Автоматическое создание модели памяти..................................................... |

56 |

Редактирование начального состояния памяти............................................. |

64 |

ФУНКЦИОНАЛЬНОЕ МОДЕЛИРОВАНИЕ СХЕМЫ...................................... |

67 |

Окно моделирования схемы............................................................................ |

67 |

Выбор контрольных точек схемы................................................................... |

69 |

Удаление контрольных точек из окна моделирования................................. |

70 |

Изменение порядка имен в окне моделирования.......................................... |

71 |

Задание входных воздействий ........................................................................ |

71 |

Задание синхросигналов............................................................................ |

72 |

Как отсоединить генератор от внешнего входа схемы........................... |

74 |

Задание входных воздействий в окне моделирования............................ |

74 |

Выполнение моделирования схемы................................................................ |

76 |

Сохранение результатов моделирования....................................................... |

77 |

Моделирование макроэлемента...................................................................... |

78 |

РЕАЛИЗАЦИЯ ПРОЕКТА НА ПЛИС.................................................................... |

78 |

ПОДГОТОВКА СХЕМЫ ДЛЯ РАЗМЕЩЕНИЯ ЕЁ НА КРИСТАЛЛЕ ........... |

80 |

Универсальный лабораторный стенд............................................................. |

80 |

Макроэлементы органов управления стенда................................................. |

82 |

Подключение макроэлементов стенда к проекту.......................................... |

85 |

РАЗМЕЩЕНИЕ СХЕМЫ НА КРИСТАЛЛЕ....................................................... |

86 |

ВРЕМЕННОЕ МОДЕЛИРОВАНИЕ СХЕМЫ..................................................... |

88 |

Измерение задержек на временной диаграмме.............................................. |

89 |

ЗАГРУЗКА ПРОЕКТА В ПЛИС........................................................................... |

90 |

ПРОСМОТР РЕЗУЛЬТАТОВ РАЗМЕЩЕНИЯ СХЕМЫ................................... |

94 |

ВВЕДЕНИЕ В ЯЗЫК VHDL ................................................................................... |

100 |

ВЫБРАННЫЕ МЕСТА ИЗ ОПИСАНИЯ ЯЗЫКА VHDL ................................ |

102 |

Структура описания объекта проекта........................................................... |

102 |

Интерфейс объекта проекта.......................................................................... |

103 |

Синтаксис................................................................................................. |

103 |

Тип сигнала .............................................................................................. |

105 |

О правилах записи программы............................................................... |

106 |

О чём можно не беспокоиться................................................................ |

107 |

Описание архитектуры объекта.................................................................... |

107 |

Синтаксис................................................................................................. |

107 |

4

Параллельные операторы........................................................................ |

109 |

Стили описания архитектур.................................................................... |

110 |

Элементы потокового проектирования.................................................. |

112 |

Элементы поведенческого проектирования.......................................... |

119 |

VHDL-стандарты IEEE .................................................................................. |

129 |

Пакеты std_logic_arith, std_logic_signed u std_logic_unsigned..................... |

131 |

Библиотеки и пакеты ..................................................................................... |

134 |

Приложение 1. БИБЛИОТЕЧНЫЕ ЭЛЕМЕНТЫ |

|

СХЕМНОГО РЕДАКТОРА..................................................................................... |

136 |

Логические элементы..................................................................................... |

136 |

Триггеры......................................................................................................... |

142 |

Мультиплексоры............................................................................................ |

154 |

Дешифратор.................................................................................................... |

157 |

Сумматоры...................................................................................................... |

159 |

Счетчики......................................................................................................... |

160 |

Регистры.......................................................................................................... |

166 |

Приложение 2. ПРИМЕР ПРОЕКТИРОВАНИЕ |

|

АРИФМЕТИКО-ЛОГИЧЕКОГО УСТРОЙСТВА НА VHDL.......................... |

172 |

Исходные данные........................................................................................... |

172 |

Составление программной модели АЛУ...................................................... |

177 |

СПИСОК ЛИТЕРАТУРЫ....................................................................................... |

191 |

5

САПР Xilinx Foundation Series

Система сквозного проектирования цифровых устройств на базе ПЛИС Xilinx Foundation Series включает в себя средства схемотехнического ввода, языки описания аппаратуры (HDL) — VHDL, Verilog и Abel, средства моделирования, синтеза структуры кристалла и программирования.

ВХОД В СИСТЕМУ

Для входа в систему необходимо на рабочем столе Windows дважды щелкнуть мышью пик-

тограмму Project Manager.

Project Manager — графическое средство управления файлами проекта и основными модулями системы автоматизированного проектирования ПЛИС.

Откроется окно Getting Started на фоне главного окна систе-

мы — Project Manager (рис. 1).

Работа в системе начинается либо с открытия нового проекта, либо с выбора уже существующего проекта для продолжения выполнения проектных операций и процедур.

Открытие нового проекта

1. В окне Getting Started активизируйте опцию Greate a New Project и нажмите кнопку OK (см. рис. 1). Откроется диалоговое окно New Project (рис. 2).

6

Рис. 1. Окно Getting Started

Рис. 2. Окно открытия нового проекта

7

2.В открывшемся окне в поле Name введите имя проекта. Имя должно содержать не более 8 символов.

3.В поле Directory выберите место расположения проекта:

U:\<номер группы>\<фамилия>.

Например, U:\K5_121\SIDOROV.

4.Не изменяйте предложенное значение в поле Type (см.

рис. 2).

5.Выберите в окнах Flow:

серию ПЛИС — Spartan, марку ПЛИС — S10PC84,

и указатель быстродействия — 3.

Заполненное окно New Project приведено на рис. 3.

Рис. 3. Заполненное окно New Project

6. Нажмите кнопку OK.

Имя проекта и марка выбранной ПЛИС с заданным значением быстродействия появятся в поле заголовка главного окна системы

(рис. 4).

8