- •Предмет "Схемотехника" эвм. Используемые системы счисления и кодирования информации, обоснование выбора.

- •Способы представления информации в цифровых устройствах. Параметры электрических сигналов. Модель логического элемента. Технические характеристики. Уго по гост и iso.

- •Функции Алгебры Логики (фал). Способы задания функций. Понятие Базиса. Сднф, скнф. Переход из одного базиса в другой.

- •Задача минимизации фал. Правило склеивания. Основные тождества алгебры логики.

- •Минимизация фал методом Квайна Мак-Класки.

- •Графические методы минимизации фал.

- •Не полностью определенные функции. Минимизация не полностью определенных функций.

- •Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

- •Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

- •Комбинационные схемы. Мультиплексор. Увеличение разрядности мультиплексора. Реализация фал на мультиплексоре. Демультиплексор.

- •Сумматоры. Одноразрядный комбинационный полусумматор. Варианты реализации и их сравнение.

- •Сумматоры. Одноразрядный полный комбинационный сумматор. Построение полного сумматора из полусумматоров.

- •Сумматоры. Одноразрядный последовательностный сумматор.

- •Сумматоры

- •Многоразрядные сумматоры. Накапливающий сумматор.

- •Многоразрядные сумматоры. Комбинационный сумматор.

- •Многоразрядные сумматоры. Организация ускоренного переноса.

- •Схемы с памятью. Понятие дискретного Времени. Тактовый генератор.

- •Элементарная запоминающая ячейка. Два варианта реализации.

- •Триггер. Обобщенная схема произвольного триггера. Формальное описание.

- •Классификация триггеров. Понятие и способы синхронизации

- •Асинхронные и синхронные триггерные схемы. Двухступенчатые триггеры типа ms.

- •Триггер с динамическим управлением записью. Временная диаграмма.

- •Rs-триггер: функции, таблица и матрица переходов.

- •T-триггер: функции, таблица и матрица переходов. Способы снятия ограничения на длительность сигнала.

- •D-триггер: функции, таблица переходов.

- •Dv-триггер: функции, таблица и матрица переходов.

- •Jk-триггер: функции, таблица и матрица переходов.

- •Построение триггера с заданной таблицей состояний на базе rs (или dv, jk).

- •Регистры. Классификация. Уго регистров.

- •Регистры хранения и регистры сдвига. Реверсивный регистр.

- •Обобщенная схема регистра сдвига. Построение заданного регистра на базе триггеров rs (или dv, jk).

- •Счетчики. Классификация счетчиков. Понятие модуля пересчета и других характеристики.

- •Суммирующие и вычитающие счетчики. Временные параметры.

- •Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Проектирование синхронного счетчика с заданным набором состояний на rs (или dv, jk) триггерах.

- •Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в счетчиках.

- •Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи/чтения. Мультиплексирование.

- •Запоминающая ячейка статического типа, устройство и принцип работы.

- •Запоминающая ячейка динамического типа, устройство и принцип работы.

- •Реализация фал на микросхеме памяти. Программируемая логика.

- •Программируемые логические интегральные схемы. Основные принципы построения плм.

- •Обобщенная структура плис fpga. Основные элементы, их назначение и принцип работы.

- •Плис fpga. Назначение и устройство clb.

- •Реализация логических функций в плис foga, lut - назначение и устройство.

- •Блоки ввода вывода Плис-iob, Теневая память. Программируемые соединения, psm.

- •Технология проектирования цифровых устройств на плис fpga. Основные этапы. На примере Xilinx Spartan.

- •Ассоциативная память. Организация, способ выборки, отличия от адресного зу.

- •Принцип кэширования при обращении к памяти. Организация, взаимодействия между процессором и озу.

Минимизация фал методом Квайна Мак-Класки.

Минимизация ФАЛ методом Квайна Мак-Класки. ax v a(not)x= a

Исходная ф-ия должна быть представлена в виде СДНФ. Если переменная входит в прямом виде, то отображается единица, если в инверсном – ноль.

Получившиеся эквиваленты группируются по кол-ву единиц в терме.

Производится попарное сравнение термов в соседних группах на предмет возможности их склеивания. В результате чего формируются термы меньшего ранга. Место выпавшей при склеивании переменной обозначается знаком «-». Получившиеся термы меньшего ранга так же группируются по кол-ву единиц. Процесс продолжается до тех пор, пока склеивание возможно. Получившиеся в результате этого процесса термы носят название «тупиковых форм».

Строится таблица (импликантная матрица) у которой в качестве заголовка столбцов выступают термы исходной функции, а в качестве заголовка строк полученные на предыдущем этапе тупиковые формы.

Проставляются метки на перекрестке, обозначающие вхождение тупиковой формы в исходный терм.

Выбирается такая минимальная совокупность тупиковых форм, которая своими метками покроет все термы исходной функции.

Производится обратная замена двоичных эквивалентов буквенными переменными и записывается минимальная дизъюнктивная форма исходной функции.

Графические методы минимизации фал.

Метод диаграмм Вейча

Занести зн-я в табл (скнф -зн-я ф-ии =0, сднф=1)

Выполнить объединения в м-кубы

Записать сднф или скнф

для

3 переменных

для

3 переменных

для

4 переменных

для

4 переменных

Карты Карно отличаются от карт Вейча только расположением аргументов.

Не полностью определенные функции. Минимизация не полностью определенных функций.

Полностью определенная функция – у нее известны все значения. Не полностью определенная функция – на части наборов она не определена. Неиспользуемые значения называются запрещенными.

Для минимизации вводится дополнительная эквивалентная функция и искусственно доопределяется (если СДНФ: склеить как можно больше термов, доопределяем единицами; если СКНФ: доопределяем нулями).

Далее минимизируем любым способом и делаем проверку импликантной матрицы, где заголовки столбцов являются исходными значениями, а заголовки строк – то, что получилось после доопределения, с целью удаления лишних импликант.

Постановка задачи, этапы анализа и синтеза комбинационных схем на аппарате фал.

Постановка задачи - определение проектируемого устройства, кол-во входных сигналов, кол-во выходных и значения которые они принимают (табл истинности).

Основные этапы синтеза и анализа:

создание математического описания (системы логических уравнений)

анализ логических уравнения и получение минимальной формы для каждой из них в заданном базисе

построение логической схемы с применением логических эл-ов выбранного базиса

цифровое моделирование и испытание схемы

физическое воплощение схемы

Комбинационные схемы. Дешифратор. Увеличение разрядности дешифратора. Реализация фал на дешифраторе.

Комбинационные схемы — такие схемы, в которых значения сигналов на выходе определяется только входными переменными. Схемы такого рода, обычно, не имеют обратных связей. Памяти в таких схемах нет.

Дешифратор (decoder) - устр-во, относящиеся к классу КС, преобразующее позиционный двоичный код в унитарный.

Позиционная система счисления — система счисления, в которой значение каждого числового знака (цифры) в записи числа зависит от его позиции (разряда).

Унитарный код – с одной единицей. Позиция и номер разряда – это и есть число.

Основное применение дешифратора в схемотехнике - там, где требуется функция выбора одного из нескольких устройств.

Если кол-во выходов DC меньше, чем 2n, где n кол-во входов, то его называют неполный. Полный дешифратор - где число входов =n, а число выходов =2n.

Таблица истинности - это такая таблица, в которой показываются все выходные состояния элемента для любых комбинаций входных сигналов.

Таблица истинности дешифратора:

|

b |

a |

f0 |

f1 |

f2 |

f3 |

F* |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

1 |

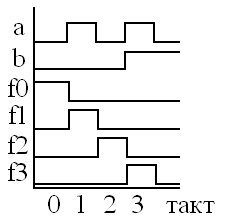

Распределитель импульсов (позволяет выбрать время):

Дешифратор и ИЛИ составляют базис, который позволяет реализовать любую логическую ф-ю с кол-ом аргументов, равным кол-ву входов дешифратора.

Представление логической функции с помощью дешифратора:

![]()

Синтез дешифратора с одним входом (основан на базисе И-ИЛИ-НЕ)

Для дешифратора широко используется функция разрешения E или CE (enable, chip enable). Разрешающий сигнал "1" разрешает работу дешифратора, "0" - запрещает (на всех выходах будет 0).

Применение:

Дешифратор с разрешающим входом может использоваться в качестве маршрутизатора по несуществующему каналу в зависимости от входа. E – вход маршрутизируемой информации. Адрес передачи определяется входами дешифратора (адресные входы).

Разрешение работы.

.

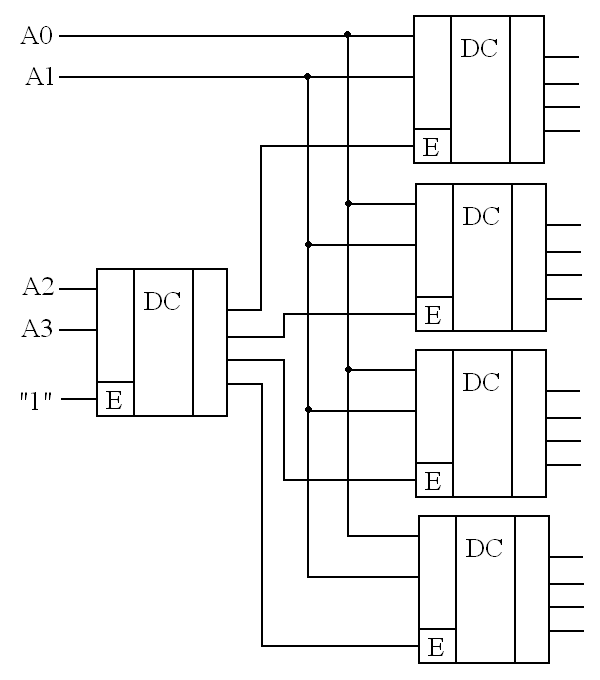

Увеличение разрядности дешифратора.

Один из наиболее распространенных способов – каскадирование (благодаря использованию разрешающего входа). Вход E - основной инструмент для увеличения разрядности.

Преимущества: понятно. Недостатки: громоздко.

Матричная структура увеличения разрядности дешифратора (не рисовали)

Каскадно-матричная – наиболее оптимальная.

Логическая схема дешифратора "4 в 16" с каскадно-матричной конструкцией: