19.Пути повышения емкости памяти(ответ не точный!!!)

Способы увеличения емкости (информационного объема) ЗУ

•Увеличение разрядности данных

•Увеличение разрядности шины адреса

•Комбинированный.

Увеличение разрядности достигается за счет параллельного соединения N микросхем ЗУ (в данном случае 8). На все микросхемы ЗУ подается одинаковый адрес, входы CS и WR/RD соединяются между собой. Емкость 1 ИМС M1 = 210·1 = 1024 бит. Емкость всей структуры: M = 210·1·8 = 8192 бит = 1 Кбайт Разрядность шины адреса увеличивается за счет использования дешифратора DC, на входы которого подаются старшие разряды ША. Входы CS ИМС ЗУ подключаются к соответствующим выходам DC. Вход Е дешифратора используется как вход разрешения работы всей схемы и идентифицируется внешними устройствами как вход выбора кристалла CS. Входы WR/RD соединяются между собой.

20.Построение основной памяти блочным методом.

|

Блочная организация основной памяти Емкость основной.памяти современных ВМ слишком велика, чтобы ее можно бьшореализовать на базе единственной интегральной микросхемы (ИМС). Необходимость объединения нескольких ИМС ЗУ возникает также, когда разрядность ячеекв микросхеме ЗУ меньше разрядности слов ВМ. Увеличение разрядности ЗУ реализуется за счет объединения.адресных входов объединяемых ИМС ЗУ. Информационные входы и выходы микросхем являются входами и выходами модуля ЗУ увеличенной разрядности (рис. 5.2). Полученную совокупность микросхем называютмодулем памяти Модулем можно считать и единственную микросхему, если она уже имеет нужную разрядность. Один или несколько модулей образуютбанк памяти. |

| ||

|

|

|

| |

|

|

|

| |

|

|

|

| |

|

|

Для получения требуемой емкости ЗУ нужно определенным образом объединить несколько банков памяти меньшей емкости. В общем случае основная па- |

| |

|

|

|

| |

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

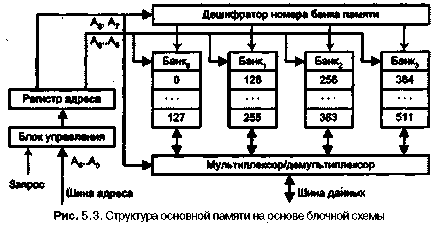

мять ВМ практически всегда имеет блочную структуру, то есть содержит несколькобанков. При использовании блочной памяти, состоящей из В банков, адрес ячейкиА преобразуется в пару (Ъ, w), где Ъ — номер банка, w — адрес ячейки внутри банка. Известны три схемы распределения разрядов адреса А междуЬиж • блочная (номер банка Ъ определяет старшие разряды адреса); • циклическая (Ъ = А тосШ: w = A div В); • блочно-циклическая (комбинациядвух предыдущих схем). Рассмотрение основных структур блочной ОП будем проводить на примере памяти емкостью 512 слов (29), построенной из четырех банков по 128 слов в каждом. Типовая структура памяти, организованная в соответствии с блочной структурой, показана на рис. 5.3. |

|

|

|

|

|

|

|

|

|

|

|

|

|