Лекции(2013)

.pdf

Проектирование цифровых устройств

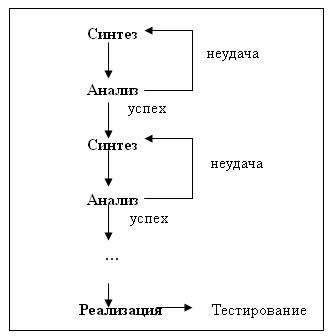

Проектирование – включает в себя процедуры синтеза и анализа.

Синтез – может выполнятся автоматически или вручную на разных этапах проектирования. Анализ - необходим для проверки правильности решений, принятых на очередном этапе синтеза.

Таким образом, проектирование – итерационный процесс, состоящий из последовательных этапов синтеза и анализа.

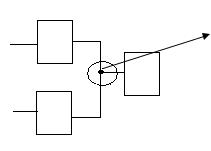

Рис.1. Последовательность этапов проектирования

Методы проектирования

Нисходящий – состоит из постепенной конкретизации функций, реализуемых устройством;

Восходящий – в чистом виде при проектировании не используется, а используется для разработки отдельных узлов или элементной базы (переход от конкретного к более общему);

Смешанный – включает в себя нисходящее проектирование целевого устройства в сочетании с восходящим проектированием отдельных узлов.

Способы реализации ЦУ:

1.Печатная плата из набора элементов различной степени интеграции (БИС, СИС, МИС) стандартных серий микросхем.

2.БИС

1)Заказные БИС. Проектирование выполняется на основе предварительно сформированных библиотек стандартных ячеек, аналогичных сериям элементов.

Водной микросхеме согласно схеме проектируемого устройства будут реализованы стандартные узлы и связи между ними. При этом все технологические операции по изготовлению БИС выполняются от начала и до конца. В результате, процесс изготовления является достаточно дорогим и долгим и используется только для крупносерийного производства.

2)Программируемые логические устройства (ПЛИС). CPLD – комплексные программируемые устройства, и FPGA - матрицы программируемых вентилей. Проектирование ПЛИС состоит в прокладке связей согласно схеме проектируемого устройства между нужными функциональными

1

элементами, которые находятся на интегральной микросхеме изначально в избыточном количестве.

Вслучае CPLD реализация состоит только в выполнении этапа металлизации (прокладки соединения).

Вслучае FPGA программатор по заданной программе согласно системе логических уравнений расплавляет ненужные перемычки (связи) или, наоборот, создает такие перемычки в нужных местах, ликвидируя изолирующий слой.

Таким образом, выполняется только конечный этап проектирования БИС. В результате, проектирование выполняется в короткие сроки и имеет гораздо более низкую стоимость, чем заказные БИС. В настоящее время это основной способ проектирования для средне и мелкосерийного производства.

Этапы нисходящего логического проектирования: Этап логического проектирования:

1.Регистровое представление

Определяет алгоритм функционирования устройства, его основные функциональные блоки, временное согласование их работы. Устройство описывается как совокупность многоразрядных регистров и операций преобразования информации между ними.

Алгоритм работы устройства описывается в виде последовательности операций преобразования, которые выполняются над многоразрядными числами, хранящимися в регистрах (элементах модели), и записи результатов операций в другие регистры.

Для анализа проекта на этом этапе применяется модель регистрового уровня представления устройства.

2.Функциональный уровень

Основные блоки устройства конкретизируются до стандартных функциональных узлов (счетчики, регистры), которые имеются в стандартных библиотеках. Сами библиотеки разрабатываются с помощью методов схемотехнического проектирования на уровне транзисторов.

Для анализа проекта на этом этапе применяются модели узлов (элементов модели устройства) функционального уровня представления, которые описывают алгоритмы работы элементов и их динамические параметры.

3.Логический уровень

Функциональные узлы представляются в виде структуры логических вентилей (элементов модели устройства). Модели вентилей кроме логической функции достаточно подробно описывают их динамические параметры.

Логическое проектирование устройства не обязательно должно проводиться на всех перечисленных уровнях. Конкретизация проекта выполняется до того элементного базиса, который выбран для реализации устройства.

После синтеза логической схемы выполняется

этап конструкторско-технологического проектирования, который включает:

1)выполнение наиболее оптимального размещения топологий элементов на кристалле БИС или микросхем на печатной плате;

2)выполнение оптимальной трассировки соединений между элементами;

3)уточненный расчет задержек элементов и соединений с учетом их топологии и паразитных связей;

Далее выполняется этап завершающего анализа - моделирование с уточненными задержками сигналов.

Последний этап - этап синтеза файлов с документацией для изготовления БИС или печатной платы в заводских условиях.

2

Для логического моделирования в настоящее время наиболее часто используются системы на основе таких стандартных языков описания схем как:

VHDL – язык описания цифровых схем, который был разработан в США по инициативе министерства обороны в 80-ых годах, получил наибольшее распространение в Европе;

Verilog – язык с аналогичными возможностями, получивший наибольшее распространение в Японии, Канаде, США.

Оба языка являются стандартными средствами представления входных данных для современных систем автоматизированного проектирования.

VHDL

Представление схемы возможно на следующих иерархических уровнях

1)уровень регистровых передач;

2)функциональный уровень;

3)вентильный уровень.

Допускается также смешанный способ описания элементов проектируемого устройства. Средства языка принципиально поддерживают два типа моделей: поведенческие и структурные.

Модели элементов

Поведенческие: |

Структурные |

математические, |

соединение элементов, |

табличные, |

описанных |

алгоритмические |

поведенческими моделями |

|

|

Описание на языке имеет блочную структуру. Блок это функционально завершенный модуль, который содержит либо общее писание объекта, либо исполняемый раздел.

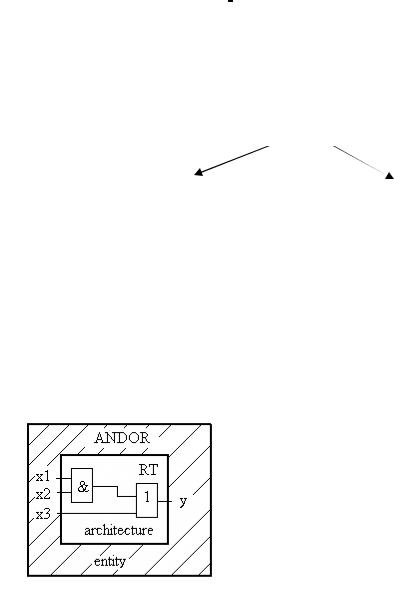

Описание модели состоит из двух блоков:

1)интерфейс – описывает входы и выходы модели как “черного ящика”;

2)архитектура – описывает внутреннее функционирование модели (исполнительный

блок).

L

Пример:

entity ANDOR is port(x1,x2,x3: in bit; y: out bit);

end ANDOR;

architecture RT of ANDOR is begin

y<=(x1 and x2) or x3; --операторы описания

--функционирования

end RT;

Один интерфейс может быть связан с разными архитектурными телами, которые по разному описывают его функционирование. Например, интерфейс ANDOR может быть связан на выбор с архитектурным телом RT или RT1, представленным ниже.

3

architecture RT1 of ANDOR is signal L:bit;

begin

L<=(x1 and x2); y<=L or x3; end RT1;

Архитектура RT представляет собой поведенческую модель элемента ANDOR, а RT1 – структурную модель, которая состоит из соединения двух поведенческих моделей с помощью внутреннего проводника L.

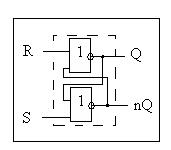

При описании в entity входных и выходных сигналов модели с помощью портов, необходимо задавать их тип. Наиболее распространенные типы: in, out, inout. Тип inout задается как для двунаправленных выводов элемента, которые поочередно используются для ввода и для вывода данных, так и для тех выходов, которые по обратным связям передают данные внутрь модели элемента. Например:

entity RS is port (R, S:in bit;

Q, nQ:inout bit);

Язык поддерживает следующую иерархию блоков: library→ package →разделы.

В качестве разделов могут быть объявлены типы данных, определены любые VHDL описания, например, моделей, конфигурации и т.д. Наиболее часто в пакеты помещают:

объявления типов данных;

объявления констант;

описания процедур;

описания функций,

описания компонентов.

Файл проекта может содержать один или более блоков проекта. Различаются первичные и вторичные блоки проекта.

Первичные блоки проекта:

декларация модели проекта в целом (entity);

декларация конфигурации;

декларация пакета.

Первичный блок может быть связан с несколькими вторичными блоками проекта, которые включают:

архитектурное тело модели проекта;

тело пакета.

Каждый первичный блок в данной библиотеке должен иметь уникальное простое имя. Каждое архитектурное тело, связанное с entity, должно быть уникальным.

Приведем пример описания пакета, который содержит две функции:

4

Интерфейс пакета, аналог Entity

Package w_vls is

function b2_int(signal w2, w1: bit) return integer;

function int_b4(signal IN:integer) return bit_vector;

end w_vls;

Тело пакета, аналог Architecture

Package body w_vls is

function b2_int(signal w2, w1:bit) --функция преобразования в К return integer is

(операторы) return K; end b2_int;

function int_b4(signal IN:integer) --функция преобразования в F return bit_vector is

(операторы) return F; end int_b4;

end w_vls;

Блоки проекта (первичные и вторичные) размещаются в библиотеках (рис.2).

Библиотека |

|

|

Команды |

. . . |

Библиотека |

||

ресурсов 1 |

|

ресурсов N |

на анализ |

|

|

|

|

VHDL-код |

VHDL- |

Рабочая |

SIMUL |

|

анализатор |

библиотека |

|

|

(компилятор) |

проэкта |

|

|

|

|

Результаты |

|

|

|

выполнения |

Рис.2. Организация выполнения VHDL-кода

Врабочей библиотеке размещаются файлы (блоки), анализируемые VHDL-анализатором (компилятором). Рабочая библиотека может быть только одна.

Вбиблиотеках ресурсов размещаются блоки, на которые ссылаются анализируемые

блоки.

Ресурсной библиотеки может не быть во время анализа. Ссылка на библиотеку осуществляется указанием ключевого слова library.

VHDL-анализатор читает файлы исходного VHDL-кода, читает ссылки на ресурсные библиотеки, и генерирует базу данных моделирования в рабочей библиотеке. Подготовленные данные инициализируются (устанавливаются в исходное состояние) и посылаются на выполнение программе моделирования SIMUL, которая выполняет задаваемые команды анализа и выдает результаты моделирования.

5

Основные ресурсные пакеты библиотеки IEEE VHDL: standard, textio подключаются автоматически. Ссылки на остальные библиотеки и их пакеты необходимо задавать явным образом. Так, например,

std_logic_1164 - распространенный пакет многозначной логики. Ссылка на него выполняется следующим образом :

library IEEE;

use std_logic_1164.аll;

Другой пример, ссылка на библиотеку STD, содержащую пакет STAND, и на библиотеку WORK, содержащую пакет FXP. Из пакета STAND используется только функция EROM, а из пакета FXP используются все объявленные в нем объекты. Ссылки на перечисленные объекты осуществляются следующим образом:

library STD, WORK; use STD.STAND.EROM; use WORK.FXP.all;

Область видимости библиотеки – от начальной ссылки до конца декларативной области, связанной с блоком проекта, где ссылка проявилась.

Область видимости сигналов: сигнал, декларированный в пакете, является видимым во всех объектах проекта, которые употребляют ссылку (use) на данный пакет. Сигнал, декларированный в entity как порт, является видимым во всех архитектурных телах, связанных с данным entity. Сигнал, декларированный в разделе деклараций архитектурного тела, видим только внутри данного архитектурного тела.

21.02.07

Структура VHDL описания и типы операторов

Package (optional) |

Entity (I/O) |

Architecture |

Параллельные |

операторы |

Последовательные |

операторы |

объявление signal

операторы безусловного, условного и выборочного присваивания значения сигналу оператор вызова процедуры оператор вызова компонента

process (предложение) generate (предложение) block (предложение)

assert (оператор сообщения)

объявление variable оператор вызова процедуры присваивание значения variable присваивание значения signal wait-оператор

операторы: if, case, loop, next, exit, return, null, assert

VHDL – язык описания параллельных процессов.

Параллельными процессами описываются блоки, которые работают параллельно друг с другом во времени. Внутри каждого параллельного блока от его начала до конца время может увеличивается только последовательно.

Операторы являются исполнительными единицами кода. Последовательные операторы выполняются в том порядке, в котором они расположены внутри параллельного процесса. Выполнение параллельных операторов не зависит от порядка их записи. Каждый такой оператор

6

выполняется каждый раз, когда один или несколько из его входных сигналов изменяет свое значение. Изменение значения сигнала называется событием.

Следует обратить внимание на то, что некоторые операторы могут выступать в качестве как параллельных, так и последовательных. Например, вызов процедуры. Как параллельные они будут работать в том случае, если будут записаны в виде отдельных элементов структурной модели, как последовательные, если будут записаны внутри параллельного оператора, например, такого, как process. Последовательные операторы могут располагаться только внутри параллельных операторов.

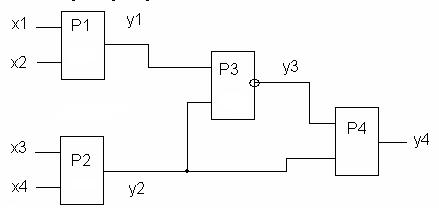

Рассмотрим пример работы схемы, изображенной на рис.3. Предположим, что все элементы имеют одинаковые задержки выходных сигналов (tз ).

Рис.3. Пример цифровой схемы

При изменении входных сигналов х1-х4 в момент времени t1 элементы Р1 и Р2 одновременно активизируются. Их переключение приведет к изменению значений сигналов у1 и у2 в момент времени t2=t1+tз. В тот же момент времени одновременно активизируются элементы Р3 и Р4, что приведет к изменению значений сигналов у3 и у4 в момент времени t3=t2+tз. И, наконец, изменение сигнала у3 в момент t3 приведет к повторной активизации Р4 и изменению у4 t4=t3+tз. t1 (xi var) y1 и y2

t2 (y 1 y2 var) y3 и y4 t3 (y3 var) y4

Элементы Р1-Р4 должны описываться как параллельные процессы с помощью параллельных операторов. Для описания алгоритма функционирования каждого из элементов Р1Р4 (внутри параллельного процесса) могут использоваться последовательные операторы.

Типы поведенческих моделей элементов

Если на вентильном уровне представления схемы элементами структурной модели являются логические вентили, соединенные связями, а задержки достаточно адекватно описывают переходные процессы внутри вентиля (инерционная задержка), то на функциональном уровне представления в качестве элементов используются более сложные функциональные узлы (регистры, счетчики, сумматоры). Функциональные модели чаще всего описывают реальные узлы и сопровождаются динамическими параметрами задержек этих узлов и ограничений на входные сигналы (время предустановки, удержания).

Регистровый уровень - это уровень более абстрактный, чем функциональный. Он не привязывается к конкретной элементной базе. Описание функционирования устройства, как последовательности этапов обработки и хранения векторных переменных в регистрах. Задержки

7

обычно равны 0 или носят условный характер для того, чтобы моделировать последовательность работы отдельных блоков относительно друг друга.

Для описания функционирования поведенческой модели любого уровня наиболее часто используются следующие три способа:

Таблица истинности (для большого количества неэквивалентных входов размерность таблицы резко увеличивается).

Система булевых уравнений (с увеличением сложности схемы размерность системы уравнений и сложность ее составления резко увеличивается).

Алгоритмическое описание – описание изменения выходных сигналов схемы под воздействием входных сигналов в виде алгоритма (наиболее компактный и универсальных способ описания).

Для создания поведенческих моделей вентильного уровня и наиболее простых элементов функционального уровня (мультиплексор, шифратор, RS –триггер и т.д.) обычно используются описания в виде таблиц истинности или булевых уравнений. В моделях функционального и регистрового уровня сложных узлов используется алгоритмический способ описания.

Язык VHDL не имеет разделения на уровни представления схемы и ее можно описывать смешанным образом (одни узлы более конкретно, другие более абстрактно).

Для описания в виде таблиц истинности или булевых уравнений наиболее удобны параллельные операторы безусловного, условного и выборочного присваивания значения сигналу, для алгоритмического описания наиболее удобен параллельный оператор process .

Типы объектов языка VHDL

Вязыке существует 3 типа объектов ( не путать с объектами проектирования)

1.Сигналы

2.Переменные

3.Константы

Сигналы

Сигналы используются для описания соединения между элементами схемы.

Сигнал связан с понятием времени. Он может измениться только тогда, когда процесс приостановится и ожидает следующего изменения входных сигналов. Для связывания параллельных операторов могут использоваться только сигналы. Порты, которые объявлены в entity, являются сигналами, а аргументы подпрограмм могут быть как сигналами так и переменными.

Типы сигналов:

bit – скалярный битовый сигнал; bit_vector – векторный битовый сигнал. Примеры:

bit_vector (7 downto 0); -- убывающий диапазон bit_vector (7 to 10); -- возрастающий диапазон

В обозначении любого диапазона слева всегда указывается старший разряд, а справа– младший.

std_logiс - поддерживает многозначную логику и функции разрешения (определения результирующих значений) сигналов в монтажных соединениях.

std_logiс_vector - поддерживает многозначную логику и функции разрешения сигналов в монтажных соединениях для векторных сигналов.

F -монтажное соединение нескольких выходов элементов

8

Рис.4. Монтажное соединение двух выходов. Функция F определяет значение результирующего сигнала, который поступает на вход следующего элемента

std_ulogiс - поддерживает многозначную логику, но не поддерживает монтажные соединения.

std_ulogic_vector - поддерживает многозначную логику, но не поддерживает монтажные соединения для векторных сигналов.

Многозначная логика включает следующее множество значений сигнала: 0,1- логические0 и 1

U – undefined – начальная неопределенность (произвольное начальное значение ) X - unknown – неопределенность, которая появилась в процесс се моделирования

Z – high impedance

W, L, H – слабые X,0,1 (эти значения используются при моделировании МОП – транзисторов. Они устанавливаются в результате действия тока, сила которого меньше стандартной или означают небольшой заряд ,накопленный в узле схемы).

“ - ” - безразличное значение (подразумевается , что оно не влияет на результат и может быть заменено любым другим значением)

Примеры объявления сигналов:

Signal A, C bit;

Signal Q std_logiс_vector (3 downto 0);

Переменные

Переменные, как правило, употребляются как промежуточные значения в алгоритме описания схемы. Переменные декларируются и видны только внутри процесса или подпрограммы. С

переменными не связано понятие времени. После выполнения оператора присваивания значение переменной сразу изменяется, и это изменение не является событием.

Пример:

Variable ROH, ROL: integer range 0 to 31; Variable BIN: bit;

Variable MEM: LTD (0 to 15; 0 to 31);

28.02.07

Константы

Константы на языке VHDL бывают двух типов: Generic и Const.

Const - статическая величина, которая обрабатывается один раз при компиляции и больше не изменяется. Задается в архитектуре или пакете.

Пример :

architecture EnA of Ent1 is constant t_p2: time:=10ns;

begin

. . . . . . . .

p1:process

constant t_hold: time:=5ns; begin

. . . . . .

end process p1; end EnA;

Generic – является фактически списком параметров, с помощью которого передаются константы при вызове экземпляра подсхемы. Он может динамически изменяться. Задается в интерфейсе, на который ссылаются архитектурные тела подсхем.

9

С помощью generic можно задать параметры портов внутри собственного интерфейса. Примеры:

entity KM is

generic(Busw: integer:=3);

port(Data:inout bit_vector(Busw-1 downto 0)); end KM;

generic(Delay: time:=20ns; long: integer:=8);

Ниже приведены различия между Generic и Const:

|

Generic |

|

Constant |

1) |

Только в entity; |

1) |

В architecture или package; |

2) |

Generic(“имя”: type:=value; |

2) |

Const “имя” type:=value; |

|

…………………. |

|

Const “имя”, “имя” type:=value; |

|

“имя”, “имя”: type:=value); |

|

|

3) |

Область действия: |

3) |

Область действия: |

|

В entity(включая порты), во всех |

|

Только внутри данной architecture, |

|

архитектурах, которые ссылаются |

|

а если в package – то во всех entity |

|

на данный entity. |

|

и architecture, которые его |

|

|

|

используют. |

Идентификатор

Идентификатор применяется для обозначения имен, назначаемых объектам языка и проекта. Он может состоять из букв, цифр и знака подчеркивания. Знак подчеркивания может располагаться только в середине идентификатора.

1)пишется в одну строку;

2)начинается с буквы;

3)нельзя начинать и заканчивать подчеркиванием;

4)не различаются большие и маленькие буквы;

5)нельзя использовать внутри пробелы и зарезервированные слова;

6)нельзя 2 подчеркивания подряд.

Комментарий

Знак комментария “ -- ” указывает на то, что текст, который располагается за ним и до конца строки, не является предложением языка VHDL.

Типы данных

В языке VHDL реализована строгая типизация. Это означает , что смешение разных типов данных в одной операции является ошибкой. Средства строгого контроля типов данных играют ответственную роль, поскольку позволяют уточнить намерения разработчика.

Тип – это поименованное множество значений с общими характеристиками. Подтип – подмножество значений данного типа. Например, тип NATURAL –это подтип типа

INTEGER.

Типы данных могут определяться в пакете, архитектурном теле и процессе. Типы данных подразделяются на скалярные и составные. Основные типы определены в пакете

STANDART.

10