Лекции(2013)

.pdf

модельного времени, когда значение сигнала s могло бы измениться, но не обязательно изменилось;

3) s’last_value -значение s до последнего события (предыдущее значение).

Пример:

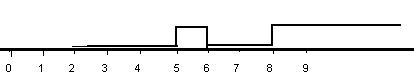

signal ex :bit;

ex <= ‘0’ after 2 s,‘1’ after 5 s,‘0’ after 6s,‘1’ after 8s;

0/U 0/U

Если сигнал будет объявлен как bit, то в начальный момент модельного времени t=0 по умолчанию ех=0, а если ех будет объявлен как STD_LOGIC, в момент времени t=0 будет по умолчанию ех = U. Рассмотрим пример для случая, когда сигнал будет объявлен как bit.

|

Тм=0 |

Тм=1 |

Тм=2 |

Тм=3 |

Тм=4 |

Тм=5 |

Тм=6 |

Тм=7 |

Тм=8 |

|

|

|

|

|

|

|

|

|

|

Ex’transaction |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

Ex’event |

false |

false |

false |

false |

false |

true |

true |

false |

true |

Ex‘last_value |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

Ex |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

Если сигнал s был объявлен как STD_LOGIC, то в момент Тм=2 Ex’event =true, Ex‘last_value =U для моментов Тм= 0, 1, 2, Ex= U для моментов Тм= 0, 1.

Параллельный оператор присваивания в момент Тм=0 вызывается безусловно и ставит в очередь события – изменения сигнала ех для соответствующих моментов времени, если новое значение отличается от предыдущего. Для момента Тм=2 было вычислено событие ех=0, но поскольку предыдущее значение ех также равно 0, события-изменения не будет.

Если мы хотим присвоить новое значение сигналу сразу в момент Тм=0, то это значение нужно присваивать без задержки.

Например:

ex <=‘1’, ‘0’ after 2 s,‘1’ after 5 s,‘0’ after 6s,‘1’ after 8s;

Атрибуты, формирующие сигналы

S’delayed (time) - формирует сигнал с ТЗ=time;

S’stable (time) - формирует TRUE, если в течении времени time не было событийизменений для S (s’event );

S’quite (time) - формирует TRUE, если в течении времени time не было попыток изменения S (s’transaction ).

…………

Пример: Процесс, который дополняет модель D-триггера

Check: process begin

wait until rising_edge (clk);

31

assert (d’stable (setup)) report(“setup time error”) severity error;

wait for hold;

assert (d’stable(hold)) report (“hold time error”) severity error;

end process;

D

Tsu (setup) и Th (hold) – константы типа time - времена предустановки и удержания информационного сигнала D по отношению к разрешающему (в данном случае, переднему) фронту сигнала clk

Th

Для проверки правильности функционирования последовательностной схемы необходимо проверять временные соотношения сигналов на ее входах. Данный процесс проверяет соблюдение времени предустановки и удержания информационного сигнала D относительно разрешающего фронта синхросигнала clk. Даная процедура ожидает переднего фронта сигнала clock. После этого, если в течении времени setup до этого события сигнал D не менялся, то время предустановки соблюдено. После переднего фронта процесс ожидает в течении времени hold. Если сигнал D не изменится, это значит, что время удержания также соблюдено.

Приведем еще один пример. Сообщение предупреждает о моментах времени, когда меняется значение сигнала Sum. При этом используется функция Now, которая возвращает текущее значение модельного времени, и атрибут image, который преобразует значение операнда из декларированного типа (в нашем случае time) в тип string.

assert (not(Sum'event))

report "Sum = new value "&time'image(Now)) severity warning;

Сообщение порождает следующий текст на консоли во время моделирования:

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

# : WARNING: Sum = new value 140000 ps

# : Time: 140 ns, Iteration: 1, TOP instance.

. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Атрибуты массивов: |

Атрибуты агрегированных сигналов |

|

|

A’right(N) |

правая граница N-того индексного диапазона |

A’left(N) |

левая граница N-того индексного диапазона |

A’high(N) |

верхнее значение N-того индексного диапазона |

A’low(N) |

нижнее значение N-того индексного диапазона |

A’range(N) |

N-тый индексный диапазон |

A’reverse_range(N) |

обратный N-тый индексный диапазон |

A’length(N) |

размер N-того индексного диапазона |

32

Пример:

Type ROM is array(0 to 15) of bit_vector (7 down to 0);

Signal R:ROM |

|

R’right(1) =15 |

R’right(2)=0 |

R’left(1)=0 |

R’left(2)=7 |

R’high(1)=15 |

R’high(2)=7 |

R’low (1)=0 |

R’low(2)=0 |

R’range(1)=0 to 15 |

R’range(2)= 7 downto 0 |

R’reverse_range(1)=15 downto 0 |

R’reverse_range(2)= 0 to 7 |

R’length(1)=16 |

R’length(2)=8 |

Пример:

Процедура сложения двух чисел h1+h2=sum begin

assert (h1’length=h2’length) and (h1’length=sum’length )

report (“vector length must be equal!”) severity error;

….

for i in sum’range loop ….

Атрибуты векторов: |

|

|

Параметр N здесь опускается (по умолчанию N =1) |

|

|

A’left |

крайнее левое значение |

|

A’right |

крайнее правое значение |

|

A’high |

максимальное значение |

|

A’low |

минимальное значение |

|

А’range |

диапазон вектора |

|

A’length |

длина вектора |

|

A’pos(x) |

номер позиции объекта Х в А |

|

A’val(К) |

значение позиции с номером К в А |

|

A’leftof (x) |

значение левой позиции от объекта Х в А |

|

A’rightof (x) |

значение правой позиции от объекта Х в А |

|

A’pred (x) |

значение позиции объекта Х-1 в А |

|

A’suss (x) |

значение позиции объекта Х+1 в А |

|

<тип>'image(A) |

значение А указанного типа (integer, bit_vector, и т.д.) |

|

|

преобразуется в тип string |

|

Пример: |

|

|

0 1 2 |

3 4 5 6 (позиции) |

|

type SEC is (a1, b1, a2, b2, a3, b3, w); |

|

|

Signal A:SEC |

|

|

A’left=0 |

A’leftof (a1)=1 |

Выходы за пределы |

A’right=6 |

A’rightof (w)=7 |

диапазона |

A’low=0 |

A’succ (b2)=a3 |

|

A’high=6 |

A’pred (b2)=a2 |

|

A’pos (a1)=0 |

A’val(4)=a3 |

|

33

Процедуры и функции

Процедуры и функции чаще всего задаются в package, но могут быть заданы в entity, architecture, process. Процедуры могут вызывать другие процедуры и функции, а функции – только другие функции. В процедурах и функциях не могут использоваться параллельные операторы.

Функция - подпрограмма, которая выполняет последовательный алгоритм и возвращает одно вычисленное значение заданного типа.

В ней могут быть объявлены переменные (variable), но не сигналы, которые связаны с понятием времени . Также не могут использоваться операторы, связанные с понятием времени (wait, операторы задержки).

Описание функции:

function <имя>(список входных параметров через “;”) return <тип результата> is

[объявление var, const] begin

последовательные операторы; return <тип результата>; end<имя>;

Ниже приведен пример описания функции. В пакете STD_LOGIC_1164 стандартной функции определения переднего фронта сигнала).

Function rising_edge(signal s:STD_LOGIC)

return boolean is |

s – 0->1= true – передний фронт; |

begin |

другие = false – хранение; |

return( s’event and( to_x01 (s) =’1’) |

( 0->0, 1->1, |

and(tо_x01(s’last_value)=’0’); |

x->1,x->0 |

end |

любые->z или ->х) |

… |

… |

Функция будет возвращать TRUE, если S изменится из 0 в1, а в других случаях будет FALSE. Для Falling_edge возвращается TRUE, если S изменится из 1 в 0.

Вспомогательная функция tо_x01 - преобразует девятизначный сигнал S к трехзначному (’0’, ’1’, ’Х’).

Вызов функции:

Показан на примере, в котором вызывается функция bool_to_SL, преобразующая bit-вый сигнал в сигнал типа std_logic .

architecture Ar of Ent is signal PAR_V: std_logic; signal data : bit;

begin

…

PAR_V=bool_to_SL(data);

…

имя функции |

параметр |

Количество и тип фактических параметров должны соответствовать объявленным в функции. Они могут быть только входными, и в ходе выполнения функцией не меняются. В качестве параметра может быть сигнал, переменная, константа, выражение.

34

В пакете функция сначала объявляется в интерфейсе пакета, а затем в теле пакета описывается.

Объявление в интерфейсе пакета: function bool_to_SL(X: boolean ) return std_logic;

Процедура – подпрограмма, содержащая логически завершенную часть кода VHDL, состоящую из последовательных операторов, аналогично телу процесса.

Описание процедуры:

procedure<имя> (список входных параметров через “;”) is [объявление signal, variable, const]

begin

последовательные операторы; end<имя>;

Входные параметры процедурой не меняются, а выходные могут быть изменены . Параметры могут иметь любой тип (signal, variable, constant, выражение).

Пример:

procedure add_vec; --процедура сложения 2-х векторов

(ad1, ad2: in bit_vector; c: in bit; signal sum: out bit_vector; signal con: out bit) is

variable cv:bit; begin

…

sum(i)<=…

cv:=…

con<=cv; end add_vec;

Вызов процедуры может быть: последовательным оператором, если выполняется в теле процесса, или параллельным оператором, если этот оператор используется, как элемент структурного описания схемы.

architecture…

signal c, a, b, rezp: bit;

signal res_s: bit_vector(3 downto 0); begin

c<=a and b;

add_vec(“1000”, “0110”, с, res_s, rezp); -- процедура вызывается как параллельный оператор

…

Если процедура задается в пакете, то в его интерфейсе она должна быть объявлена: procedure add_vec

(ad1, ad2: in bit_vector; c: in bit; signal sum: out bit_vector; signal con: out bit);

Приведем пример пакета, который содержит процедуры, функции и компоненты: package bitpackage is

procedure add_vec(ad1, ad2 : in bit; c: in bit;

35

signal sum: out bit_vector; signal con: out bit);

…

function boot_to_SL(X: boolean ) return std_logic;

…

component jkff generic(…); port(…); end component;

…

end bitpackage;

Package body bitpackage is function boot_to_SL (…) return is

(описание функции) end boot_to_SL;

. . .

procedure add_vec(…) is

(описание процедуры) end add_vec;

, . .

end bitpackage;

architecture A of jkff is -- компоненты описываются после конца тела пакета (описание компонента)

end A;

. . . .

Приведем пример задания процедур и функций в теле architecture:

entity lab4 is

generic (Lin: integer :=2; Lout: integer :=2);

port(

x:in STD_LOGIC_vector (Lin downto 0); x1: in STD_LOGIC;

y:out STD_LOGIC_vector (Lout downto 0); y1: out STD_LOGIC

);

end lab4;

architecture lab4 of lab4 is

------------------процедуры и функции--------------------------

-- функция +1 (по алгоритму синхронного счетч. с последовательн. переносом) function vecincr (vec: STD_LOGIC_vector)

return STD_LOGIC_vector is

variable k:STD_LOGIC:='1';

variable vec1:STD_LOGIC_vector (vec'length-1 downto 0); variable retval:integer:=0;

begin

if vec'length-1 > 0 then

for i in 1 to vec'length-1 loop k:=k and vec(i-1);

vec1(i):=(k and (not vec(i))) or((not k) and vec(i)); end loop;

else null;

end if; vec1(0):=not vec(0);

36

return vec1; end vecincr;

-- функция -1 (по алгоритму синхронного счетч. с последовательн. переносом) function vecdecr (vec: STD_LOGIC_vector)

return STD_LOGIC_vector is

variable k:STD_LOGIC:='1';

variable vec1:STD_LOGIC_vector (vec'length-1 downto 0); variable retval:integer:=0;

begin

if vec'length-1 > 0 then

for i in 1 to vec'length-1 loop k:=k and (not(vec(i-1)));

vec1(i):=(k and (not vec(i))) or((not k) and vec(i)); end loop;

else null;

end if; vec1(0):=not vec(0); return vec1;

end vecdecr;

-- процедура суммирования (по алгоритму параллельного сумматора c послед. переносом) procedure addvec (ad1,ad2: in STD_LOGIC_vector;

cin: in STD_LOGIC;

signal sum: out STD_LOGIC_vector; signal p:out STD_LOGIC) is variable c:STD_LOGIC;

begin

c:=cin;

if (ad1'length-1 > 0) and (ad2'length-1 > 0) and (ad1'length = ad2'length) then for i in 0 to ad1'length-1 loop

sum(i)<=c xor ad1(i) xor ad2(i);

c:=(ad1(i) and ad2(i)) or (ad1(i)and c) or(ad2(i)and c); end loop;

else null; end if; p<=c;

end addvec;

-- функция определения положительного фронта в многозначной логике, 1-есть фронт, 0- хранение, Х – нельзя -- определить был фронт или нет

function posedge (signal s: STD_LOGIC) return STD_LOGIC is

begin

if s'event=FALSE then return '0';

else if s'last_value ='0' and s ='1' then return '1'; else if s='0' then return '0';

else return 'X'; end if;

end if; end if;

end posedge;

-------------------------------------------

signal A,B: STD_LOGIC_vector (Lin downto 0); signal Sum: STD_LOGIC_vector (Lout downto 0); signal Cou: STD_LOGIC;

begin y<=vecdecr(x);

addvec(A,B,'0',Sum,Cou);

37

y1<=posedge(x1); end lab4;

Библиотека IEEE для проектирования цифровых устройств

Библиотека состоит более чем из десятка пакетов и предназначена для логического моделирования и синтеза цифровых устройств. Фундамент языка VHDL представляет собой пакет STANDART, в котором определены операции языка, основные типы данных и функции. Фактическим стандартом стал пакет Std_Logic_1164, пакеты Numeric_std и Numeric_bit были утверждены в качестве стандарта для упрощения проектирования устройств, использующих арифметические операции. Функции этих пакетов перегружают (замещают при вызове) ряд стандартных операций и функций над целыми числами, а также одноименные операции и функции более ранних пакетов Std_Logic_arith (Std_Logic_signed Std_Logic_unsigned), предназначенных для тех же целей. Функции перечисленных пакетов поддерживаются всеми синтезаторами и наиболее оптимально отображаются в аппаратуре.

Пакет Std_Logic_1164 и многозначная логика

Многозначная логика реализована в стандартной библиотеке IEEE STD_LOGIC_1164. В соответствии с ней скалярный сигнал может принимать одно из 9 значений:

U- неинициализированное значение; X- сильное неизвестное (0 или 1); 0, 1 - сильное значение;

Z- высокий импеданс (состояние отключения от источника сигнала); L, H - слабые значения (0 и 1);

W- слабое неизвестное (0 или 1); _ - безразличное значение.

L, H, W используются для моделирования ряда эффектов в МОП - схемах, это слабые значения токов и небольшие значения зарядов в емкостях, по сравнению с сильными значениями, которые по умолчанию формируются выходами стандартных микросхем (они имеют усилительный выходной каскад). Например значение Н принимает выходной сигнал pull-up резистора или схемы с открытым коллектором, а значение L- сигнал на открытом эмиттере.

Значение U назначается всем сигналам в начальный момент моделирования (t=0). Cохранение сигналом значения U в процессе моделирования, означает, что этот сигнал так и не смог получить конкретное значение в процессе работы схемы, т.е. – ошибку проектирования. Появление значения Х в процессе моделирования демонстрирует ошибочную ситуацию, в результате которой невозможно в общем случае предсказать конкретное значение сигнала. Например, подача на входы элемента комбинации сигналов не предусмотренной логикой его работы.

Безразличное значение может использоваться при описании таблиц переходов не полностью определенных автоматов и при минимизации заменяться на «0» или «1». Однако не многие синтезаторы поддерживают такую возможность. Если же подавать такие значения на входы элементов, то это будет приводит к неопределенности их состояния.

В библиотеке существует два вида логики: logic и ulogic.

Ulogic - не разрешаемая логика, в ней не разрешены монтажные соединения элементов. Logic - разрешаемая логика. Для нее возможны функции разрешения для определения значений

результирующих сигналов в монтажных соединениях. Типичным примером является общая шина, по которой могут передаваться данные от нескольких источников – подключенных к шине устройств. С точки зрения VHDL это означает, что одному и тому же сигналу (например, шине) значения назначаются несколькими параллельными процессами (моделями разных устройств). Каждый скалярный сигнал VHDL хранится в виде вектора переменной длины. Длина вектора равняется количеству процессов, которые параллельно могут назначать значения сигналу(рис.?).

38

Сигнал Х1 |

|

|

. . . |

F |

Сигнал Y |

Сигнал Хn

Рис.? Назначение значения сигналу несколькими параллельными процессами

Приведем таблицу значений Y стандартной функции разрешения F пакета STD_LOGIC_1164. Значения сигналов можно расположить в порядке их приоритетов: ’U’ →’Х’ →’0’,’1’ →’W’ →’L’,’H’ →’Z’. Два сигнала равной силы, но разных значений дают неопределенность. Сигнал ‘Z’ подавляется любым типом сигналов. Сигнал ‘-‘ не должен появляться входах элементов.

X1/X2 |

U |

X |

0 |

1 |

Z |

W |

L |

H |

- |

U |

U |

U |

U |

U |

U |

U |

U |

U |

U |

X |

U |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

U |

X |

0 |

X |

0 |

0 |

0 |

0 |

X |

1 |

U |

X |

X |

1 |

1 |

1 |

1 |

1 |

X |

Z |

U |

X |

0 |

1 |

Z |

W |

L |

H |

X |

W |

U |

X |

0 |

1 |

W |

W |

W |

W |

X |

L |

U |

X |

0 |

1 |

L |

W |

L |

W |

X |

H |

U |

X |

0 |

1 |

H |

W |

W |

H |

X |

- |

U |

X |

X |

X |

X |

X |

X |

X |

X |

Например:

В примере тестируется работа элемента памяти 8*8 с двунаправленными выводами данных, которые подключаются к общей шине схемы. Сигналы на шину могут поочередно выдавать элемент памяти Mem1 и некоторое устройство ELEM. Когда одно устройство выдает сигналы на шину, другое устройство должно от нее отключаться (значение сигнала - ‘Z’). Двунаправленные выводы элемента памяти образуют внутреннюю общую шину, на которой объединяются сигналы внешней шины и выходного 3-х стабильного буфера элемента. Для правильной работы элемента управление его внутренней шиной должно также подчиняться условию поочередности.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity Bdir_test is end Bdir_test;

architecture Bdir_test of Bdir_test is

component Bdir is

port( w : in STD_LOGIC; r : in STD_LOGIC; A : in integer;

F : inout STD_LOGIC_VECTOR(7 downto 0)); end component Bdir;

signal IO: STD_LOGIC_VECTOR(7 downto 0); --общая шина

signal w,r: STD_LOGIC; -- разрешение записи чтения для элемента памяти signal A: integer; --адрес элемента памяти

begin

Mem1: Bdir port map(w,r,A,IO); -- элемент памяти Mem1, подключенный к шине

39

ELEM:process |

-- устройство ELEM, подключенное к шине |

begin |

|

IO<="11100110" ; |

-- имитация выдачи сигналов на шину элементом ELEM |

wait for 64ns; |

|

IO<="ZZZZZZZZ" ; |

|

wait for 83ns; |

|

IO<="11100000" ; |

|

wait for 25ns; |

|

IO<="01010000" ; |

|

wait for 250ns; |

|

IO<="ZZZZZZZZ" ; |

|

end process ELEM; |

|

end Bdir_test; |

|

entity Bdir is |

-- упрощенная модель элемента памяти |

port( w : in STD_LOGIC; |

--вход разрешения записи в память |

r : in STD_LOGIC; |

-- вход разрешения чтения (выдачи) из памяти |

A : in integer; |

-- адресный вход |

F : inout STD_LOGIC_VECTOR(7 downto 0):=(others=>'Z') ); --двунаправленный вывод

end Bdir; |

-- данных |

|

|

architecture Bdir of Bdir is |

|

type memory is array(0 to 7) of STD_LOGIC_VECTOR(7 downto 0); |

|

signal Mem: Memory:=(others=>(others=>'0')); -- матрица памяти 8х8 |

|

begin |

|

process |

|

variable F_w: STD_LOGIC_VECTOR(7 downto 0); --внутренний выходной буфер |

|

begin |

|

wait on w,r,A; |

|

if (r='1') then F_w:=Mem(A); |

-- чтение из ячейки памяти во внутренний буфер |

else F_w:="ZZZZZZZZ"; |

--внутренний буфер отключен от вывода F |

end if; |

|

if w='1' then Mem(A)<=F; |

-- запись в ячейку памяти с вывода F |

else null; |

|

end if; |

|

F<=F_w; -- внутренний буфер подключен к выводу F |

|

end process; |

|

end Bdir; |

|

Для отдельных соединений элементов внутри схемы можно описать в модели схемы |

|

собственную функцию разрешения типа «монтажное ИЛИ» или «монтажное И». Например, для «монтажное И»:

Х1 Х2 Y

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

Х 0 |

|

1 |

Х Х |

|

0 |

U |

0 |

1 |

U |

U |

. . . . . . .

40