Уч пос Электроника

.pdfМинистерство Российской Федерации по связи и информатизации

Сибирский государственный университет телекоммуникаций и информатики

В.Л. Савиных

ЭЛЕКТРОНИКА

Учебное пособие для специальностей 071 700, 200 700,

200 800, 200 900, 201 000, 201 100, 201 200, 201 400

Новосибирск

2004

УДК 621.382

Рассматривается принцип работы, характеристики и параметры цифровых и аналоговых микросхем. Кратко описываются технологические процессы, применяемые при изготовлении ИМС.

ктн, доц. В.Л. Савиных,

Для студентов дневной и заочной форм обучения специальностей

071700, 200700, 200800, 200900, 201000, 201100, 201200, 201400.

Кафедра технической электроники. Ил. 58, табл. 18, список лит. 5 назв. Рецензент ктн, доц. Матвеев В.А.

Утверждено редакционно-издательским советом СибГУТИ в качестве учебного пособия

@ Сибирский государственный университет телекоммуникаций и информатики, 2004 г.

2

Содержание

1Цифровые интегральные микросхемы…………………………….….5 1.1 Основы алгебры логики………………………………………………..5 1.2 Параметры ЦИМС……………………………………………………...9

1.3 Диодно-транзисторная логика………………………………………..11

1.4 Транзисторно-транзисторная логика…………………………………14

1.5 ТТЛ со сложным инвертором…………………………………………16

1.6 ТТЛ с открытым коллекторным выходом……………………………18

1.7 ТТЛ с тремя состояниями на выходе…………………………………19

1.8 ТТЛШ…………………………………………………………………...20

1.9 КМДП…………………………………………………………………...21

2Операционный усилитель……………………………………………25

2.1Параметры и характеристики ОУ……………………………………25

2.2Структура ОУ…………………………………………………………26

2.3Дифференциальный усилитель………………………………………27

2.4Составной транзистор………………………………………………..28

2.5Источники тока……………………………………………………….29

2.6Схема сдвига уровня…………………………………………………29

2.7Эмиттерный повторитель…………………………………………….31

2.8Инвертирующий усилитель на ОУ………………………………..…31

2.9Неинвертирующий усилитель на ОУ……………………………..…32

3 Технологические основы производства ППИМС…………..………42

3.1Подготовительные операции…………………………………..……..42

3.2Эпитаксия……………………………………………………...………43

3.3Термическое окисление………………………………………………44

3.4Литография……………………………………………………….……46

3.5Легирование……………………………………………………………49

3.6Нанесение тонких пленок………………………………………….….53

4Полупроводниковые ИМС…………………………………………….56 4.1 Методы изоляции элементов в ППИМС……………………………..58 4.2 Планарно-эпитаксиальный биполярный транзистор…………………60 4.3 Планарно-эпитаксиальный биполярный транзистор со скрытым

слоем………………………………………………………………………64 4.4 Разновидности биполярных транзисторов………………………..…65 4.5 Интегральные диоды ………………………………………………....68 4.6 Полевые транзисторы ………………………………………………...70 4.7 Полупроводниковые резисторы………………………………………75 4.8 Полупроводниковые конденсаторы …………………..…………….78

5Гибридные ИМС…………………………………………………...….81

5.1 Подложки ГИМС………………………………………………….…..81

3

5.2Резисторы ……………………………………………………………....82

5.3Конденсаторы…………………………………………………………..84

5.4Катушки индуктивности………………………………………………85

5.5Пленочные проводники и контактные площадки…………….…….85

5.6Навесные компоненты…………………………………………………86

5.7Методы формирования заданной конфигурации пленочных элементов ГИМС…………………………………………………………………….86

7 Литература……………………………………………………………….

4

1 ЦИФРОВЫЕ ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ

1.1 Основы алгебры логики

1.1.1Основные определения

Взависимости от отсутствия или наличия элементов памяти цифровые устройства делятся на комбинационные устройства (КУ) и конечные автоматы (последовательные устройства). Выходные сигналы КУ определяются совокупностью (комбинацией) входных сигналов, действующих на некотором интервале времени. Наличие элементов памяти в конечных автоматах обусловливает зависимость выходных сигналов на рассматриваемом интервале от совокупности входных сигналов, действующих как на этом интервале времени, так и на ряде предшествующих интервалов. В комбинационном

устройстве связь между входными x1, x2,… хn и выходными у1, у2, …, уn сигналами цифрового устройства может быть задана функциями вида:

y1 |

f1 (x1 , x2 |

, ..., xn ), |

|

||||||

|

|

|

|

|

|

|

|

|

|

y2 |

f2 (x1 , x2 , ..., xn ), |

(1.1) |

|||||||

y |

n |

f |

m |

(x , x |

2 |

, ..., x |

n |

), |

|

|

|

1 |

|

|

|

||||

Особенность входных сигналов (независимых переменных) и выходных сигналов (функций) заключается в том, что они могут принимать только два значения: 1 или 0. Такие функции называются логическими, или

переключательными, или булевыми.

Раздел математики, который изучает логические функции, называется

алгеброй логики.

Наиболее часто логическая функция задается с помощью таблицы. В строках таблицы записываются все возможные наборы значений аргументов и указываются значения логической функции, которые они принимают на каждом наборе. Эту таблицу принято называть таблицей истинности. Для m переменных может быть 2m различных наборов. Пример логической функции трех аргументов x1, х2, x3 приведен в таблице 1.1.

Таблица |

1.1 |

|

|

|

|

|

|

|

|

|

Номер |

|

Х3 |

Х2 |

Х1 |

У |

Номер |

Х3 |

Х2 |

Х1 |

У |

набора |

|

|

|

|

|

набора |

|

|

|

|

0 |

|

0 |

0 |

0 |

0 |

4 |

1 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

5 |

1 |

0 |

1 |

1 |

2 |

|

0 |

1 |

0 |

0 |

6 |

1 |

1 |

0 |

1 |

3 |

|

0 |

1 |

1 |

1 |

7 |

1 |

1 |

1 |

1 |

Если рассматривать наборы x3, x2, x1 как двоичные числа, то удобно ввести десятичную нумерацию наборов. Например, набор x3= 1, х2=1, X1 = 0 имеет номер 6.

5

Вместо таблицы истинности иногда логическую функцию удобно задавать словесным описанием. Например, функция у, заданная таблице 1.1, может быть словесно определена так: у=1 в том случае, если не менее двух аргументов принимают значение 1.

По способу соединений элементов цифровые устройства делятся на два типа: на устройства со статическими (потенциальными) связями между элементами и устройствами с динамическими (импульсными и импульснопотенциальными) связями между элементами. Учитывая широкое распространение в интегральной схемотехнике элементов с потенциальными связями, в дальнейшем будем ориентироваться только на элементы этого класса.

1.1.2 Некоторые логические функции и реализующие их логические элементы

Логическое сложение (дизъюнкция). Логическая функция у является логической суммой (дизъюнкцией) переменных y=f(х1, х2, ..., хn), если она равна 1 в тех наборах, на которых хотя бы одна независимая переменная равна 1, и равна 0 в остальных наборах. Пример функции у, являющейся логической суммой двух переменных х1 и х2, приведен в таблице 1.2.

Таблица 1.2 |

|

|

Таблица 1.3 |

|

|

|

||

Номер |

Х2 |

Х1 |

У |

|

Номер |

Х2 |

Х1 |

У |

набора |

|

|

|

|

набора |

|

|

|

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

2 |

1 |

0 |

1 |

|

2 |

1 |

0 |

0 |

3 |

1 |

1 |

1 |

|

3 |

1 |

1 |

1 |

Логическое сложение двух переменных принято обозначать следующим образом: y=х1 х2, а логическое сложение n переменных

y=x1 х2 … хn |

(2) |

Схема, с помощью которой из входных переменных х1, х2, ..., хn образуется их логическая сумма, называется логическим элементом ИЛИ. Графическое обозначение этого элемента при двух входных переменных приведено на рисунке 1.la.

Логическое умножение (конъюнкция). Логическая функция у является логическим произведением (конъюнкцией) переменных

x1, х2, ..., хn, если она равна 1 только на тех наборах, на которых все переменные одновременно равны 1. Пример функции у, являющейся логическим произведением двух переменных х1 и х2, приведен в таблице 3.

6

Логическое умножение двух переменных будем обозначать так же, как обозначают обычное алгебраическое умножение y=x1 x2. Для n переменных можно записать:

Y=х1 x2 … xn (1.3)

а |

б |

в |

г |

д |

|

|

Рисунок 1.1 |

|

|

Схема, с помощью которой из входных переменных х1, х2, ..., хn образуется их логическое произведение у, называется логическим элементом И. Графическое обозначение этого элемента при двух входных переменных приведено на рисунке 1.1б.

Логическое отрицание (инверсия). Логическая функция у является логическим отрицанием переменной х, если ее значение противоположно значению переменной х. Функция у, являющаяся отрицанием переменной х, приведена в таблице 1.4. Логическое отрицание принято обозначать Таблица 1.4.

х |

у |

|

|

|

|

|

|

y x . |

Схема, |

с помощью которой реализуется |

|||||

|

|

||||||

0 |

1 |

логическое отрицание, называется логическим элементом НЕ. |

|||||

Графическое обозначение этого элемента приведено на рисунке |

|||||||

1 |

0 |

||||||

|

|

|

|

|

|||

1.lв .

При построении современных цифровых устройств нашли широкое применение некоторые логические функции, являющиеся простыми комбинациями рассмотренных.

Логическое сложение с отрицанием (стрелка Пирса). Логическая функция у является логической суммой с отрицанием независимых переменных х1, х2, ..., хn, если она равна 0 на тех наборах, на которых хотя бы одна переменная равна 1. Пример указанной функции при двух переменных приведен в таблице 1.5.

Логическое сложение с отрицанием обозначается y x1 x2 . Иногда в литературе пользуются обозначением y=х1+х2. В дальнейшем будем использовать первое обозначение. Для функции n переменных можно записать:

y x1 x2 ... xn

Схема, реализующая функцию «логическое сложение с отрицанием», называется логическим элементом ИЛИ-НЕ (элементом Пирса).

7

Графическое обозначение элемента при двух переменных приведено на рисунке 1.1г.

Логическое умножение с отрицанием (штрих Шеффера). Логическая функция у является логическим произведением с отрицанием

Таблица 1.5 Таблица 1.6

Номер |

Х2 |

Х1 |

У |

набора |

|

|

|

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

2 |

1 |

0 |

0 |

3 |

1 |

1 |

0 |

Номер |

Х2 |

Х1 |

У |

набора |

|

|

|

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

2 |

1 |

0 |

1 |

3 |

1 |

1 |

0 |

независимых переменных х1, х2, ..., хn, если она равна 1 только на тех наборах, на которых хотя бы одна переменная равна 0. Пример функции у, являющейся логическим произведением с отрицанием двух переменных, приведен в таблице 1.6.

Логическое умножение с отрицанием для двух переменных будем обозначать y x1 x2 . Иногда в литературе встречается обозначение

y x1 x2 . Для реализации функции «логическое умножение с отрицанием» используется логический элемент, называемый элементом И-НЕ (элементом Шеффера). Его графическое обозначение приведено на рисунке 1.1д.

1.1.3 Основные законы и соотношения алгебры логики

При проектировании цифровых устройств часто требуется преобразовать структурные формулы. Для этой цели используются соотношения, вытекающие из законов алгебры логики.

С помощью таблиц 2-4 легко могут быть проверены свойства логического сложения, умножения и инверсии:

0 0 0, |

|

|

|

|

|

|

|

|

|

|

|

0 1 1, |

|

|

0 0 0, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 1 0, |

|

0 |

1 |

|

|||||

1 1 1, |

|

|

|

|

|

||||||

x 1 1, |

|

|

1 1 1, |

|

|

|

|

|

|

0 |

|

(1.5), |

(1.6), |

1 |

|

(1.7). |

|||||||

|

|

|

|

||||||||

x x x, |

|

x 1 x, |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

x |

|

|||

|

|

|

|

|

|

|

|||||

|

|

|

x |

|

|||||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

x 0 x, |

|

x x x, |

|

|

|

|

|

|

|

||

x x 1 |

|

|

x 0 0, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x x 0. |

|

|

|

|

|

|

|

|

Основные законы соответственно для логического сложения |

и умножения |

||||||||||

записываются:

8

Переместительный закон |

|

x y=y x, x y=y x. |

(1.8) |

Сочетательный закон |

|

(x y) z=x (y z), (x y) z=x (y z). |

(1.9) |

Распределительный закон

z(x y)=x z y z, (z x)(z y)=z (x y). (1.10)

Закон двойственности (Правило де Моргана)

|

|

|

|

|

|

|

x y x y, |

x y x y. |

(1.11) |

||||

На основании правила де Моргана логическое сложение может быть заменено умножением и, наоборот, при соответствующем инвертировании переменных и всей логической функции. На практике часто пользуются другой интерпретацией указанного правила: функции логического сложения и умножения реализуются одним и тем же логическим элементом, который в зависимости от кодировки сигналов на его входе и выходе может выполнять или функцию И, или функцию ИЛИ.

Все законы алгебры логики легко проверяются подстановкой возможных комбинаций значений 0 и 1 в левую и правую части.

Для преобразования структурных формул применяется ряд тождеств, важнейшие из которых определяют правила поглощения

x x y = x, |

x(x y) = x |

(1.12) |

|||||||||||||||||

и склеивания |

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x y xy = x, |

(x y) (x y ) = x. |

(1.13) |

|||||||||||||||||

Приведем еще несколько полезных соотношений: |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

x xy = x y |

|

|

|

|

(1.14) |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

x |

|

|

x y= |

|

|

(x y), |

(1.15) |

||||||||||||

y |

xy |

||||||||||||||||||

|

|

|

|

|

|

||||||||||||||

|

|

|

|

||||||||||||||||

x y x z= xy (x v z). |

(1.16) |

||||||||||||||||||

Соотношения (1.12 – 1.16) могут быть доказаны с помощь (1.5) - (1.11).

1.2Параметры цифровых интегральных микросхем

1.2.1Параметры цифровых интегральных микросхем (ЦИМС), имеющие размерность напряжение.

Напряжение питания ЕПИТ. Напряжение соответствующее логическому

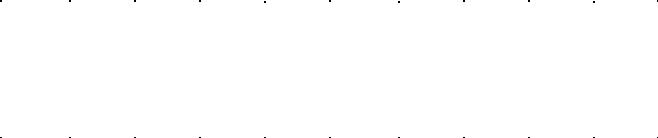

0 и логической 1 . При позитивной логике низкий уровень напряжение U0 соответствует логическому 0, а высокий уровень U1- логической 1. Логический перепад напряжений U= U1 -U0 (рисунок 1.2).

9

а) |

б) |

|

Рисунок 1.2 |

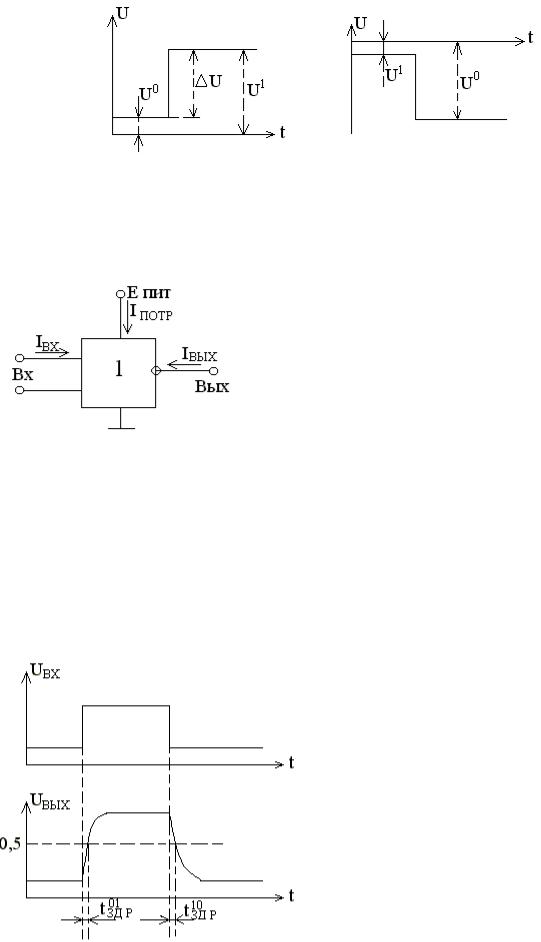

1.2.2 Параметры, соответствующие размерности тока.

I0ВХ- входной ток, соответствующий логическому 0 на входе, I1ВХ- входной ток, соответствующий логической 1 на

входе, I0ВЫХ- выходной ток, соответствующий логическому 0 на

выходе, I1ВЫХ -выходной ток, соответствующий логической 1 на

выходе, I0ПОТР- ток потребляемый Рисунок 1.3

микросхемой, соответствующий логическому 0 на выходе, I1ПОТР- ток потребляемый микросхемой, соответствующий логической 1 на выходе. Токи, втекающие в микросхему, считаются положительными, вытекающие – отрицательные.

1.2.3 Параметры, имеющие размерность мощности.

Р0ПОТР= I0ПОТР ЕПИТ, |

Р1ПОТР= I1ПОТР ЕПИТ, |

РПОТРСР =(Р0ПОТ +Р1ПОТР) 2 |

1.2.4 Параметры, имеющие размерность время.

Рисунок 1.4

10