Схемы цепей

.docРассматриваемые разделы

Схемы цепей питания биполярных резисторов…………………………………………………………………………………..2

Схемы цепей питания полевых транзисторов……………………………………………………………………………………..5

Составные транзисторы…………………………………………………………………………………………………………………………6

Генераторы стабильного тока (ГСТ)………………………………………………………………………………………………………6

Генераторы стабильного тока на полевых транзисторах……………………………………………………………………8

Генераторы стабильного тока на полевых и биполярных транзисторах…………………………..………………9

Источники опорного напряжения……………………………………………………………………………………………………….10

Однокаскадные усилители……..…………………………………………………………………………………………………………..11

Двухкаскадные усилители….……………………………………………………………………………………………………………….13

Трехкаскадные усилители….……………………………………………………………………………………………………………….22

Четырехкаскадные усилители….…………………………………………………………………………………………………………27

Специальные усилители…..…………………………………………………………………………………………………………………29

Дифференциальные каскады (ДК)………………………………………………………………………………………………………30

Схемы цепей питания биполярных транзисторов

Рисунок 1. Подача напряжений смещения биполярного транзистора:

а) для n-p-n транзистора

б) другой вид графического представления

в) для p-n-p транзистора

Рисунок 2. Схемы с фиксированным смещением

а) с фиксированным током базы через Rб

б) с фиксированным напряжением на базе

в) тоже с дросселем в цепи базы

Рисунок 3. Схемы биполярных транзисторов с автоматическим смещением (эмиттерная стабилизация):

а) основная

б) с дросселем в качестве нагрузки коллектора

в) в трансформаторном каскаде

г) с двухполярным питанием

Рисунок 4. Схемы питания биполярных транзисторов с автоматическим смещением (коллекторная стабилизация)

а) основная схема

б) с использованием фильтра

Рисунок 5. Схемы термокомпенсации точки покоя:

а), б) резистором с отрицательным температурным коэффициентом

в) резистором с положительным температурным коэффициентом

Рисунок 6. Схем термокомпенсации точки покоя:

а) включением диода в цепь базового делителя

б) включением диода в цепь базового делителя при наличии Rэ

в) в схеме с трансформаторным входом

г) включением диода в цепь обратной связи по постоянному току

Схема цепей питания полевых транзисторов:

Рисунок 7. Подача напряжения смещения в полевом транзисторе:

а) с фиксированным напряжением затвор-исток

б), в) с автоматическим смещением в цепи истока

г) с автоматическим смещением и с частичным включением в цепь истока

д) с делителем в цепи затвора

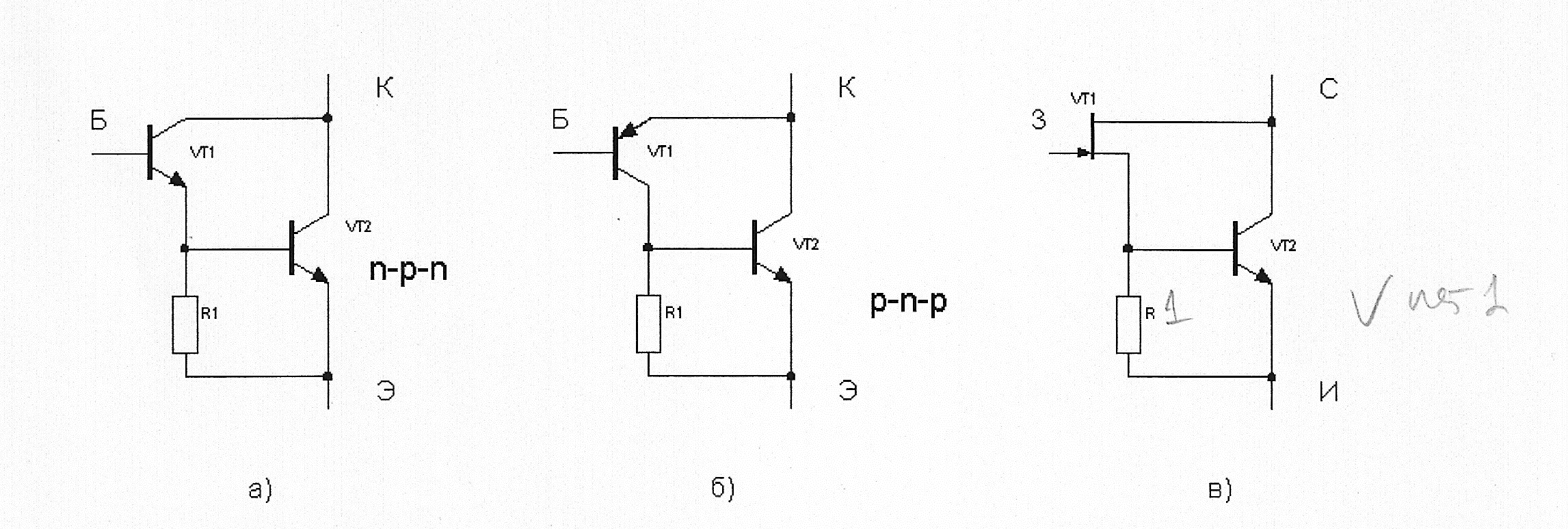

Составные транзисторы

Рисунок 8. Составные транзисторы:

а) Схема Дарлингтона

б) схема Нортона

в) с полевым транзистором

Генераторы стабильного тока (ГСТ)

Рисунок 9. Варианты схем токового зеркала:

а) ГСТ Уилсона

б) с регулировкой тока с резисторами в цепи эмиттеров

в) при низковольтном питании

Рисунок 10. ГСТ с повышенным выходным сопротивлением.

а) ГСТ, смещенный другим ГСТ

б) соединение транзисторов ОЭ-ОБ

в) для тока свыше 3 мА

г) двухвыводной ГСТ (встречное включение двух схем ГСТ [см. рис. 9(в)])

Генераторы стабильного тока на полевых транзисторах

Рисунок 11. ГСТ на полевых транзисторах:

а) простейшая схема

б) с увеличенным выходным сопротивлением

в) составной ГСТ ОИ-ОБ с увеличенным напряжением источника питания

Генераторы стабильного тока на полевых и биполярных транзисторах

Рисунок 12. Гибридные ИСТ:

а) с повышенной стабильностью выходного тока

б) с высоким выходным сопротивлением

Источники опорного напряжения

Рисунок 13. источники опорного напряжения:

а) с уменьшенным выходным сопротивлением

б) на многоэмиттерном транзисторе

в) с использованием перехода база-эмиттер

г), д) с регулируемым стабильным напряжением, последний с уменьшенным выходным сопротивлением, за счёт ООС на VT1

Однокаскадные усилители

Рисунок 14. Усилительные каскады с ОЭ:

а), б) с эмиттерной стабилизацией, без ОС по сигналу

в), г) с эмиттерной стабилизацией, и ОС по сигналу

д), е) с коллекторной стабилизацией

Рисунок 14. Усилительные каскады с ОК:

а) каноничная схема

б) с большим входным сопротивлением, не шунтируемым делителем

в), г) с двухполярным питанием и транзисторами разной проводимости

д) с токовым зеркалом в качестве генератора стабильного тока

Двухкаскадные усилители:

Рисунок 16. Усилители по схеме ОЭ-ОЭ:

а), б), в) на комплиментарных БТ

г) на БТ одинаковой проводимости

Рисунок 16. Усилители по схеме ОЭ-ОЭ:

Рисунок 16. Усилители по схеме ОЭ-ОЭ:

д), е) на БТ одинаковой проводимости

Рисунок 17. Усилители на ПТ и БТ:

а) ОИ-ОЭ

б) с ОС

в) на составном резисторе Дарлингтона

Рисунок 18. Усилители с повышенным входных сопротивлением:

а) на БТ

б) на ПТ

в) на МОП ПТ

Рисунок 19. Повторители напряжений:

а), б) на ПТ и БТ

в) с динамической нагрузкой

Рисунок 20. Двухкаскадный усилитель с динамической нагрузкой.

Рисунок 21. Двухкаскадный усилитель с входным согласующим дифференциальным трансформатором и конечным каскадом по схеме Дарлингтона.

Рисунок 22. Усилители с последовательным питанием.

Рисунок 23. Усилитель с нейтрализацией входной емкости.

Рисунок 24. Двухкаскадный усилитель ОЭ-ОЭ

а) с емкостной связью

б) с гальванической связью

Рисунок 24. Двухкаскадный усилитель ОЭ-ОЭ

в) на транзисторах разной проводимости

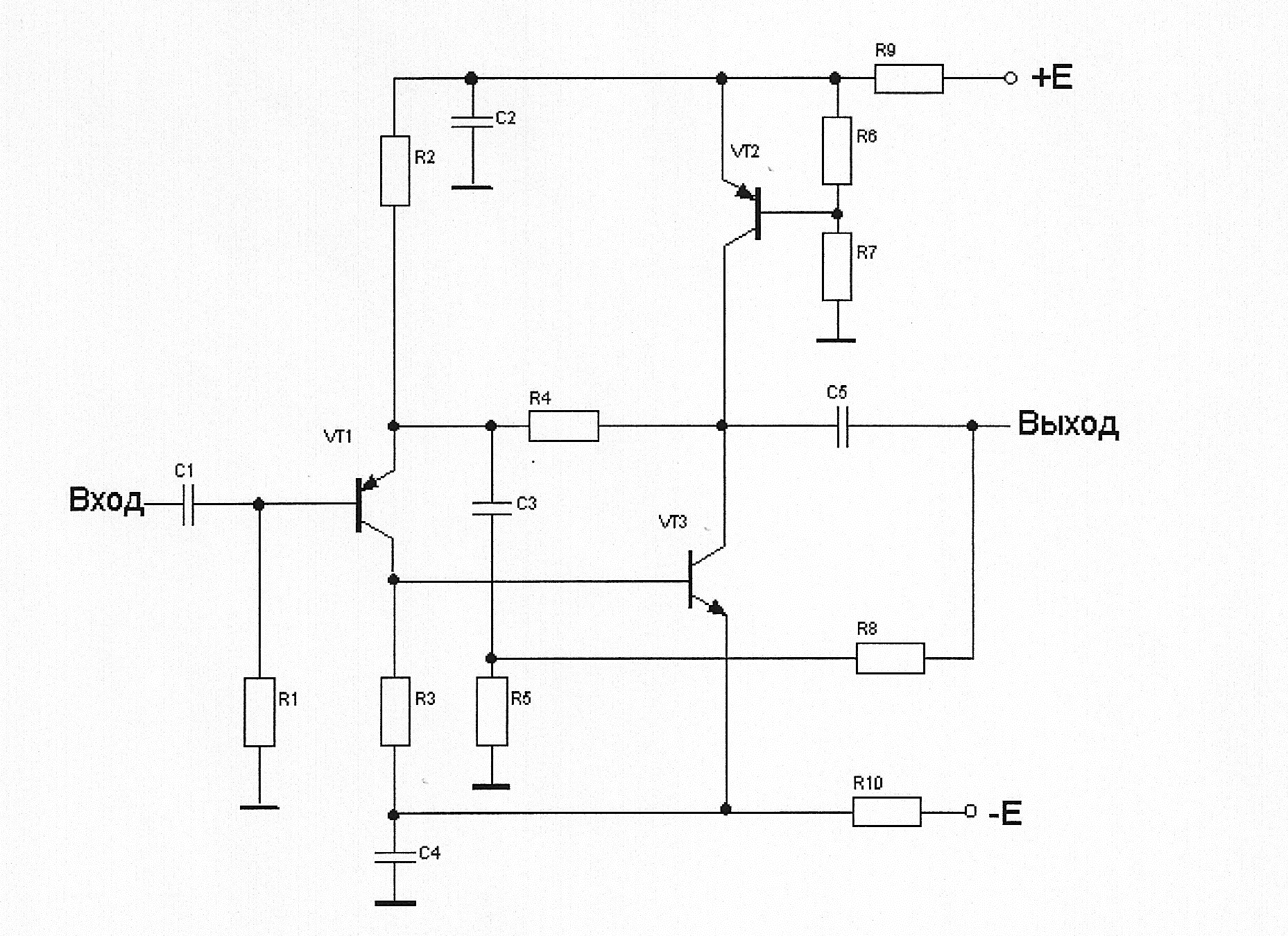

Трехкаскадные усилители:

Рисунок 25. Трехкаскадные усилители:

а) усилители со структурой близкой к рис. 14(г)

б) усилитель с последовательным питанием

Рисунок 26. Усилитель с ПТ на входе

Рисунок 27. Усилитель на базе каскодной схемы с повышенным входным сопротивлением и структура Нортона.

Рисунок 28. Усилитель со скрещенным ОС

Рисунок 29. Усилитель с общей ОС.

Рисунок 30. Усилитель с Дифференциальным каскадом.

Рисунок 31. Усилитель с ПТ и общей ОС.

Рисунок 32. Усилитель с общей ОС

Рисунок 33. Усилитель с общей ОС

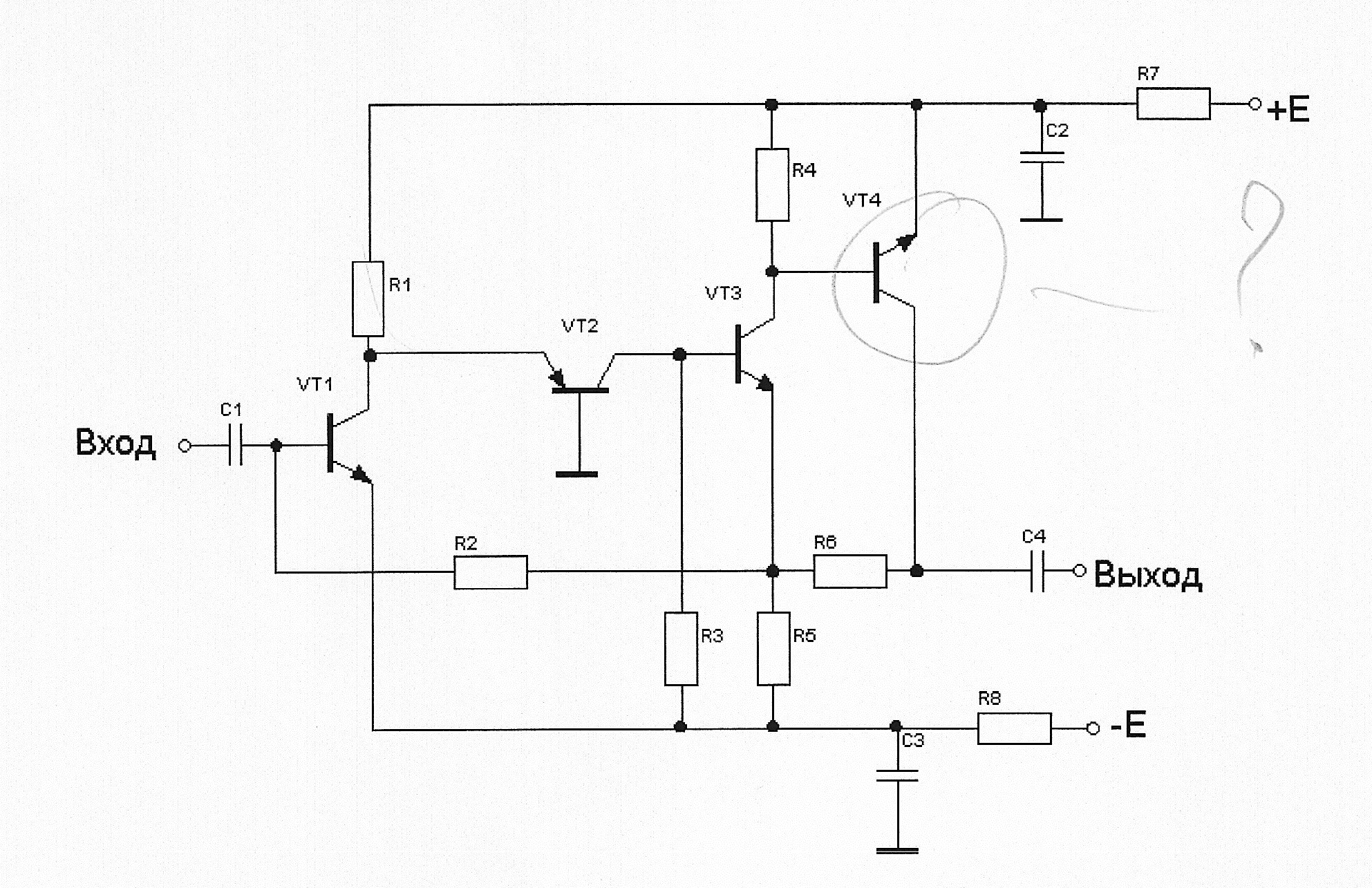

Четырехкаскадные усилители:

Рисунок 34. Усилитель с общей ОС и структурой близкой к рис. 14(д)

Рисунок 35. Усилитель с малым входным сопротивлением

Рисунок 36. усилитель на структурах ОЭ-ОК

Специальные усилители:

Рисунок 37. а) согласующий усилитель

б) нормирующий усилитель

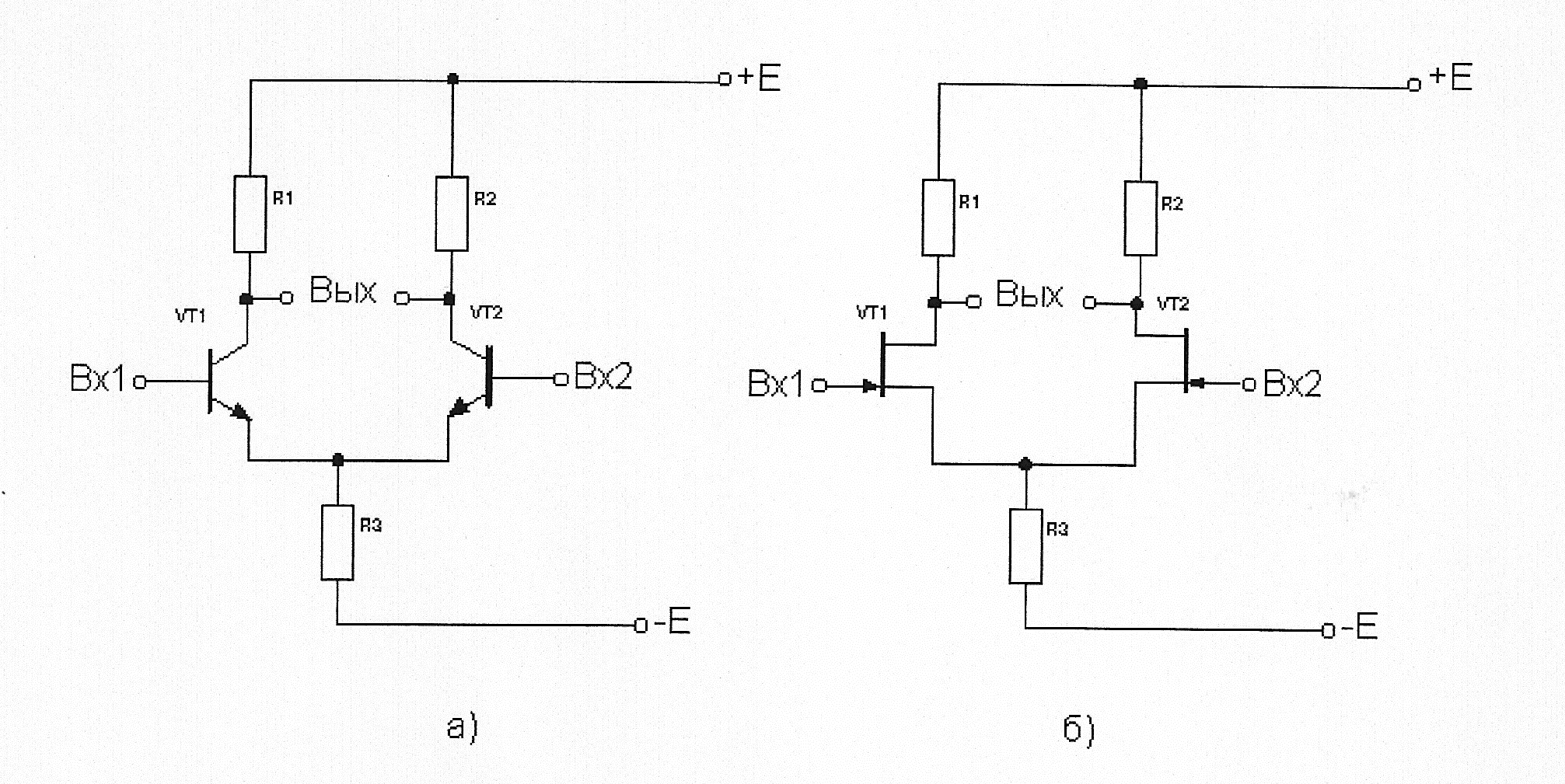

Дифференциальные каскады (ДК):

Рисунок 38. Простейшие ДК:

а) на БТ

б) на ПТ

Рисунок 39. ДК на супербэта транзисторах

Рисунок 40. ДК:

а) с активной нагрузкой (VT2) в виде токового зеркала

б) с суммированием выходных напряжений левого и правого плеча на общем выходе

Рисунок 41. ДК на ПТ:

а) каскодное соединение ОИ-ОЭ с динамической нагрузкой на VT4

б) на МОП-транзисторах

Рисунок 42. ДК:

а) с инвертором на VT2 и VT3 для широкополосных усилителей

б) двухкаскадный ДК с одинаковой крутизной переднего и заднего фронта в режиме большого сигнала