- •Оглавление

- •3.3. Математические модели надежности аппаратуры ис 36

- •4.Расчет аппаратурной надежности ис на этапе проектирования 45

- •4.5. Расчет надежности ремонтируемых систем 57

- •5. Методы обеспечения контроля и диагностики аппаратуры ис 66

- •1. Основные понятия, термины и определения

- •1.1. Система и ее элементы

- •1.2. Понятия надежности и отказа системы (элемента)

- •1.3 Основные определения в области качества и надежности программного обеспечения (по) ис

- •1.4. Основные определения в области надежности подсистемы человек - оператор ис

- •1.5. Проблема стандартизации в области надежности и качества

- •2. Факторы, влияющие на надежность информационных систем

- •2.1. Общая характеристика факторов, влияющих на надежность ис

- •2.2. Влияние внешних воздействующих факторов при эксплуатации ис

- •2.3. Общие принципы обеспечения надежности сложных технических систем

- •Показатели надежности аппаратуры ис и используемые модели надежности

- •Основные показатели надежности невосстанавливаемых объектов

- •3.1.1. Вероятность безотказной работы

- •3.1.2. Вероятность отказа

- •3.1.3. Средняя наработка до отказа

- •3.1.4. Интенсивность отказов

- •3.2. Показатели надежности восстанавливаемых объектов

- •3.2.1. Показатели безотказности восстанавливаемых объектов

- •3.2.1.1. Параметр потока отказов

- •3.2.1.2. Средняя наработка на отказ объекта

- •3.2.2. Показатели ремонтопригодности

- •3.2.2.1. Вероятность восстановления

- •3.2.2.2. Среднее время восстановления

- •3.2.2.3. Интенсивность восстановления

- •3.2.3. Показатели долговечности

- •3.2.3. Комплексные показатели надежности

- •3.2.3.1. Коэффициент готовности

- •3.2.3.2. Коэффициент оперативной готовности

- •3.2.3.3. Коэффициент технического использования

- •3.2.3.4. Коэффициент сохранения эффективности

- •3.3. Математические модели надежности аппаратуры ис

- •3.3.1. Модели потоков событий

- •3.3.1.1. Простейший поток отказов

- •3.3.1.2. Потоки Эрланга

- •Законы распределения дискретных случайных величин

- •3.3.2.1. Биномиальный закон распределения числаn появления событияАвmнезависимых испытаниях.

- •3.3.2.2. Пуассоновское распределение появления n событий за время наблюдения t

- •3.3.3. Законы распределения непрерывных случайных величин

- •3.3.3.1. Экспоненциальное распределение

- •3.3.3.2. Нормальное распределение

- •3.3.3.3. Гамма - распределение

- •3.3.4. Марковские процессы

- •Расчет аппаратурной надежности ис на этапе проектирования

- •4.1. Составление логических схем

- •4.2. Расчет надежности нерезервированной невосстанавливаемой системы

- •4.3. Учет влияния режимов работы элементов на надежность систем

- •4.4. Расчет надежности невосстанавливаемых резервированных систем

- •4.4.1. Резервирование с целой кратностьюk с постоянно включенным резервом или нагруженное резервирование замещением с абсолютно надежными переключателями

- •4.4.1.1. Общее резервирование

- •4.4.1.2 Раздельное резервирование

- •4.4.1.3. Общее резервирование с дробной кратностью

- •4.4.2. Резервирование замещением ненагруженное и облегченное с абсолютно надёжными переключателями.

- •4.4.2.1.Общее ненагруженное резервирование замещением

- •4.4.2.2. Облегченное резервирование замещением

- •4.4.3. Резервирование с учетом надежности переключателей.

- •4.4.4. Скользящее резервирование

- •4.5. Расчет надежности ремонтируемых систем

- •4.5.1. Общая характеристика методов расчета надежности ремонтируемых систем

- •4.5.2. Вычисление функций готовности и простоя нерезервированных систем

- •4.5.3. Особенности расчета резервированных восстанавливаемых систем

- •4.5.3.1. Ненагруженное резервирование с восстановлением

- •4.5.3.2. Нагруженное резервирование замещением с восстановлением

- •4.5.4. Расчет надежности восстанавливаемых систем, перерывы, в работе которых в процессе эксплуатации недопустимы

- •4.5.5. Примеры решения типовых задач

- •5. Методы обеспечения контроля и диагностики аппаратуры ис

- •5.1. Контроль технического состояния ис в процессе эксплуатации

- •5.1.1. Основные определения в области контроля ис

- •Методы контроля аппаратуры ис

- •5.1.2.1. Оперативные методы контроля аппаратуры

- •5.1.2.2. Тестовый контроль аппаратуры

- •5.2. Основы диагностирования информационных систем

- •5.2.1. Метод построения квазиоптимальных тестов Шеннона – Фано

- •5.2.2. Организация тестирования персонального компьютера

- •6. Основы моделирования и расчета надежности программного обеспечения

- •6.1. Модель анализа надежности программных средств

- •6.2. Статистика ошибок по ис

- •6.3. Количественные характеристики надежности по ис

- •Модели надежности программного обеспечения

- •6.4.1. О возможности построения априорных мнп

- •6.4.2. Непрерывные эмпирические модели надежности по (нэмп)

- •6.4.3. Дискретные эмпирические модели надежности по (дэмп)

- •6.5. Способы обеспечения и повышения надежности по

- •6.5.1. Основы организации тестирования программ

- •6.5.1.1. Особенности тестирования « белого ящика»

- •6.5.1.2. Особенности функционального тестирования по ( методы тестирования «черного ящика»)

- •6.5.1.3. Организация процесса тестирования программного обеспечения

- •6.5.2. Способы повышения оперативной надежности по

- •7. Основы организации испытаний ис на надежность

- •7.1. Виды испытаний на надежность

- •7.2. Принципиальные особенности организации испытаний на надежность ис

- •Основы организации определительных испытаний на надежность

- •7.3.1. Точечные оценки показателей безотказности и ремонтопригодности

- •7.3.2. Оценка показателей надежности доверительным интервалом

- •7.3.2.1. Определение доверительного интервала для средней наработки на отказ

- •7.3.2.2. Определение доверительного интервала для вероятности безотказной работы по числу обнаруженных при испытаниях отказов

- •7.4. Основы организации контрольных испытаний

- •Основы надежности подсистемы «человек-оператор» ис

- •Основные понятия и определения

- •8.2. Влияние человека - оператора на надежность ис

- •Показатели безошибочности человека-оператора

- •8.2.2. Способы борьбы с ошибками оператора

- •Заключение

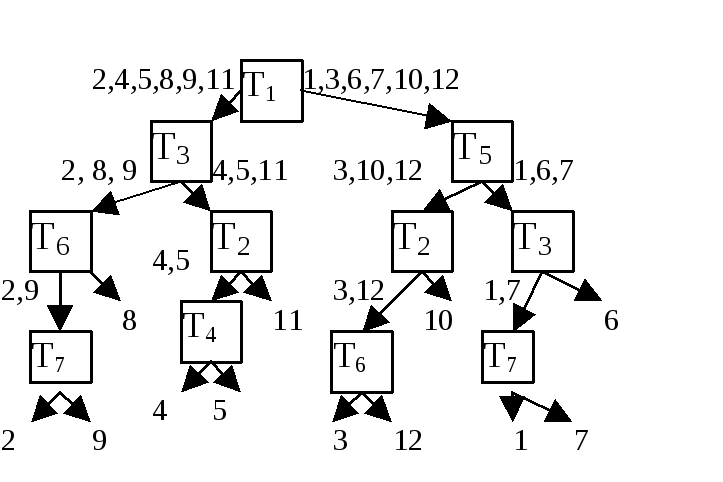

5.2.1. Метод построения квазиоптимальных тестов Шеннона – Фано

Допускается, что в диагностируемом объекте имеется одна неисправность

(

факт наличия неисправности установлен

методами контроля). Каждой из неисправностей

предписывается вероятность pi

того, что имеет место именно данная

i-

я неисправность. Согласно сделанному

допущению

![]() .

Вероятности могут быть найдены известными

методами расчета надежности ( см. п.

4.1). Первый тест выбирается так, чтобы

он разделил множество возможных

неисправностей объекта на два

подмножества с примерно равными

суммарными вероятностями входящих

неисправностей. Тест должен определить,

какому из двух подмножеств принадлежит

имеющаяся неисправность. Затем

подбирается тест, разделяющий таким же

образом на приблизительно равновероятные

подмножества то подмножество, в котором,

как было установлено, находится

неисправность и т. д. до достижения

достаточной определенности относительно

места расположения неисправности.

Дерево тестов, построенное по методу

Шеннона- Фано, показано на рис.5.2, где

Тi-

номер теста.

.

Вероятности могут быть найдены известными

методами расчета надежности ( см. п.

4.1). Первый тест выбирается так, чтобы

он разделил множество возможных

неисправностей объекта на два

подмножества с примерно равными

суммарными вероятностями входящих

неисправностей. Тест должен определить,

какому из двух подмножеств принадлежит

имеющаяся неисправность. Затем

подбирается тест, разделяющий таким же

образом на приблизительно равновероятные

подмножества то подмножество, в котором,

как было установлено, находится

неисправность и т. д. до достижения

достаточной определенности относительно

места расположения неисправности.

Дерево тестов, построенное по методу

Шеннона- Фано, показано на рис.5.2, где

Тi-

номер теста.

Рис. 5.2 Дерево тестов для системы, которая может иметь одно из 12 состояний неисправности.

Допустим, что все 12 неисправностей равновероятные. Выбираем в качестве первого теста Т1, который в зависимости от исхода делит всю область возможных неисправностей на два множества {2,4,5,8,9,11} и {1,3,6,7,10,12}. Допустим, что тест Т1 не обнаружил неисправность. Следовательно, неисправность входит в первое подмножество ( на рис 5.2 слева от теста указывается возможное подмножество состояний, отвечающих успешному прохождению теста). В качестве следующего теста выбирается тест Т3 и т.д. Принцип условного тестирования применим на любом иерархическом уровне аппаратуры.

Для диагностирования современных сложных ИС используются следующие подходы [5.1]:

разделение сложной системы на отдельные блоки ( функциональные) с выводом отдельных точек из тестируемой структуры или проектированием перемычек между частями схемы, которые технологически могут быть разомкнуты. Такой подход требует увеличения количества внешних выводов для тестируемых частей структуры;

построения схем, приспособленных к диагностическим процедурам. В структуру схем включаются средства встроенного аппаратного контроля, например, используется контроль по четности для средств хранения и передачи информации (см. п. 5.1.2.1) или вводятся компоненты интерфейса JTAG ( см.п.5.2.2);

построение вероятностных компактных тестов, например сигнатурного тестирования ( см. п. 5.1.2.2) с использованием генератора псевдослучайных чисел. Отметим, что генераторы псевдослучайных чисел и тестовые анализаторы могут быть получены не только аппаратными средствами, но и программными. Для примера покажем, как осуществляется процедура начального самотестирования в персональных компьютерах (ПК) семейства IBM PC.

5.2.2. Организация тестирования персонального компьютера

При включении питания, аппаратном сбросе от кнопки RESET или нажатии клавиш CTRL+ALT+ DEL процессор переходит к выполнению программы начального самотестирования POST, хранящейся в микросхеме ROM BIOS [3].

При прохождении каждой секции POST записывает ее код в диагностический регистр, который располагается на специальной диагностической плате, устанавливаемой в слот системной шины. Состояние каждого бита 8-битного диагностического регистра отражается на светоиндикаторах. По состоянию светоиндикаторов можно определить, на какой секции остановилась программа, и какая причину неисправности. Обычная последовательность шагов POST такова:

Тестирование регистров процессора.

Проверка контрольной суммы ROM BIOS.

Проверка и инициализация системного таймера.

После этого шага становится доступной звуковая диагностика.

Проверка и инициализация контроллеров DMA.

Проверка регенерации памяти.

Тестирование 64 КБ нижней памяти.

Загрузка векторов прерывания и стека в первый килобайт ОЗУ.

Инициализация видеоконтроллера – на экране появляется заставка Video BIOS обычно с указанием модели видеокарты и объемом установленной видеопамяти.

Теперь диагностические сообщения выводятся на экран. Далее

Тестирование полного объема ОЗУ.

Тестирование клавиатуры.

Тестирование CMOS- памяти и часов.

Инициализация COM и LPT- портов.

Инициализация и тест контроллера НГМД

Инициализация и тест контроллера НЖМД.

Сканирование области дополнительной памяти ROM BIOS.

Вызов Bootstrap – загрузка ядра ОС.

В персональном компьютере широко используется специальный диагностический интерфейс JTAG. Интерфейс является внешним, поскольку позволяет подключать внешнее тестирующее устройство- контроллер. Интерфейс включает всего 4 сигнала, образующие TAP- порт, через который тестируемое устройство подключается к тестирующему оборудованию. Задачей тестирующего оборудования является формирование тестовых последовательностей по программе тестирования, определенной разработчиком тестируемого устройства и сравнение полученных результатов с эталонами. При этом специальные ячейки тестирования как будто бы «врезаются» между реальными внешними выводами устройства и собственно цифровым устройством. ТАР – контроллер способен сканировать ячейки – управлять ими и считывать с них информацию. При включенном тестовом режиме ТАР – контроллер способен логически отсоединить сигналы от внешних выводов, после чего задавать входные воздействия и считывать результаты. Обычно тестирование осуществляется методами сигнатурного анализа. Интерфейсом JTAG снабжены многие стандартные устройства ПК. Например, центральный процессор во время спада сигнала RESET, если на определенном его входе удерживать низкий уровень, начинает выполнять внутренний тест BIST. По окончании самотестирования процессор начинает работу как после обычного сброса, регистр ЕАХ содержит сигнатуру результата самотестирования. Об успешном выполнении теста свидетельствует нулевое значение сигнатуры. Помимо интерфейса JTAG процессор имеет в своем составе специальные регистры отладки и тестирования. Регистры тестирования проверяют аппаратные средства процессора, в частности, работу встроенной кэш – памяти. Для процессоров Pentium и выше с помощью JTAG возможно наблюдение и изменение состояния регистров процессора.

––––––––––––––––––––––––––––––––––

Иыуду К.А. Надежность контроль и диагностика вычислительных машин и систем. - М.: Высшая школа, 1989

Каган Б.М., Мкрутмян И.Б. Основы эксплуатации ЭВМ. – М.: Энергоатомиздат, 1987

Гук М. Аппаратные средства IBMPС. Энциклопедия – СПб: Питер, 1998