- •Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

- •Исследование влияния параметров элементов схемы на работу базового логического элемента 2и-не ттлш серии 1531

- •Москва, 2013

- •1.Анализ схемы заданного блэ

- •1.1Логические операции и таблица истинности

- •1.2 Структурная схема

- •1.3. Принципиальная схема

- •1.4 Постановка задачи исследования базового логического элемента

- •2. Анализ работы базового логического элемента в статическом и динамическом режимах

- •3.2. Влияние изменения r1,r2.R3,r4,r12,c1 на величины ,

- •3.3. Влияние изменения r1,r2,r3,r4,r12,c1 на величины

- •3.4.Анализ результатов и выбор оптимальных величин для r1,r2,r3,r4,r12,c1.

1.Анализ схемы заданного блэ

1.1Логические операции и таблица истинности

Данный базовый логический элемент (БЛЭ) выполняет логическую операцию 2И-НЕ. Он имеет два входа: X1, X2 и один выход: Y1.Таблица истинности представлена в таблице 1.

Таблица.1.

-

Вход1

Вход2

Выход

X1

X2

Y1

0

0

1

0

1

1

1

0

1

1

1

0

1.2 Структурная схема

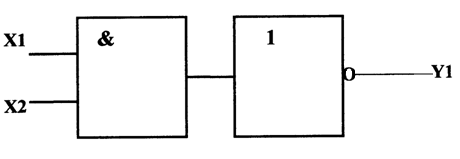

Структурная схема состоит из элемента 2И и инвертора. Эта схема представлена на рисунке 2.

Рисунок 2- Структурная схема базового логического элемента

1.3. Принципиальная схема

Принципиальная

схема базового логического элемента

2И-НЕ ТТЛШ, построенная в программе

схемотехнического моделирования

MicroCap

9[1], приведена на рисунке 3.

Рисунок 3 - Принципиальная схема базового логического элемента

Схемы ТТЛШ [2,3,4] являются разновидностью схем ТТЛ и включают в себя диоды Шоттки. Они имеют повышенное быстродействие ввиду того, что параллельно переходам база-коллектор транзисторов включен диод Шоттки, используемый в качестве ограничивающего диода. Поскольку такой диод имеет меньшее прямое падение напряжения ( вместо 0.7 В для кремниевых у него 0.2 – 0.3 В), чем переход база-коллектор биполярного транзистора, то излишний управляющий ток базы при открывании транзистора отводится через диод, что предотвращает вхождение транзистора в режим насыщения. Поэтому в области базы не накапливаются избыточные носители заряда. Базовый элемент 2И-НЕ на транзисторах Шоттки ( в интегральном исполнении транзистор и диод Шоттки составляют единую структуру) показан на рис. 6. Поскольку в программе Micro Cap 9 [1] отсутствует транзистор Шоттки, то на данной схеме он представлен как биполярный транзистор, параллельно коллекторному переходу которого включен диод Шоттки.

Логическую операцию 2И выполняют диоды VD3 и VD5 и резистор R1. Сложный инвертор собран на транзисторах VT2 – VT6 с соответствующими диодами Шоттки VD8, VD11 – VD13. Транзистор VT3 является обычным биполярным транзистором, поскольку в процессе работы схемы он не входит в насыщение. Транзистор VT5 с диодом VD13 и резисторами R9 и R11 представляет собой корректирующую цепочку, которая сглаживает передаточную характеристику схемы при переключении схемы с логической единицы на логический ноль. В этом случае схема более устойчива к помехам в интервале входных напряжений приблизительно от 0.8 В до 1 В. Транзисторы VT2 и VT3 с диодом VD8 и резистором R4 представляют собой схему Дарлингтона, которая удваивает значение коэффициента усиления базового тока, что обеспечивает большие токи в нагрузке и повышает быстродействие элемента. Цепочка R12 и C1 представляют собой комплексную нагрузку следующего каскада. Делитель напряжения R6, R12 представляет входное напряжение следующего каскада. Источник V2 служит для запирания входа 2, резисторы R8 и R5 представляют собой внутренние сопротивления источников V1 и V3. Генератор V1 формирует трапецеидальные импульсы с периодом повторения порядка 64 нс. На транзисторе VТ1 собран дополнительный усилитель. Дополнительные диоды VD4 и VD6 емкостными токами своих переходов ускоряют процесс переключения транзистора VТ1. Коллектор транзистора VТ4 дополнительно соединен с базой транзистора VТ3 через диод VD9 и резистор R7; это способствует уменьшению времени перезарядки паразитных емкостей нагрузки.

Работает схема следующим образом[2]. При поступлении на оба входа сигналов высокого уровня (U1вх) входные диоды VD3 и VD5 закрываются. Ток от источника V3 протекает через резистор R1, поступает в базу транзистора VТ1 и открывает его. Ток его эмиттера создает на резисторе R10 падение напряжения, которое открывает фазоинверсный каскад на VТ4. Далее открывается транзистор VТ5, и падением напряжения на резисторе R9 и VТ5 открывается транзистор VТ6. Транзисторы VТ2 и VТ3 (составной транзистор) закрываются, т.к. потенциал коллектора VТ4 уменьшается и, соответственно, падение напряжения на R3 увеличивается. В результате на выходе схемы устанавливается напряжение низкого уровня(U0вых).

При появлении на одном из входов (например, на входе 1) сигнала низкого уровня (U0вх) открывается диод VD3 и через него потечет ток I0вх. Транзисторы VТ1, VТ4 и VТ6 закроются, так как потенциал базы VТ1 резко упадет и падение напряжения на R10 и VТ5 близко к 0. Транзисторы VТ2 и VТ3 откроются, так как потенциал коллектора VТ4 и падение напряжения на R7 возрастут. На выходе схемы установится напряжение высокого уровня (U1вых). Для защиты входов от выбросов напряжения отрицательной полярности в структуру схемы встроены диоды VD1 и VD2. В данной схеме все транзисторы, кроме VТ3, имеют фиксирующие диоды Шоттки. В качестве VТ3 используется обычный транзистор, так как на его коллекторном переходе всегда сохраняется обратное смещение, то есть он не входит в насыщение.

Потенциалы в узлах схемы показаны на рисунке 4.