- •Минобрнауки россии

- •I sbn х-хххх-хххх-х ©сПбГэту «лэти», 2011 Техническое задание

- •1. Постановка задачи

- •1.1. Имитатор подвижного сигнала

- •1.2. Микропроцессор 1821вм85

- •2. Выбор и обоснование структурной схемы имитатора

- •2.1. Структурная схема имитатора

- •2.2. Расчет основных параметров имитатора

- •3. Выбор элементов принципиальной схемы

- •3.1. Выбор элементной базы

- •3.2. Синтез счетчика с тремя модулями пересчета

- •3.3. Синтез счетчика по mod м0

- •3.4. Синтез счетчика по mod м1i

- •3.5. Синтез счетчика по mod Мj

- •3.6. Контроллер клавиатуры

- •3.7. Приемопередатчик, обслуживающий внешние устройства схемы

- •3.8. Дешифратор адресов

- •3.9. Организация памяти

- •3.10. Дисплей

- •4. Создание макроэлементов в символьном редакторе

- •5. Инициализация микроконтроллера

- •6. Выполнение принципиальной схемы

- •7. Перечень элементов принципиальной схемы

- •Список литературы

- •Минобрнауки россии

- •«Санкт-Петербургский государственный электротехнический университет

- •(СПбГэту)

- •Санкт-Петербург

- •201_ Г. Оглавление

- •Имитатор сигналов, отраженных от движущейся цели на бис Altera

- •197376, Санкт-Петербург, ул. Проф. Попова, д. 5

3.3. Синтез счетчика по mod м0

В зависимости от выбранного при расчетах значения М0 = 5 или 10 могут быть построены 2 схемы.

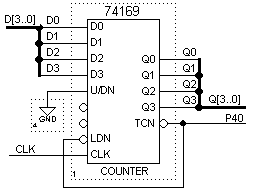

Счетчик по mod 5 (рис. 3.9, а) строится на макроэлементе 74169 с записью в него числа d = 4 (рис. 3.10). Граничная частота такого счетчика ограни-

|

|

|

|

а |

б |

|

Рис. 3.9. Делители на M0= 5 (а) иM0= 10 (б) на МЭ фирмы Altera | |

|

|

|

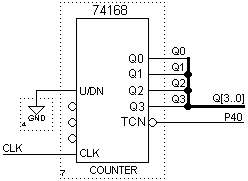

Рис. 3.10. Временные диаграммы работы делителя на M0= 5 |

Таблица 3.10

Результаты временного анализа схемы рис. 3.9. а

|

Сигналы |

Выход | |||||

|

Вход |

|

Q0 |

Q1 |

Q2 |

Q3 |

out |

|

CLK, нс |

7.4 |

2.8 |

2.8 |

2.8 |

2.8 |

7.4 |

|

|

|

Рис. 3.11. Временные диаграммы работы делителя на M0= 10 |

Таблица 3.11

Результаты временного анализа схемы рис. 3.9, б

|

Сигнал |

Выход | |||||

|

Вход |

|

Q0 |

Q1 |

Q2 |

Q3 |

out |

|

CLK, нс |

7.4 |

2.8 |

2.8 |

2.8 |

2.8 |

7.4 |

чивается

только задержкой сигнала

![]() = 0:

t

з

= t

зP4

= 7.6 нс;

(fmax

≤ 131 МГц). Счетчик по mod

10 (рис. 3.9, б)

строится на макроэлементе 74168, который

является счетчиком по mod 10, поэтому

загрузка отсутствует (рис. 3.11). Граничная

частота определяется частотой работы

самого счетчика и равна 175 МГц.

В табл. 3.10 и 3.11 приведены значения

задержек сигнала в схемах счетчиков по

mod

М0.

= 0:

t

з

= t

зP4

= 7.6 нс;

(fmax

≤ 131 МГц). Счетчик по mod

10 (рис. 3.9, б)

строится на макроэлементе 74168, который

является счетчиком по mod 10, поэтому

загрузка отсутствует (рис. 3.11). Граничная

частота определяется частотой работы

самого счетчика и равна 175 МГц.

В табл. 3.10 и 3.11 приведены значения

задержек сигнала в схемах счетчиков по

mod

М0.

3.4. Синтез счетчика по mod м1i

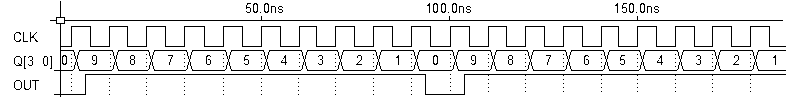

Счетчик по mod M1i имеется как в канале зондирующего сигнала G, так и в канале отраженного (подвижного) сигнала Gv. Эти счетчики используются в качестве делителей частоты на число Mi = Tif0/M0 при i = 1, 2, 3, 4 (рис. 2.1) и могут быть выполнены на 16-разрядном двоичном счетчике с параллельной синхронной загрузкой данных (расчетные значения Mi, как правило, представимы 16-разрядным двоичным кодом).

Счетчик по mod

M1i

на МЭ lpm

counter.

Для построения

делителя на МЭ фирмы Altera

используются счетчики из папки lpm:

16-разрядный счетчик lpm_counter

с синхронной загрузкой данных (в счетчике

задаются входные сигналы cin,

clk_en,

cnt_en,

sload,

разрядность width

= 16 и направление работы (режим вычитания)

lpm

direction

= down,

а также выходной сигнал переноса cout.

На рис. 3.12 показана схема 16-разрядного

счетчика. Модуль пересчета Mi

этого счетчика определяется соотношением

Mi

=

![]() +

1, т. е. он

задается параллельной записью в счетчик

числа

+

1, т. е. он

задается параллельной записью в счетчик

числа

![]() =Mi

– 1. Число

=Mi

– 1. Число

![]() – двухбайтовое, содержащее мдадший

байтdLT

и старший байт dMT

(M

– most,

L

– least),

хранящиеся в памяти в соседних ячейках.

Оба байта должны быть записаны в регистры

памяти 74377b. По команде OUT port_dLT вырабатывается

системный сигнал управления

– двухбайтовое, содержащее мдадший

байтdLT

и старший байт dMT

(M

– most,

L

– least),

хранящиеся в памяти в соседних ячейках.

Оба байта должны быть записаны в регистры

памяти 74377b. По команде OUT port_dLT вырабатывается

системный сигнал управления

![]() = 0, а дешифратор адресных сигналов

внешних устройств вырабатывает сигнал

port_dLT

= 0, который разрешает запись младшего

байта D[7..0]

в регистр; запись производится

положтиельным перепадом сигнала

= 0, а дешифратор адресных сигналов

внешних устройств вырабатывает сигнал

port_dLT

= 0, который разрешает запись младшего

байта D[7..0]

в регистр; запись производится

положтиельным перепадом сигнала

![]() .Аналогичным

образом по команде OUT port_dMT

записывается старший байт данных

D[15..0]

в регистр 74377b.

.Аналогичным

образом по команде OUT port_dMT

записывается старший байт данных

D[15..0]

в регистр 74377b.

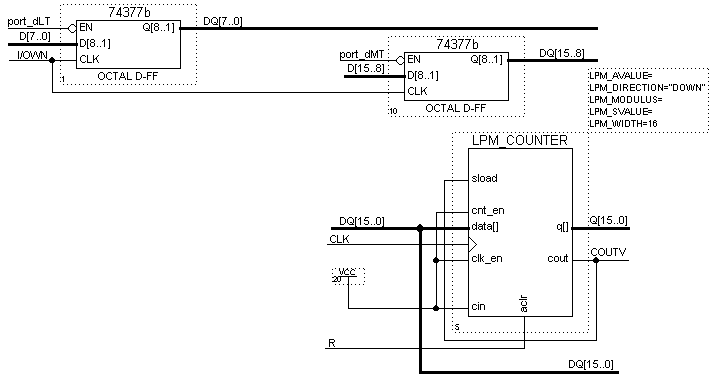

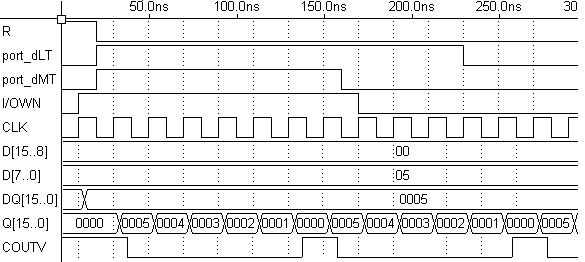

Временные диаграммы работы счетчика представлены на рис. 3.13. После загрузки младшего байта D[7..0] = 05 и старшего байта D[15..0] = 00, которая разрешается сигналом COUT = 1, возникающем в нулевом состоянии счетчика, счетчик начинает считать до нуля, после чего снова произойдет загрузка. На рис. 3.13 запись младшего и старшего байта осуществляется одновременно, реально же запись младшего и старшего байта происходит в разные моменты времени.

|

|

|

Рис. 3.12. Схема 16-разрядного делителя на M1i |

|

|

|

Рис. 3.13. Временные диаграммы 16-разрядного делителя |

Схема 16-разрядного делителя частоты используется как в неподвижном канале (на тактовый вход подается сигнал с выхода делителя на M0 P40), так и в подвижном канале (на тактовый вход подается сигнал с выхода делителя на Mv P4v). Выходные сигналы счетчиков COUT являются сигналами G и Gv.