4788

.pdfМинистерство образования и науки российской федерации Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«Воронежская государственная лесотехническая академия»

П.В. Мурзинов Ю.В. Мурзинов

МИКРОПРОЦЕССОРНАЯ ТЕХНИКА

Лабораторный практикум

Воронеж 2012

2

УДК 004.3 М91

Печатается по решению учебно-методического совета ФГБОУ ВПО «ВГЛТА» (протокол № 3 от 23 декабря 2011 г.)

Рецензенты: кафедра технологии машиностроения ВГТУ, первый заместитель ген. директора ОАО ХК

«Мебель Черноземья» д-р техн. наук, проф. А.Д. Данилов

Научный редактор д-р техн. наук, проф. B.C. Петровский

Мурзинов, П. В.

М91 Микропроцессорная техника [Текст] : лабораторный практикум / П. В. Мурзинов, Ю. В. Мурзинов ; М-во образования и науки РФ, ФГБОУ ВПО «ВГЛТА». – Воронеж, 2012. – 40 с.

ISBN 978-5-7994-0481-9 (в обл.)

В лабораторном практикуме представлены описание и порядок исследования типовых логических элементов и узлов микроЭВМ, а также комбинационных и последовательных устройств.

Лабораторный практикум предназначен для бакалавров по направлениям подготовки 220700 – Автоматизация технологических процессов и производств, 190700 – Технология транспортных процессов.

УДК 004.3

© Мурзинов П.В., Мурзинов Ю.В., 2012

ISBN 978-5-7994-0481-9 © ФГБОУ ВПО «Воронежская государственная лесотехническая академия», 2012

3

Введение

В настоящее время микропроцессорная техника получила широкое применение в системах управления технологическим и контрольноиспытательным оборудованием, транспортными средствами, космическими аппаратами, бытовыми приборами и т.д. Малые размеры, масса и энергоѐмкость микропроцессоров позволяют встраивать их непосредственно в объект управления. На базе микропроцессоров создаются различные типы микроЭВМ, контроллеров, программаторов и других устройств автоматики и вычислительной техники.

Для того чтобы наиболее точно разобраться в процессе функционирования микропроцессорных устройств, необходимо знать принципы работы их составных частей: логических элементов, триггеров, регистров, счетчиков, сумматоров, мультиплексоров, дешифраторов, демультиплексоров и т.д.

В данном лабораторном практикуме представлены описание и порядок исследования типовых логических элементов и узлов микроЭВМ, а также комбинационных и последовательностных устройств. Исследования проводятся в рамках лабораторных занятий по курсу «Микропроцессорная техника» при использовании универсального стенда ОАВТ.

4

ОПИСАНИЕ ЛАБОРАТОРНОГО СТЕНДА

Универсальный стенд ОАВТ предназначен для выполнения нескольких лабораторных работ. Он содержит блок питания, блок управления и ввода информации, блок индикации. Стенд имеет разъѐм X1, в который вставляются сменные платы, зависящие от содержания выполняемой работы. Принципиальная схема блоков индикации, управления и ввода информации представлена на рис. 1.

На передней (наклонной) панели стенда установлены тумблеры (SA1 – SA5) и кнопки (SB1 – SB3) ввода информации и задания режимов работы исследуемых устройств. Выводы всех тумблеров и кнопок, кроме SB1, подключены непосредственно к контактам разъѐма X1.

Переключатели SA1 – SA4, SB2 и SB3 предназначены для подачи логических сигналов с уровнями 0 (соответствующий вывод замкнут на общий провод) или 1 (вывод – на + 5 В). Тумблер SA5 подключается всеми своими выводами к разъѐму и поэтому может использоваться в качестве переключателя «двух сигналов в одну линию» или наоборот, «одного сигнала на два направления». Кнопка SB1 подключена к схеме зашиты от «дребезга» на триггере (микросхема D1.1). С помощью этой кнопки на выходе триггера (27 контакт разъѐма X1) формируется одиночный импульс с крутыми фронтами, необходимый для нормальной работы исследуемых триггеров, регистров и счѐтчиков. При нажатии SB1 на 27 контакте появляется логический 0, а при отпускании – логическая 1. Этот блок в дальнейшем на схемах обозначается как формирователь одиночного импульса (F).

На передней панели блока установлен светодиодный дисплей для индикации режимов работы, а также входной и выходной информации исследуемого устройства. Дисплей состоит из девяти светодиодов HL1 – HL9, позволяющих индицировать в 9 разрядах уровни логической 1 (светодиоды светятся) и логического 0 (не светятся), и семисегментного индикатора HG1 для индикации числа в десятичном или шестнадцатеричном кодах.

Индикатор HG1 подключается к исследуемой схеме через дешифратор на интегральной микросхеме D5, преобразующий четырѐхразрядный двоичный код (на контактах 11 – 14 разъѐма X1) в семисегментный код индикатора HG1. При низком уровне напряжения на входе 5 микросхемы D5

5

(контакт 15 разъѐма X1) на индикаторе HG1 индицируется число в десятичном коде, при высоком уровне – в шестнадцатеричном. Светодиоды HL1 – HL9 подключаются к элементам схемы через инверторы D3.1 – D3.4, D3.6, D4.1 – D4.4. В дальнейшем устройство, содержащее дешифратор D5, индикатор HG1, инверторы с подключенными к ним светодиодами HL1 – HL9, обозначается как блок индикации (БИ).

Помимо описанных устройств ввода и вывода информации стенд содержит следующие вспомогательные устройства:

– инвертор на элементе D4.5, используемый при работе с платами П3,

П4;

–генератор прямоугольных импульсов на элементах D2.1 – D2.3 с выходом 30 на Х1. Частота колебаний генератора в пределах 2...10 кГц;

–инвертор на элементе D2.6, используемый при работе с платой П6. Тумблеры и кнопки, формирователь F, генератор прямоугольных

импульсов, инверторы D2.6 и D4.5 образуют блок управления (БУ).

6

Рис. 1. Схема блоков индикации, управления и ввода информации

7

ЛАБОРАТОРНАЯ РАБОТА № 1

Исследование логических элементов

Цель работы – исследование поведения основных логических элементов при подаче на них двоичных потенциальных сигналов.

Краткие теоретические сведения Логический элемент – это устройство, к входу которого подводятся

конкретные значения логических переменных, а на выходе получается решение определенной элементарной (логической) функции. Основными логическими функциями являются: инверсия, конъюнкция, дизъюнкция, неравнозначность.

Инверсия (логическое отрицание, «НЕ») переменной X есть логическая функция Y, которая истинна только тогда, когда ложна X, и наоборот.

Логическое уравнение для инверсии имеет следующий вид:

Y X .

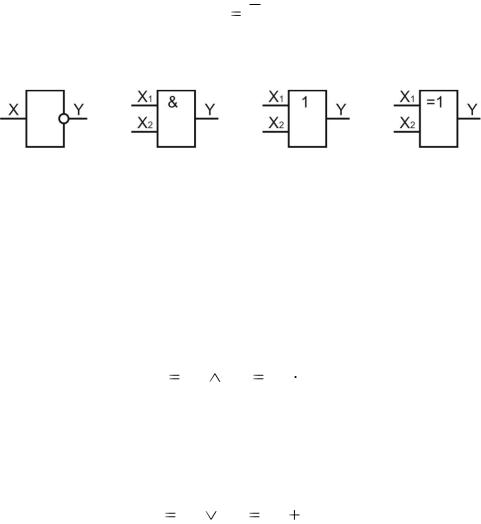

Графическое обозначение логического элемента реализующего функцию логического отрицания представлено на рис. 2.

а) |

б) |

в) |

г) |

|

Рис. 2. Логические элементы: а) «НЕ»; б) «И»; в) «ИЛИ»; |

|

|||

г) «исключающее ИЛИ» |

|

|

||

Конъюнкция (логическое умножение, «И») двух переменных X1 |

и X2 |

|||

есть логическая функция Y, которая истинна только тогда, когда |

||||

одновременно истинны входные переменные. |

|

|

||

Логическое уравнение для конъюнкции имеет следующий вид: |

|

|||

Y |

X1 |

X 2 X1 X 2 . |

|

|

Дизъюнкция (логическая сложение, «ИЛИ») двух переменных Х1 |

и Х2 |

|||

есть логическая функция Y, которая истинна, когда истинна хотя бы одна из входных переменных.

Логическое уравнение для дизъюнкции имеет следующий вид:

Y X1 X 2 X1 X 2 .

8

Неравнозначность (сложение по модулю 2, «исключающее ИЛИ») двух переменных Х1 и Х2 есть логическая функция Y, которая истинна, когда значения входных переменных различны.

Логическое уравнение для неравнозначности имеет следующий вид:

Y X1 X 2 .

Графическое обозначение логических элементов реализующих функции логического умножения, логического сложения и сложения по модулю 2 представлено на рис. 2.

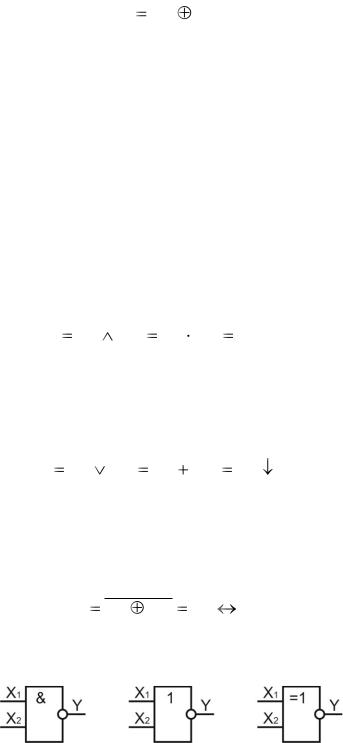

Если объединить инверсию с одной из трѐх других функций, то получатся следующие логические функции: отрицание конъюнкции, отрицание дизъюнкции, равнозначность.

|

Отрицание конъюнкции (функция Шеффера, «И-НЕ») двух переменных |

|||||||||||

X1 |

и X2 есть логическая функция Y, которая ложна только тогда, когда |

|||||||||||

одновременно истинны входные переменные. |

|

|

||||||||||

|

Логическое уравнение для отрицания конъюнкции имеет следующий |

|||||||||||

вид: |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

X1 | X 2 . |

|

|

Y X1 |

X 2 |

|

|

X1 X 2 |

|||||||

|

Отрицание дизъюнкции (функция Пирса, «ИЛИ-НЕ») двух переменных |

|||||||||||

Х1 |

и Х2 есть логическая функция Y, которая ложна, когда истинна хотя бы |

|||||||||||

одна из входных переменных. |

|

|

|

|

|

|

|

|

|

|||

|

Логическое уравнение для отрицания дизъюнкции имеет следующий вид |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|||

|

Y X1 |

X 2 |

|

X1 X 2 |

X1 |

X 2 . |

||||||

|

Равнозначность (эквивалентность, «исключающее ИЛИ-НЕ») двух |

|||||||||||

переменных Х1 и Х2 есть логическая функция |

Y, которая истинна, когда |

|||||||||||

значения входных переменных одинаковы.

Логическое уравнение для равнозначности имеет следующий вид:

Y X1 X 2 X1 X 2 .

Графическое обозначение логических элементов, реализующих функции Шеффера, Пирса и эквивалентности, представлено на рис. 3.

а) б) в)

Рис. 3. Логические элементы: а) «И-НЕ»; б) «ИЛИ-НЕ»; в) «исключающее ИЛИ-НЕ»

9

Описание сменной платы П1 Схема платы П1 приведена на рис. 4. Плата выделена пунктиром, ключи

и индикаторы находятся на стенде. В качестве D1 используется интегральная микросхема К155ЛЕ1, в качестве элемента D2 – К155ЛА3, в качестве элемента

D3 – К155ЛП5.

Рис. 4. Схема платы П1 и ее подключения к основному блоку

10

Порядок выполнения работы

1. Выделить из рис. 4 и изобразить отдельно схему реализации логической функции Y X1 X 2 . Экспериментально получить таблицу истинности функции (карта I-1).

2. Выделить из рис. 4 и изобразить отдельно схему реализации логической функции Y X1 X 2 . Экспериментально получить таблицу истинности функции (карта I-2).

3. Выделить из рис. 4 и изобразить отдельно схему реализации логической функции Y X1 X 2 . Экспериментально получить таблицу истинности функции (карта I-3).

4. Выделить из рис. 4 и изобразить отдельно схему реализации логической функции Y X1 X2 . Экспериментально получить таблицу истинности функции (карта I-4).

5. Выделить из рис. 4 и изобразить отдельно схему реализации логической функции Y X1 X 2 . Экспериментально получить таблицу истинности функции. Синтезировать функцию на элементах «И-НЕ» и изобразить полученную схему (карта I-5).

6. Выделить из рис. 4 и изобразить отдельно схему реализации логической функции Y X1 X 2 . Экспериментально получить таблицу истинности функции (карта I-6).

7.Исследовать трѐхразрядное устройство проверки на нечетность. Источниками сигнала являются тумблеры SA1, SA2, SA3. Индикатором нечетного количества истинных бит в слове является светодиод HL1. Выделить из рис. 4 и изобразить схему трѐхразрядного устройства. Получить экспериментально таблицу истинности, по которой составить уравнение в СДНФ. Составить уравнение в СДНФ непосредственно по виду схемы. Сравнить оба полученных уравнения (карта I-7).

8.Исследовать устройство побитового сравнения двух двухразрядных чисел Х1Х0 и Z1Z0. Число X1Х0 задаѐтся тумблерами SA1, SA4, a число Z1Z0

–SA2, SA5. Результат сравнения наблюдать на светодиоде HL1. Два числа равны, если X1 = Z1 и X0 = Z0. Получить экспериментально таблицу истинности, по которой составить логическое уравнение условия равенства