4788

.pdf11

чисел. По уравнению синтезировать устройство сравнения на элементах «И- НЕ». Выделить из рис. 4 и изобразить схему сравнения на элементах D1, D3. Составить уравнение функционирования схемы и, преобразовав его в СДНФ, сравнить с предыдущим (карта I-8).

9. Исследовать одноразрядный полусумматор, используя ключи SA1, SA2 в качестве булевских переменных X1, Х2, светодиод HL1 для индикации суммы, a HL2 – переноса. Выделить из рис. 4 и изобразить часть схемы, реализующую полусумматор. Получить экспериментально таблицу истинности, по которой составить уравнение в СДНФ. Составить уравнение в СДНФ непосредственно по виду схемы. Сравнить оба полученных уравнения. Синтезировать полусумматор на элементах «И-НЕ» (карта I-9).

Отчѐт о работе В отчѐте должны содержаться:

1.Схема (выделенная из рис. 4) и экспериментальная таблица истинности функции «И-НЕ».

2.Схема (выделенная из рис. 4) и экспериментальная таблица истинности функции «И».

3.Схема (выделенная из рис. 4) и экспериментальная таблица истинности функции «ИЛИ-НЕ».

4.Схема (выделенная из рис. 4) и экспериментальная таблица истинности функции «ИЛИ».

5.Схема (выделенная из рис. 4) и экспериментальная таблица истинности функции «исключающее ИЛИ».

6.Схема функции «исключающее ИЛИ» синтезированная на элементах

«И-НЕ».

7.Схема (выделенная из рис. 4) и экспериментальная таблица истинности функции «исключающее ИЛИ-НЕ».

8.Схема (выделенная из рис. 4) и экспериментальная таблица истинности трѐхразрядного устройства проверки на нечетность.

9.Уравнения в СДНФ трѐхразрядного устройства проверки на нечетность, построенные по таблице истинности и схеме.

10.Схема (выделенная из рис. 4) и экспериментальная таблица истинности устройства побитового сравнения двух двухразрядных чисел.

12

11.Уравнения в СДНФ устройства побитового сравнения двух двухразрядных чисел, построенные по таблице истинности и схеме.

12.Схема устройства побитового сравнения двух двухразрядных чисел, синтезированная на элементах «И-НЕ» по уравнению равенства двух чисел.

13.Схема (выделенная из рис. 4) и экспериментальная таблица истинности одноразрядного полусумматора.

14.Уравнения в СДНФ одноразрядного полусумматора, построенные по таблице истинности и схеме.

15.Схема одноразрядного полусумматора на элементах «И-НЕ».

Вопросы для самоконтроля 1. Определения алгебры логики: булевские переменные, логическая

функция.

2.Логический элемент: таблицы истинности, уравнения основных логических функций, графические обозначения элементов.

3.Основные законы алгебры логики.

4.ДНФ, КНФ, СДНФ и СКНФ.

5.Одноразрядный полусумматор (определение). Функционирование одноразрядного полусумматора с позиций двоичной арифметики.

6.Каковы различия принципов работы органов управления стенда?

ЛАБОРАТОРНАЯ РАБОТА № 2

Исследование триггеров

Цель работы – исследование режимов работы триггеров на интегральных микросхемах.

Краткие теоретические сведения Триггер – это элемент, запоминающий информацию, представленную в

двоичном коде и не превышающую одного бита. Триггеры имеют два устойчивых состояния, обозначаемые как состояния 0 и 1. Эти состояния могут быть определены по логическим уровням на выходах. Триггер

снабжается двумя выходами: прямым выходом Q и инверсным Q . Логический уровень на выходе Q совпадает с состоянием триггера: если

триггер в состоянии 0, то и Q = 0, если триггер в состоянии 1, то и Q = 1.

13

Логический уровень на инверсном выходе Q представляет собой инверсию

состояния триггера (в состоянии 0, Q = 1 и наоборот). Триггеры имеют различные типы входов:

R (от англ. RESET) – раздельный вход установки в состояние 0; S (от англ. SET) – раздельный вход установки в состояние 1;

К – вход установки универсального триггера в состояние 0; J – вход установки универсального триггера в состояние 1; Т – счѐтный вход;

D (от англ. DELAY) – информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

С – исполнительный управляющий (синхронизирующий) вход; V – разрешающий управляющий вход.

По способу переключения и по закону функционирования триггеры можно разделить на следующие группы: RS – триггеры с раздельной установкой 0 и 1; D – триггеры задержки; JK – триггеры универсальные; Т – триггеры счѐтные (рис. 5).

По характеру реакции на входные сигналы триггеры делятся на два типа: асинхронные и синхронные. Асинхронный триггер характеризуется тем, что входные сигналы на состояние триггера действуют непосредственно с момента их подачи на входы, а в синхронных триггерах – только при подаче синхронизирующего сигнала на управляющий вход С.

а) б) в) г) д)

Рис. 5. Триггеры: а) асинхронный RS-триггер; б) синхронный RS-триггер;

в) D-триггер; г) Т-триггер; д) JK-триггер

Описание сменной платы П2 Принципиальная схема платы П2 приведена на рис. 6. Цифры на

границах пунктирного прямоугольника означают номера контактов на разъѐме X1. Блоки управления и индикации расположены в основном блоке ввода-

14

вывода стенда и используются при работе с данной платой. В качестве D1 используется интегральная микросхема К155ЛА3, в качестве элемента D2 – К155ЛА3, в качестве элемента D3 – К155ТМ2.

Порядок выполнения работы

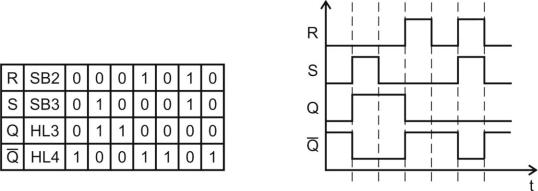

1.Выделить из рис. 6 и изобразить отдельно схему RS-триггера на элементах «ИЛИ-НЕ». В качестве источника сигнала использовать кнопки SB2, SB3. Состояние триггера определять с помощью диодов HL3, HL4. Сигналы управления триггером индицируются на светодиодах HL1, HL2. Экспериментально заполнить таблицу переходов триггера, по полученной таблице составить временную диаграмму (рис. 7). Обратить внимание на запрещѐнное состояние и состояние повтора (карта II-1).

2.Выделить из рис. 6 и изобразить отдельно схему RS-триггера на элементах «И-НЕ». В качестве источника сигнала использовать кнопки SB2, SB3. Состояние триггера определять с помощью диодов HL3, HL4. Инвертированные сигналы управления триггером отображаются на светодиодах HL1, HL2. Экспериментально заполнить таблицу переходов триггера, по полученной таблице составить временную диаграмму (карта II-2).

3.Выделить из рис. 6 и изобразить отдельно схему RS-триггера на микросхеме D3.1. В качестве источника сигнала использовать кнопки SB2, SB3. Входы D, С не используются (кнопка SB1 не нажата, a SA1 находится в фиксированном положении). Инвертированные сигналы управления триггером отображаются на светодиодах HL1, HL2. Выходная информация выводится на светодиоды HL3 (инверсный выход) и HL4 (прямой выход). Экспериментально заполнить таблицу переходов триггера, по полученной таблице составить временную диаграмму (карта II-3).

15

Рис. 6. Схема платы П2 и ее подключения к основному блоку

4. Выделить из рис. 6 и изобразить отдельно схему тактируемого D- триггера на интегральной микросхеме D3.1. Информационный сигнал D задаѐтся тумблером SA1, управляющий – кнопкой SB1. На входы R, S подать логические единицы. Выходная информация выводится на светодиоды HL1 (инверсный выход) и HL2 (прямой выход). Экспериментально получить таблицу переходов D-триггера. По полученной таблице составить временную диаграмму (карта II-4).

16

5. Выделить из рис. 6 и изобразить отдельно схему Т-триггера на базе интегральной микросхемы D3.2 путем надлежащей коммутации D-триггера (соединить перемычкой контакты X2 и Y1). В качестве источника сигнала использовать кнопку SB1. Выходная информация индицируется светодиодом HL1. Экспериментально заполнить таблицу переходов Т-триггера, по полученной таблице составить временную диаграмму (карта II-7).

а) б)

Рис. 7. Пример таблицы переходов а) и временной диаграммы б) RS-триггера

Отчѐт о работе В отчѐте должны содержаться:

1.Схема, экспериментальная таблица переходов и временная диаграмма RS-триггера на элементах «ИЛИ-НЕ».

2.Схема, экспериментальная таблица переходов и временная диаграмма RS-триггера на элементах «И-НЕ».

3.Схема, экспериментальная таблица переходов и временная диаграмма RS-триггера на интегральной микросхеме D3.1.

4.Схема, экспериментальная таблица переходов и временная диаграмма D-триггера на интегральной микросхеме D3.1.

5.Схема, экспериментальная таблица переходов и временная диаграмма T-триггера на интегральной микросхеме D3.2.

Вопросы для самоконтроля

1.Триггеры: определение и виды.

2.Схемы и таблицы переходов RS-, D-, Т-, JK-триггеров.

3.Асинхронные и синхронные RS-триггеры.

4.Принцип работы двухступенчатых триггеров.

5. Способы превращения JK-триггера в RS-, D-, Т-триггеры.

17

ЛАБОРАТОРНАЯ РАБОТА № 3

Исследование регистров

Цель работы – исследование режимов работы регистров, составленных из триггеров или выполненных на интегральных микросхемах, установленных на сменных платах П2 и П3.

Краткие теоретические сведения

Регистр – это устройство, предназначенное для приема и запоминания n- разрядного слова, а также выполнения определенных логических операций над этим словом. Регистры различают:

1.По виду выполняемых операций: регистры приема информации; регистры передачи информации; регистры сдвига информации.

2.По способу приема и передачи информации: последовательные регистры; параллельные регистры; параллельно-последовательные регистры.

3.По количеству каналов, по которым поступает информация: однофазные регистры, в которых информация поступает только по одному каналу: прямому или инверсному (D-триггеры); парафазные регистры, в которых информация поступает в каждый разряд по обоим каналам (синхронных RS-триггеры).

4.По количеству тактов управления, необходимых для записи слова: однотактные регистры; двухтактные регистры; многотактные (n-тактные) регистры.

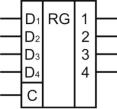

Рис. 8. Четырѐхразрядный регистр

В параллельные регистры запись числа осуществляется параллельным кодом, т. е. во все разряды одновременно. На рис. 8 представлен четырѐхразрядный параллельный регистр. Последовательные регистры характеризуются последовательной записью кода числа, начиная с младшего или старшего разряда, путем последовательного сдвига кода тактирующими импульсами. Параллельно-последовательные рег истры имеют входы как для параллельной, так и для последовательной записи кода числа.

18

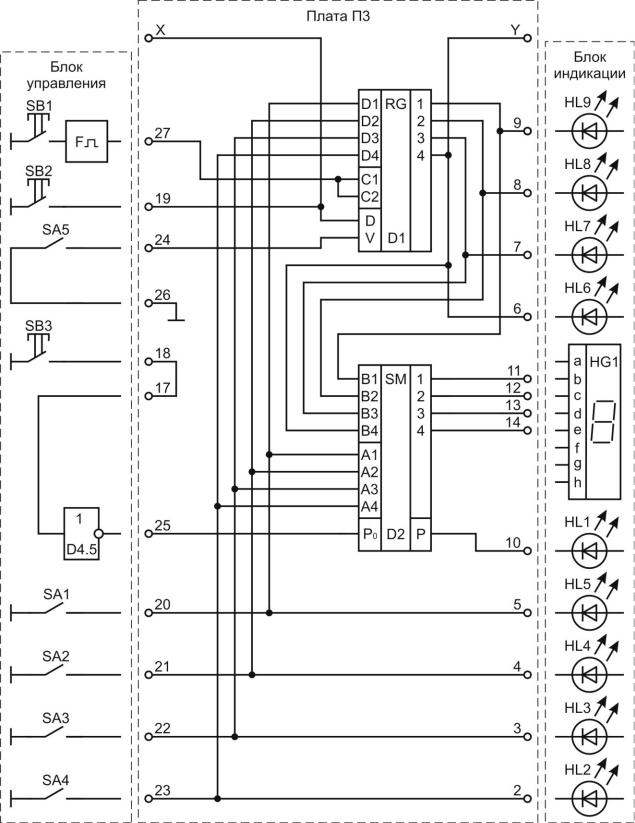

Описание сменной платы П3 Плата используется при исследовании регистров и сумматоров.

Принципиальная схема платы приведена на рис. 9. Цифры по пунктирному контуру означают номера контактов на разъѐме X1. Блоки индикации и управления относятся к блоку ввода-вывода информации. В качестве элемента D1 используется интегральная микросхема К155ИР1, в качестве элемента D2 – К155ИМ3.

Порядок выполнения работы 1. Исследование регистров на сменной плате П2.

1.1.Выделить из рис. 6 и изобразить отдельно схему параллельного регистра. Регистр составляется из двух триггеров (D3.1 – младший разряд, D3.2 – старший разряд). На младший разряд информация подаѐтся от тумблера SA1, а на старший – от SA3. При этом тумблер SA5 должен находиться в нижнем положении, а контакты Х1, Х2 замкнуты перемычкой. Запись информации производится кнопкой SB1, а индикация результатов – светодиодами HL1, HL2. На входах R и S триггера D3.1 должны быть установлены логические единицы. Осуществить запись всех возможных двухразрядных двоичных чисел в регистр и составить таблицу переходов с учетом тактовых сигналов. Используя полученную таблицу, изобразить временную диаграмму (карта II-5).

1.2.Выделить из рис. 6 и изобразить отдельно схему последовательного регистра. Регистр составляется из двух триггеров (D3.1 – младший разряд, D3.2 – старший разряд). Источником информации является ключ SА1. При этом тумблер SA5 должен находиться в верхнем положении, а контакты Х1, Х2 замкнуты перемычкой. Запись информации производится кнопкой SB1, а индикация результатов – светодиодами HL1, HL2. На входах R и S триггера D3.1 должны быть установлены логические единицы. Задавая различную входную информацию, наблюдать продвижение и хранение кода в регистре. Осуществить прохождение кода 1011 через предварительно очищенный регистр и составить таблицу переходов с учетом тактовых сигналов. Используя полученную таблицу, изобразить временную диаграмму (карта II- 6).

19

2. Исследование регистров на сменной плате П3.

2.1.Выделить из рис. 9 и изобразить отдельно схему последовательного регистра. В качестве регистра используется интегральная микросхема К155ИР1. Тактовый сигнал подаѐтся от кнопки SB1. Тумблер SA5 должен находиться в нижнем положении (V = 0). Информация задаѐтся кнопкой SB2. Четырѐхразрядное слово, запоминаемое регистром, отображается на светодиодах HL1 – HL4, при этом сдвиг осуществляется от младшего разряда (светодиод HL1) к старшему разряду (светодиод HL4). Записать в регистр шестнадцатеричные цифры 1, 4, B, D, представленные в двоичном коде. После каждой сохраненной цифры регистр обнулить. Составить таблицу переходов и временную диаграмму процесса записи цифр в регистр. Записать в регистр цифру 1 и, соединив перемычкой вход с выходом (контакты X и Y), наблюдать процесс перемещения 1 в закольцованном регистре, подавая тактовые сигналы кнопкой SB1. Составить таблицу переходов и временную диаграмму этого процесса. Записать в регистр цифру А и, соединив вход с выходом (контакты X и Y), превратить регистр в генератор прямоугольных импульсов, подавая тактовые сигналы кнопкой SB1. Нарисовать временную диаграмму работы генератора (карта III-1).

2.2.Выделить из рис. 9 и изобразить отдельно схему параллельного регистра. В качестве регистра используется интегральная микросхема К155ИР1. Тактовый сигнал подаѐтся от кнопки SB1. Тумблер SA5 должен находиться в верхнем положении (V = 1). Четырѐхразрядное слово задаѐтся тумблерами SA1 – SA4 и индицируется светодиодами HL1 – HL4. Младший разряд слова задаѐтся тумблером SA1 (светодиод HL4). Код, хранящийся в регистре, отображается светодиодами HL5 – HL8. Младший разряд – светодиод HL8. Записать в регистр шестнадцатеричные цифры 0, 5, 9, С, E, F, представленные в двоичном коде. После каждой сохраненной цифры регистр обнулить. Составить таблицу переходов и временную диаграмму процесса записи цифр в регистр (карта III-2).

20

Рис. 9. Схема платы П3 и ее подключения к основному блоку