4788

.pdf

31

дешифратора D1 и индицируются на светодиодах HL2 – HL9. Информационные сигналы в дешифратор D1 подаются от тумблеров SA1 – SA3, синхронизирующий сигнал – от кнопки SB2. Код адреса информационного входа мультиплексора D2 набирается тумблерами SA1 – SA3 и «защелкивается» в регистре D3 кнопкой SB3. Светодиод HL1 показывает значение выхода мультиплексора D2. Задать код адреса 011, перебрать все возможные выходные коды дешифратора D1, наблюдая изменения на светодиодах HL1 – HL9. Составить таблицу переходов и временную диаграмму работы элементов D1, D2 и D3 (карта IV-3).

Рис. 14. Обозначения сегментов индикатора HG1

Отчѐт о работе В отчѐте должны содержаться:

1.Схема, экспериментальная таблица переходов и временная диаграмма дешифратора на интегральной микросхеме D1.

2.Схема, экспериментальная таблица переходов и временная диаграмма демультиплексора на интегральной микросхеме D1.

3.Схема, экспериментальная таблица истинности и временная диаграмма преобразователя кодов на интегральной микросхеме D5.

4.Схема, экспериментальная таблица переходов и временная диаграмма мультиплексора на интегральной микросхеме D2.

Вопросы для самоконтроля

1.Комбинационные и последовательностные устройства.

2.Шифратор и дешифратор. Виды дешифратора.

3.Мультиплексор и демультиплексор: принцип работы, области применения.

4.Преобразование двоичного и шестнадцатеричного кода в семисегментный код.

5.Виды памяти микроЭВМ.

32

ЛАБОРАТОРНАЯ РАБОТА № 6

Исследование универсального счётчика

Цель работы – исследование работы счѐтчика в режимах прямого и обратного счѐта.

Краткие теоретические сведения Счѐтчик – это устройство для подсчѐта сигналов, поступающих на его

вход, и хранения этого числа сигналов в виде кода в триггерах. Счѐтчик может быть реализован на Т-, D-, JK-триггерах.

Счѐтчик предназначен для подсчѐта шагов программы, циклов сложения, вычитания, умножения, деления, преобразования кодов и т. п. По целевому назначению счѐтчики подразделяются на простые (суммирующие и вычитающие) и реверсивные (объединяют функции суммирования и вычитания). На простые счѐтчики (рис. 15) сигналы поступают с одним знаком, т. е. в одном направлении. Реверсивные счѐтчики предназначены для работы в режиме сложения и вычитания.

По способу организации счѐта счѐтчики подразделяются на асинхронные и синхронные. По способу организации цепей переноса между разрядами различают счѐтчики с последовательным, групповым, сквозным, частично групповым переносом. По способу кодирования счѐтчики подразделяются на счѐтчики, работающие в двоичных кодах; счѐтчики, работающие в кодах Грея, Либау-Крейга, Котца; счѐтчики специальных непозиционных кодов.

Основные характеристики счѐтчика:

–модуль счѐта – характеризуюет число устойчивых состояний счѐтчика, т. е. предельное число входных сигналов, которые может сосчитать счѐтчик;

–разрешающая способность – минимально допустимый период следования входных сигналов, обеспечивающий надежную работу счѐтчика;

–время регистрации – интервал времени между моментами поступления входного сигнала и окончания самого длинного переходного процесса в счѐтчике;

–ѐмкость счѐтчика – максимальное число единичных сигналов, которое может быть зафиксировано в счѐтчике. Зависит от основания системы счисления и числа разрядов.

33

Рис. 15 Четырѐхразрядный суммирующий счѐтчик

Обычно счѐтчик имеет цепь установки в 0 (сброс триггеров), однако начальное состояние может устанавливаться передачей в счѐтчик кода некоторого числа, с которого будет начинаться операция счѐта единиц. Такой режим необходим при образовании последовательности адресов команд при заданном начальном адресе.

Если после заполнения счѐтчика единицами не прекратится подача входных сигналов, то наступит переход счѐтчика через состояние 0 и во всех разрядах подсчѐт импульсов начинается сначала. Этот режим счѐтчика называется циклическим, а счѐтчик называется пересчѐтным. В течение цикла на счѐтчик поступает 2n импульсов, где n – число разрядов.

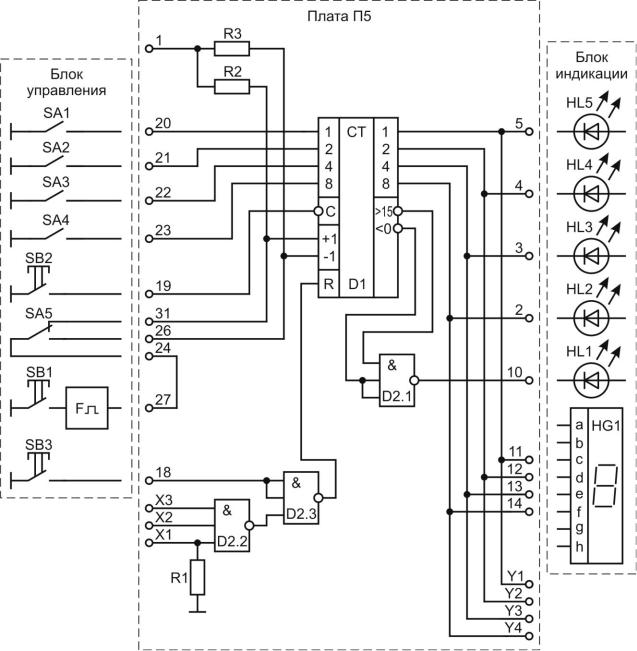

Описание сменной платы П5 Принципиальная схема платы П5 изображена на рис. 16. В качестве

универсального счѐтчика используется интегральная микросхема D1 типа К155ИЕ7. Микросхема К155ЛА4 (D2) выполняет вспомогательную роль. Цифры по пунктирному контуру означают номера контактов на разъѐме X1. Блоки индикации и управления относятся к блоку ввода-вывода информации.

Порядок выполнения работы 1. Выделить из рис. 16 и изобразить отдельно схему суммирующего

счѐтчика, представленного последовательным соединением триггеров. Счѐтчик, реализованный на интегральной микросхеме D1, имеет 4 выхода, которые соединены со светодиодами HL1 – HL4. Входные импульсы подаются кнопкой SB1. Тумблер SA5 находится в верхнем положении. Количество разрядов счѐтчика можно изменить, соединив перемычкой контакт X1 (к контакту X1 через резистор R1 подведен логический 0) с одним из контактов Y2, Y3, Y4. Если контакт X1 соединѐн с контактом Y2, то счѐтчик имеет 1 разряд. Если контакты не соединены, то счѐтчик имеет максимальное количество разрядов для микросхемы D1 равное 4. После того как значение

34

каждого разряда счѐтчика становится равным 1 (светодиоды светятся), подача очередного импульса кнопкой SB1 вызовет обнуление счѐтчика (светодиоды не светятся), и процесс счѐта начнется сначала. Составить таблицу переходов

ивременную диаграмму одного цикла работы двухразрядного, трѐхразрядного

ичетырѐхразрядного суммирующего счѐтчика (карта V-1).

2.Выделить из рис. 16 и изобразить отдельно схему вычитающего счѐтчика, представленного последовательным соединением триггеров. Счѐтчик реализован на интегральной микросхеме D1, значения выходных четырѐхразрядных кодов индицируются светодиодами HL1 – HL4. Младший разряд – светодиод HL4. Входные импульсы подаются кнопкой SB1. Сброс счѐтчика (обнуление выходных сигналов) осуществляется кнопкой SB3. Тумблер SA5 находится в нижнем положении. Начальное положение вычитающего счѐтчика 1111 (светодиоды HL1 – HL4 светятся). После того как значение каждого разряда счѐтчика становится равным 0, подача очередного импульса кнопкой SB1 вызовет перегрузку счѐтчика и светодиоды HL1 – HL4 загорятся. Счѐтчик готов к новому циклу. Составить таблицу переходов и временную диаграмму одного цикла работы четырѐхразрядного вычитающего счѐтчика (карта V-2).

35

Рис. 16. Схема платы П5 и ее подключения к основному блоку

3. Выделить из рис. 16 и изобразить отдельно схему реверсивного счѐтчика с предустановкой. Входные импульсы подаются кнопкой SB1. Тумблеры SA1 – SA4 и кнопка предустановки SB2 осуществляют начальную загрузку счѐтчика. Тумблер SA1 задаѐт значение младшего разряда счѐтчика. Кнопка SB3 осуществляет сброс счѐтчика. Тумблер SA5 переключает режимы работы реверсивного счѐтчика: верхнее положение – суммирующий счѐтчик, нижнее положение – вычитающий счѐтчик. Выходной четырѐхразрядный код отображается светодиодами HL2 – HL5. Значение младшего разряда

36

показывает светодиод HL5. Четырѐхразрядный код с выходов реверсивного счѐтчика поступает на дешифратор D5, который преобразует его в семисегментный код индикатора HG1. На экране индикатора HG1 отображается состояние счѐтчика в виде шестнадцатеричных цифр. Когда значение счѐтчика будет < 0 или > 15, с соответствующего выхода поступит сигнал низкого уровня, и светодиод HL1 загорится. После этого счѐтчик перейдѐт в первоначальное состояние 1111 или 0000 в зависимости от режима работы (вычитание или сложение). Обнулить реверсивный счѐтчик и перевести все тумблеры в нижнее положение. С помощью тумблеров SA1 – SA4 и кнопки SB2 загрузить в счѐтчик шестнадцатеричную цифру 4. Затем, используя тумблер SA5 и кнопку SB1, перевести счѐтчик в состояние 1000, отображающееся на светодиодах HL2 – HL5. С помощью тумблера SA5 и кнопки SB1 вернуть в память счѐтчика шестнадцатеричную цифру 4. Произвести сброс значений счѐтчика. Составить таблицу переходов и временную диаграмму процесса работы реверсивного счѐтчика (карта V-3).

Отчѐт о работе В отчѐте должны содержаться:

1.Схема, экспериментальная таблица переходов и временная диаграмма суммирующего счѐтчика.

2.Схема, экспериментальная таблица переходов и временная диаграмма вычитающего счѐтчика.

3.Схема, экспериментальная таблица переходов и временная диаграмма реверсивного счѐтчика с предустановкой.

Вопросы для самоконтроля

1.Счѐтчик: определение и виды.

2.Основные характеристики счѐтчика.

3.Принципы построения счѐтчиков прямого и обратного счѐта.

4.Принцип построения счѐтчика с изменяемым числом разрядов.

5.Осуществление сброса значений счѐтчика.

37

Библиографический список

1.Бойт, К. Цифровая электроника [Текст] / К. Бойт. – М. : Техносфера,

2007. – 472 с.

2.Букреев, И. Н. Микроэлектронные схемы цифровых устройств [Текст]

/И. Н. Букреев, В. И. Горячев, Б. М. Мансуров. – М. : Техносфера, 2009. –

712 с.

3.Кочетов, В. И. Основы микропроцессорной техники [Текст] : учеб. пособие / В. И. Кочетов. – Воронеж, 2001. – 134 с.

4.Кузин, А. В. Микропроцессорная техника [Текст] : учеб. / Жаворонков М. А. М.: Академия, 2007. – 304 с.

5.Мержи, И. Теория и практика применения цифровых логических микросхем [Текст] / И. Мержи ; пер. с англ. Ю. Соколов. – М. : НТ Пресс,

2007. – 256 с.

6.Нефедов, А. В. Интегральные микросхемы и их зарубежные аналоги [Текст] : справочник : в 12 т. Т. 2. – М. : РадиоСофт, 2000. – 640 с.

7.Стенд универсальный по основам автоматики и электронновычислительной техники [Текст]. – Омск : ОГПИ, 1990. – 53 с.

8.Фрике, К. Вводный курс цифровой электроники [Текст] / К. Фрике. – М. : Техносфера, 2003. – 432 с.

38

Приложение

ОСНОВНЫЕ ПРАВИЛА АЛГЕБРЫ ЛОГИКИ

1. |

Y |

X |

0 |

0 |

|||

2. |

Y |

X |

1 |

X |

|||

3. |

Y |

X |

X |

X |

|||

4. |

|

|

|

|

|

|

|

Y |

X |

X |

0 |

||||

5. |

Y |

X |

0 |

X |

|||

6. |

Y |

X |

1 |

1 |

|||

7. |

Y |

X |

X |

X |

|||

8. |

|

|

|

|

|

|

|

Y |

X |

X |

1 |

||||

9. |

|

|

|

|

|||

|

|

|

|

|

|

|

|

Y |

X |

X |

|

||||

10. Y |

X1 |

X 2 |

X 2 |

||||||||

11. Y |

X1 |

X 2 |

X 2 |

||||||||

12. Y |

(X1 |

|

X |

2 ) |

|

|

|

X3 |

|||

13. Y |

(X1 |

|

X |

2 ) |

|

|

|

X3 |

|||

14. Y |

X1 |

(X |

2 |

|

|

X3 ) |

|||||

15. Y |

X1 |

(X 2 |

|

|

X3 ) |

||||||

16. Y |

X1 |

X1X 2 |

|

|

|

X1 |

|||||

17. Y |

X1 |

( X1 |

|

|

X 2 ) |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

18. Y |

X1 |

X1X 2 |

|

|

|

X1 |

|||||

|

|

|

|

|

|

|

|

|

|

||

19. Y |

X1 |

( X1 |

|

|

X 2 ) |

||||||

|

|

|

|

|

|

|

|||||

20. Y |

X1X 2 |

|

X1X 2 |

||||||||

21. Y |

( X1 |

|

X 2 ) |

|

|

( X1 |

|||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

||||||

22. Y |

X1 |

X 2 |

|

X1 |

|||||||

|

|

|

|

|

|

||||||

23. Y |

X1 |

X 2 |

X1 |

||||||||

X1 |

|

|

– Переместительный закон |

|||

X1 |

|

|

||||

|

|

|

||||

X1 |

(X 2 |

X3 ) |

– Сочетательный закон |

|||

X1 |

(X 2 |

X3 ) |

||||

|

||||||

X1X 2 X1X3 |

– Распределительный |

|||||

(X1 |

X 2 ) |

(X1 |

X3 ) закон |

|||

X1 |

|

|

– Закон поглощения |

|||

|

|

|

||||

X 2 |

|

|

– Закон свертки |

|||

X1 |

X 2 |

|

||||

|

|

|||||

X1 |

|

|

– Закон склеивания |

|||

|

|

|

|

|

||

X 2 ) |

X1 |

|

|

|||

X 2

X 2

39

Оглавление

Введение…………………………………………………………………………….3

Описание лабораторного стенда…………………………………………………..4 Лабораторная работа № 1. Исследование логических элементов………………7

Лабораторная работа № 2. Исследование триггеров…………………………...12 Лабораторная работа № 3. Исследование регистров…………………………...17 Лабораторная работа № 4. Исследование сумматоров…………………………23

Лабораторная работа № 5. Исследование комбинационных устройств………26

Лабораторная работа № 6. Исследование универсального счетчика………….32

Библиографический список………………………………………………………37

Приложение………………………………………………………………………..38

40

Учебное издание

Павел Валерьевич Мурзинов Юрий Валерьевич Мурзинов

МИКРОПРОЦЕССОРНАЯ ТЕХНИКА

Лабораторный практикум

Редактор Е.А. Попова

Подписано в печать 13.02.2012. Формат 60×90 /16. Объем 2,5 п. л. Усл. печ. л. 2,5. Уч.-изд. л. 2,45. Тираж 100 экз. Заказ

ФГБОУ ВПО «Воронежская государственная лесотехническая академия» РИО ФГБОУ ВПО «ВГЛТА». 394087, г. Воронеж, ул. Тимирязева, 8 Отпечатано в УОП ФГБОУ ВПО «ВГЛТА»

394087, г. Воронеж, ул. Докучаева, 10