4788

.pdf21

2.3. Выделить из рис. 9 и изобразить отдельно схему универсального регистра, сочетающего в себе функции последовательного и параллельного регистров. Светодиоды HL2 – HL5 отражают входные значения (параллельный код), светодиоды HL6 – HL9 – выходные значения универсального регистра. Обнулив регистр, через параллельный вход, используя тумблеры SA1 – SA5 и кнопку SB1, занести в регистр шестнадцатеричную цифру 8 и разделить ее на 4, оперируя тумблером SA5 и кнопкой SB1 (перемычка соединяет контакты X и Y платы П3). Обнулив регистр, через параллельный вход, используя тумблеры SA1 – SA5 и кнопку SB1, занести в регистр шестнадцатеричную цифру A и разделить ее на 2, оперируя тумблером SA5 и кнопкой SB1 (перемычка соединяет контакты X и Y платы П3). Обнулив регистр, через параллельный вход, используя тумблеры SA1 – SA5 и кнопку SB1, занести в регистр шестнадцатеричную цифру В и, оперируя тумблером SA5 и кнопкой SB1, преобразовать еѐ в цифру 7, а затем в цифру D (перемычка соединяет контакты X и Y платы П3). Составить таблицу переходов и временную диаграмму процесса записи и преобразования цифр в регистре.

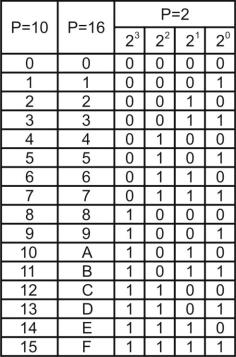

Для упрощения преобразования шестнадцатеричных цифр в двоичный четырѐхразрядный код на рис. 10 представлена таблица эквивалентности десятичных, шестнадцатеричных и двоичных чисел.

Отчѐт о работе В отчѐте должны содержаться:

1.Схема параллельного регистра на микросхемах D3.1, D3.2. Таблица переходов и временная диаграмма записи двухразрядных чисел в регистр.

2.Схема последовательного регистра на микросхемах D3.1, D3.2. Таблица переходов и временная диаграмма процесса прохождения кода 1011 через регистр.

3.Схема последовательного регистра на микросхеме К155ИР1. Таблица переходов и временная диаграмма записи шестнадцатеричных цифр 1, 4, B, D

врегистр.

4.Таблица переходов и временная диаграмма процесса перемещения 1 в закольцованном регистре.

22

5. Временная диаграмма работы генератора прямоугольных импульсов, синтезированного на последовательном регистре микросхемы D1.

Рис. 10. Таблица эквивалентности десятичных, шестнадцатеричных

идвоичных чисел

6.Схема параллельного регистра на микросхеме К155ИР1. Таблица переходов и временная диаграмма записи шестнадцатеричных цифр 0, 5, 9, С, E, F в регистр.

7.Схема универсального регистра на микросхеме D1. Таблица переходов и временная диаграмма записи в регистр цифры 8 и еѐ деления на 4, записи в регистр цифры А и еѐ деления на 2, записи в регистр цифры В и еѐ преобразования в цифру 7 и D.

Вопросы для самоконтроля

1.Регистры: определение, особенности построения.

2.Принцип построения регистров, сдвигающих информацию вправо и

влево.

3.Описание процедуры записи, хранения, сдвига информации в универсальном регистре.

4.Системы счисления: двоичная, восьмеричная и шестнадцатеричная, преобразование из одной системы счисления в другую.

23

ЛАБОРАТОРНАЯ РАБОТА № 4

Исследование сумматоров

Цель работы – исследование основных принципов работы сумматора, реализованного на интегральной микросхеме, установленной на сменной плате П3.

Краткие теоретические сведения Сумматор – это электронный узел, выполняющий операцию

суммирования цифровых кодов двух чисел. Различают два вида сумматоров: комбинационные, выполняющие суммирование и не обладающие функцией запоминания, и накопительные, которые кроме суммирования способны хранить результаты.

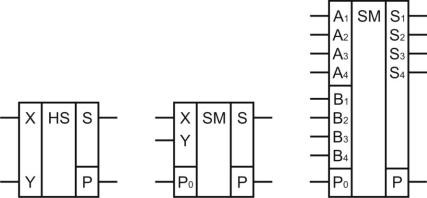

В цифровых устройствах применяются одноразрядные сумматоры на 2 и 3 входа, причем первый из них называется полусумматором, или сумматором по модулю 2, а второй – полным одноразрядным сумматором (рис. 11).

а) б) в)

Рис. 11. Сумматоры: а) полусумматор; б) одноразрядный сумматор; в) четырѐхразрядный сумматор

При сложении двух чисел независимо от системы счисления в каждом разряде производится сложение трѐх цифр: цифры данного разряда первого слагаемого, цифры данного разряда второго слагаемого и цифры переноса из соседнего младшего разряда. В результате сложения для каждого разряда получаются: цифра суммы этого разряда и цифра переноса в следующий старший разряд.

24

В зависимости от того, каким образом передаются числа, могут быть два способа сложения: последовательный и параллельный. Если для передачи каждого числа используется один канал, по которому код числа передаѐтся в виде временной последовательности сигналов, то используется последовательный способ сложения. Если для передачи каждого разряда числа предусмотрен отдельный канал, то применяется параллельный способ сложения.

Последовательный сумматор обычно строится на основе одноразрядного комбинационного сумматора.

Параллельный способ сложения предусматривает наличие отдельных сумматоров для каждого разряда чисел. Этот способ реализуется в сумматоре с поразрядным последовательным переносом. В сумматорах этого типа перенос распространяется последовательно от разряда к разряду по мере образования цифры суммы в каждом отдельном разряде.

Одноразрядный сумматор может быть использован для выполнения операции вычитания. Для этого на один из его входов подаѐтся либо прямой, либо обратный код слагаемого, соответствующий его отрицательному значению.

Порядок выполнения работы 1. Выделить из рис. 9 и изобразить отдельно схему четырѐхразрядного

сумматора, реализованного на интегральной микросхеме К155ИМ3 – D2. Слагаемое В4В3В2В1 задаѐтся с помощью регистра D1 и индицируется светодиодами HL6 – HL9. Светодиод HL6 показывает значение старшего разряда, светодиод HL9 – младшего разряда. Кнопка SB1 подаѐт синхронизирующие сигналы управления регистром D1. Тумблер SA5 переключает режимы работы регистра D1: верхнее положение – параллельный регистр, нижнее положение – последовательный регистр. Тумблеры SA1 – SA4 и кнопка SB2 задают четырѐхразрядное слово в регистр. Значение слагаемого А4А3А2А1 подаѐтся в сумматор от тумблеров SA1 – SA4 и отображается светодиодами HL2 – HL5. Светодиод HL2 показывает значение старшего разряда, светодиод HL5 – младшего разряда. Кнопка SB3 задаѐт цифру переноса в младший разряд. Сумма поступает на дешифратор D5 и отображается семисегментным индикатором HG1 в шестнадцатеричном коде.

25

Для суммы цифра переноса в старший разряд отображается светодиодом HL1

(карта III-3).

2.Перевести регистр D1 в последовательный режим и произвести сложение шестнадцатеричных цифр: 1 + А; 4 + С; D + D; 6 + F. Составить таблицу переходов и временную диаграмму сложения шестнадцатеричных цифр (карта III-3).

3.Перевести регистр D1 в параллельный режим и произвести сложение шестнадцатеричных цифр: 7 + А; 4 + 5. Сначала задавать слагаемое В4В3В2В1. Составить таблицу переходов и временную диаграмму сложения шестнадцатеричных цифр. Произвести сложение шестнадцатеричных цифр: 3

+4; D + 2 с добавлением 1 в младший разряд кнопкой SB3. Составить таблицу переходов и временную диаграмму сложения шестнадцатеричных цифр (карта

III-3).

Отчѐт о работе В отчѐте должны содержаться:

1.Схема четырѐхразрядного сумматора, реализованного на интегральной микросхеме К155ИМ3.

2.Таблица переходов и временная диаграмма сложения шестнадцатеричных цифр при работе регистра в последовательном режиме.

3.Таблица переходов и временная диаграмма сложения шестнадцатеричных цифр при работе регистра в параллельном режиме.

4.Арифметические выражения сумм в шестнадцатеричном и двоичном

кодах.

Вопросы для самоконтроля

1.Сумматор: определение и виды.

2.Назначение входа переноса из младшего разряда в старший разряд многоразрядного сумматора.

3.Реализация одноразрядного сумматора на основе полусумматора.

4.Прямой и обратный код и их применение в сумматоре-вычитателе.

26

ЛАБОРАТОРНАЯ РАБОТА № 5

Исследование комбинационных устройств

Цель работы – исследование дешифратора, демультиплексора, мультиплексора, преобразователя кодов.

Краткие теоретические сведения Различают два типа цифровых устройств: комбинационные

(однотактные) и последовательностные (многотактные).

Комбинационными называют цифровые устройства, в которых значения выходных сигналов определяются заданным в данный момент времени сочетанием входных воздействий. В комбинационных логических устройствах отсутствуют запоминающие элементы.

Последовательностными называют устройства, в которых выходные сигналы зависят не только от входных воздействий в заданный момент времени, но и от их предыдущих значений. Поэтому последовательностные устройства в отличие от комбинационных содержат запоминающие элементы.

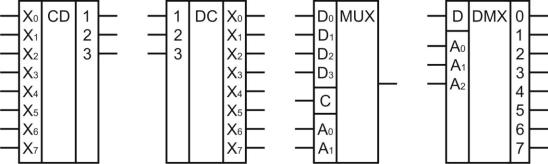

К комбинационным устройствам относят следующие: шифратор, дешифратор, мультиплексор, демультиплексор (рис. 12).

Шифратор – устройство для преобразования унитарного (однопозиционного) кода в двоичный позиционный. Т. е. устройство, осуществляющее преобразование десятичных чисел в двоичную систему счисления. Сигнал на одном из входов приводит к появлению на выходах n- разрядного двоичного числа, соответствующего номеру активизированного входа. Шифратор называют полным, если число его входов 2n (n – число выходов).

Шифраторы широко используются в разнообразных устройствах ввода информации в цифровые устройства. Такие устройства ввода могут снабжаться клавиатурой, каждая клавиша которой связана с определенным входом шифратора.

27

а) б) в) г) Рис. 12 Комбинационные устройства: а) шифратор; б) дешифратор;

в) мультиплексор; г) демультиплексор

Дешифратор – это устройство ЭВМ, обеспечивающее формирование для n-входовой схемы активный сигнал только на одном из его выходов. Максимальное количество выходов может быть 2n, такой дешифратор называют полным. Дешифратор выполняет микрооперацию преобразования позиционного двоичного кода в унитарный (однопозиционный) цифровой код.

Если длина дешифрируемого двоичного слова, входящих в устройство, больше возможного числа входов, используют многоступенчатое (каскадное) построение дешифратора. Таким образом, выбор той или иной схемы дешифратора определяется в основном длиной дешифрируемого слова и используемой для построения элементной базой. Для дешифрации длинных слов (n = 10 и более) используют матричный дешифратор, в котором входное слово разбивается на полслова и дешифрируется на линейных дешифраторах, выходы которых подключаются на входы следующей ступени дешифратора.

Мультиплексор – операционный узел ЭВМ, осуществляющий микрооперацию передачи сигнала с одного из своих входов на единственный выход. Выбор входного сигнала осуществляется в соответствии с кодом, поступающим на адресный управляющий вход. Мультиплексор, как правило, имеет информационные входы (D0, D1,...), адресные входы (А0, А1,...), вход для подачи стробирующего сигнала С и один выход. Каждому из информационных входов мультиплексора присваивается номер, называемый адресом. При подаче стробирующего сигнала на вход С мультиплексор выбирает один из входов и подключает его к выходу.

Демультиплексор – операционный узел ЭВМ, осуществляющий микрооперацию передачи сигнала с единственного информационного входа на

28

один из нескольких выходов. Вход подключается к выходу, имеющему заданный адрес. Адреса задаются при помощи адресных входов.

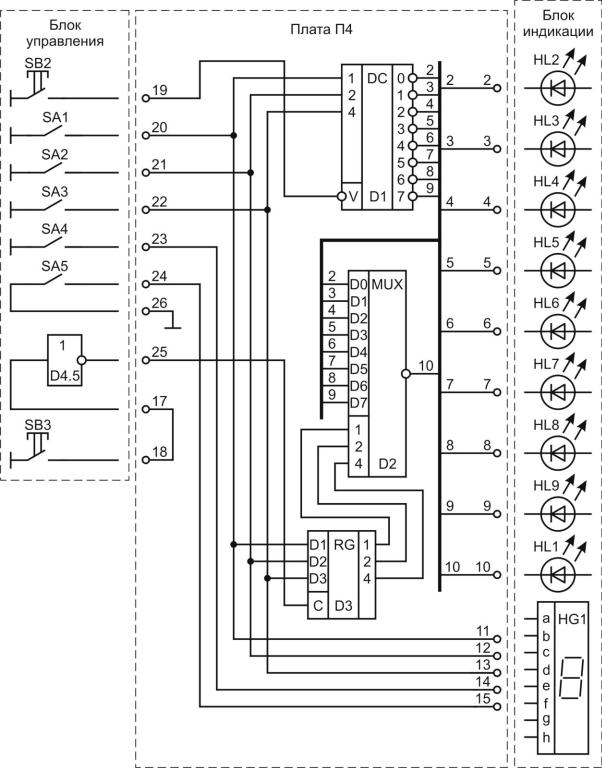

Описание сменной платы П4 Принципиальная схема платы изображена на рис. 13. Дешифратор-

демультиплексор выполнен на интегральной микросхеме D1 типа К155ИД4. В качестве мультиплексора используется интегральная микросхема К155КП5 (D2). Интегральная микросхема D3 типа К155ТМ5 используется как регистр для хранения информации, записываемой по тактовому сигналу от кнопки

SB3.

Порядок выполнения работы

1.Выделить из рис. 13 и изобразить отдельно схему дешифратора. В качестве дешифратора используется интегральная микросхема D1. Тактовый сигнал подаѐтся от кнопки SB2 (при нажатой кнопке SB2 значение входа V = 1). Выходные значение отображаются на светодиодах HL1 – HL8. Входной код задаѐтся тумблерами SA1 – SA3. Перебирая все возможные значения трѐхразрядного входного кода, используя тумблеры SA1 – SA3 и кнопку SB2, наблюдать выходные значения. Составить таблицу переходов и временную диаграмму работы дешифратора (карта IV-1).

2.Выделить из рис. 13 и изобразить отдельно схему демультиплексора.

Вкачестве демультиплексора используется интегральная микросхема D1. Информация задаѐтся с помощью кнопки SB2 и отображается на одном из выходов (светодиоды HL1 – HL8). Адреса выходов демультиплексора задаются тумблерами SA1 – SA3. Набирая различные адреса выходных каналов, осуществить передачу информации от ключа SB2 к индикаторам HL1

– HL8. Составить таблицу переходов и временную диаграмму работы демультиплексора (карта IV-1).

3.Выделить из рис. 1, 13 и изобразить отдельно схему преобразователя кодов. В качестве дешифратора D5 используется интегральная микросхема К155РЕ3, являющейся программируемым ПЗУ. Преобразователь кодов осуществляет преобразование десятичного и шестнадцатеричного кода в семисегментный код индикатора HG1 типа АЛС321Б. Ёмкость ПЗУ 32 и 8 бит. Вход дешифратора D5 V = 1. Входной код задаѐтся тумблерами SA1 – SA5. Тумблер SA1 задаѐт значение младшего разряда в двоичном коде. Если тумблер SA5 = 1, то шестнадцатеричный код преобразуется в семисегментный

29

код индикатора HG1. Если SA5 = 0, то семисегментный индикатор HG1 высвечивает десятичные числа (запятая означает единицу во втором разряде десятичного числа). На индикаторе HG1 смонтировано 7 сегментов и запятая (рис. 14). Каждый выход дешифратора D5 (h, g, f, e, d, c, b, a) соответствуют одному элементу семисегментного индикатора HG1. Если элемент индикатора HG1 светится, то значение соответствующего выхода дешифратора D5 равно 1. Выходы дешифратора D5 образуют двухразрядное шестнадцатеричное число, каждый разряд которого представляет собой двоичный четырѐхразрядный код – тетраду (a и e – значения младших разрядов четырѐхразрядных двоичных чисел). Данное двухразрядное шестнадцатеричное число является семисегментным кодом. Манипулируя тумблерами SA1 – SA5, наблюдать информацию на индикаторе HG1. Составить таблицу истинности, ставящую в соответствие десятичный и шестнадцатеричный код семисегментному коду индикатора HG1 (карта IV-2).

30

Рис. 13. Схема платы П4 и ее подключения к основному блоку

4. Выделить из рис. 13 и изобразить отдельно схему мультиплексора. Мультиплексор, реализованный на интегральной микросхеме D2, имеет 8 информационных входов (D0 – D7) и 3 адресных входа (1, 2, 4). Значения информационных входов мультиплексора D2 поступают с выходов