Лекции

.pdf

левой синхросигнал на входе V разрешает передачу информации с выбранного входа на выход. Если V=0, то F=0 независимо от информационных сигналов. Булево выражение, описывающее функционирование рассматриваемого мультиплексора имеет вид:

F V ( A2 A1 A0 D 0 A2 A1 A0 D 1 A2 A1 A0 D 2 A 2 A1 A0 D 3

A2 A1 A0 D 4 A2 A1 A0 D 5 A2 A1 A0 D 6 A 2 A1 A0 D 7 )

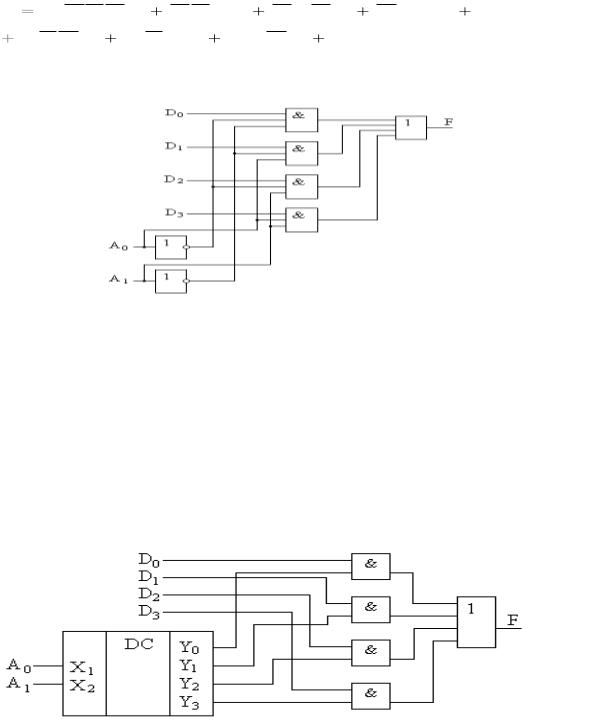

Схему мультиплексора «4x1» можно реализовать с помощью логических элементов базиса И-ИЛИ-НЕ:

Рис.4.14.12. Схема мультиплексора «4x1» без стробирующего сигнала

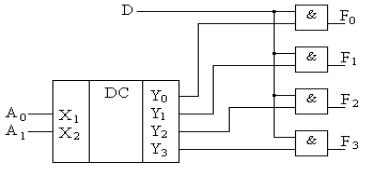

3.14.4.2 Реализация мультиплексора на базе дешифратора

Мультиплексор можно реализовать, используя дешифратор и элементы И и ИЛИ. Дешифратор формирует логическую единицу на одном из выходов согласно входному двоичному коду. Сигналы с выходов дешифратора являются стробирующими, т.е. разрешающими сигналами для схемы совпадения единиц, реализованной на двухвходовых элементах И. Логическая единица будет формироваться на выходе только того элемента И, на один вход которого подается единица с выхода дешифратора и на второй вход – единица с соответствующего входа Di. Для объединения выходов всех элементов И в один выход F, служит элемент ИЛИ. На его выходе формируется логическая единица, если таковая присутствует на опрашиваемом в данный момент входе Di.

Рис.4.14.13. Реализация мультиплексора «4x1» на базе дешифратора

Для увеличения числа каналов объединяют несколько мультиплексоров, используя для этой цели стробированые входы.

3.14.4.3 Демультиплексоры.

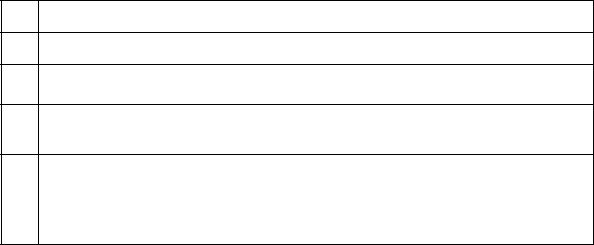

Демультиплексор – это логическое устройство, предназначенное для переключения сигнала с одного информационного входа на один из информационных выходов. На схемах демультиплексоры обозначают через DMX или DMS.

Демультиплексор выполняет функцию, обратную мультиплексору, т.е. в соответствии с принятой адресацией A0, A1 ,…, An-1 направляет информацию с единственного входа D на один из M выходов F0, F1, … , FM-1. При этом на остальных выходах будут логические нули (единицы). Принцип работы демультиплексора «1x4» иллюстрируется таблицей истинности:

A0 |

A1 |

F3 |

F2 |

F1 |

F0 |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

D |

|

|

|

|

|

|

0 |

1 |

0 |

0 |

D |

0 |

|

|

|

|

|

|

1 |

0 |

0 |

D |

0 |

0 |

|

|

|

|

|

|

1 |

1 |

D |

0 |

0 |

0 |

|

|

|

|

|

|

Булево выражение, описывающее функционирование рассматриваемого мультиплексора имеет вид:

|

|

|

|

|

|

|

|

D , |

F |

0 |

|

A A |

0 |

||||

|

|

1 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

F1 |

A1 |

A0 D , |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

F2 |

|

A1 |

|

A0 |

D , |

|||

|

|

|

|

|

|

|

|

|

F3 |

|

A1 A0 D . |

||||||

3.14.4.4 Реализация демультиплексора на базе дешифратора.

Демультиплексор можно реализовать, используя дешифратор и элемент И. Дешифратор формирует логическую единицу на одном из выходов согласно входному двоичному коду. Сигналы с выходов дешифратора являются стробирующими (разрешающими) сигналами для схемы совпадения единиц, реализованной на двухвходовых элементах И. Логическая единица будет формироваться на выходе только того элемента И, на один вход которого подается единица с выхода дешифратора и на второй вход – единица с входа D.

3.14.5. Триггеры и регистры.

Триггеры и регистры являются простейшими представителями последовательностных цифровых микросхем. Если выходные сигналы логических элементов и комбинационных микросхем однозначно определяются их текущими входными сигналами, то выходные сигналы микросхем с внутренней памятью зависят также еще и от того, какие входные сигналы и в какой последовательности поступали на них в прошлом, то есть они помнят предысторию поведения схемы. Именно поэтому их применение позволяет строить гораздо более сложные и интеллектуальные цифровые устройства, чем в случае простейших микросхем без памяти.

Триггеры и регистры сохраняют свою память только до тех пор, пока на них подается напряжение питания. Иначе говоря, их память относится к типу оперативной (в отличие от постоянной памяти и перепрограммируемой постоянной памяти, которым отключение питания не мешает сохранять информацию). После выключения питания и его последующего включения триггеры и регистры переходят в случайное состояние, то есть их выходные сигналы могут устанавливаться как в уровень логической единицы, так и в уровень логического нуля. Это необходимо учитывать при проектировании схем.

Большим преимуществом триггеров и регистров перед другими типами микросхем с памятью является их максимально высокое быстродействие (то есть минимальные времена задержек срабатывания и максимально высокая допустимая рабочая частота). Именно поэтому триггеры и регистры иногда называют также сверхоперативной памятью. Однако недостаток триггеров и регистров в том, что объем их внутренней памяти очень мал, они могут хранить только отдельные сигналы, биты (триггеры) или отдельные коды, байты, слова (регистры).

Триггер можно рассматривать как одноразрядную, а регистр – как многоразрядную ячейку памяти, которая состоит из нескольких триггеров, соединенных параллельно (обычный, параллельный регистр) или последовательно (регистр сдвига).

3.14.5.1 Триггеры.

Триггер представляет собой устройство с двумя устойчивыми состояниями. Устойчивым называется состояние, в котором устройство в отсутствии внешних воздействий может прибывать сколько угодно долго.

Термин триггер происходит от английского слова trigger – защелка, спусковой крючок, хотя для обозначения этой схемы в английском языке чаще употребляется термин flipflop – «хлопанье». Это звукоподражательное название электронной схемы указывает на ее способность почти мгновенно переходить («перебрасываться») из одного состояния в другое.

Так как триггер обладает двумя устойчивыми состояниями, причем эти состояния зависят от ранее воздействующих сигналов, то это позволяет сделать следующий вывод –

триггер является простейшим элементом памяти.

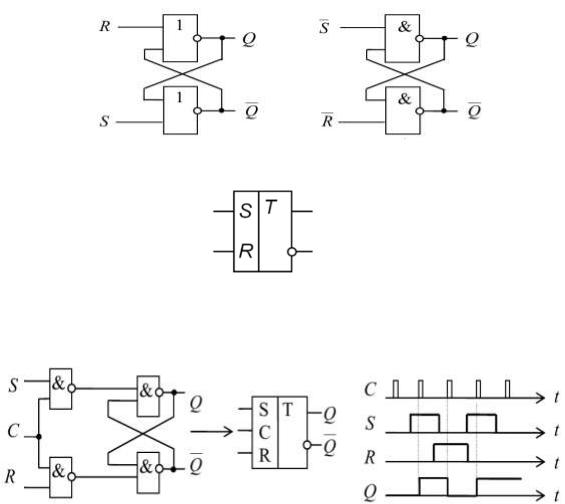

В основе любого триггера лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В общем случае триггер имеет два выхода: прямой и инверсный.

Состояние триггера принято определять по значению потенциала на прямом выходе. Если на прямом выходе имеем 1, то триггер находится в единичном состоянии (при этом потенциал инверсного выхода равен логическому нулю). В противном случае триггер находится в нулевом состоянии.

По способу записи информации триггеры могут быть асинхронными и синхронными. Триггер называют асинхронным, если сам сигнал, несущий информацию, вызывает его переключение. В синхронных (тактируемых) триггерах информация записывается при одновременном воздействии информационного сигнала и синхронизирующего (разрешающего) импульса.

В основу классификации триггеров может быть положен функциональный признак: по виду логического уравнения, характеризующего состояния входов и выходов триггера в момент времени до его срабатывания и после. В соответствии с функциональной классификацией различают RS-, D-, T- и JK-триггеры.

Закон функционирования триггера удобно отображать с помощью, так называемых таблиц переходов (состояний), в которых даются состояния входов и выходов триггера в момент времени до его срабатывания и после, при этом выходное состояние может обозначаться следующим образом:

0триггер находится в состоянии Q = 0

1триггер находится в состоянии Q = 1

Qсостояние триггера не изменяется при изменении информации на входе. состояние триггера изменяется

на противоположное при изменении информации на входе

Xнеопределенное состояние триггера – характеризуется тем, что в процессе действия информационного сигнала на входе логические уровни выходов триггера одинаковы, а после окончания действия информационного сигнала триггер может оказаться в состояние Q=1 или Q=0 с равной вероятностью

Триггером RS-типа называется логическое устройство с двумя устойчивыми состояниями, имеющее два информационных входа R и S, такие, что при S=1 и R=0 триггер принимает единичное состояние (Q=1), а при S=0, R=1 – нулевое (Q=0) и два выхода Q и не-Q. Вход S называется единичным, а R – нулевым, Выход Q называется прямым, не-Q – инверсным. Принцип работы RS-триггера можно задать таблицей переходов (таблицей состояний):

S |

R |

Q+ |

Режим работы |

|

|

|

|

0 |

0 |

Q |

Хранение |

|

|

|

|

0 |

1 |

0 |

Установка в 0 |

|

|

|

|

1 |

0 |

1 |

Установка в 1 |

|

|

|

|

1 |

1 |

Х |

Запрещенная |

|

|

|

|

|

|

|

комбинация |

Чтобы установить RS-триггер в нулевое |

|

|

|

состояние достаточно на вход R подать 1. Ес- |

|

|

|

|

|

|

|

|

|

|

ли 1 подать на вход S, то это переведет его в |

единичное состояние. Если на оба входа (R и S) подать 1, то состояние выходов определить невозможно. Триггер установится как ему заблагорассудится, т.е. в произвольное состояние. Схема асинхронного RS-триггера с прямым и инверсным управлением:

Условное обозначение RS-триггера:

Часто удобно, чтобы триггер менял состояние только в определенные моменты. Тактируемый (синхронный) RS-триггер может изменить свое состояние только с приходом тактового импульса на вход С.

Запрещенным является состояние CRS=1. При включении питания состояние триггера остается неопределенным. После совпадения единичных уровней на входах S и C триггер устанавливается в единичное состояние. При совпадения логических единиц на входах R и С триггер сбрасывается в нулевое состояние.

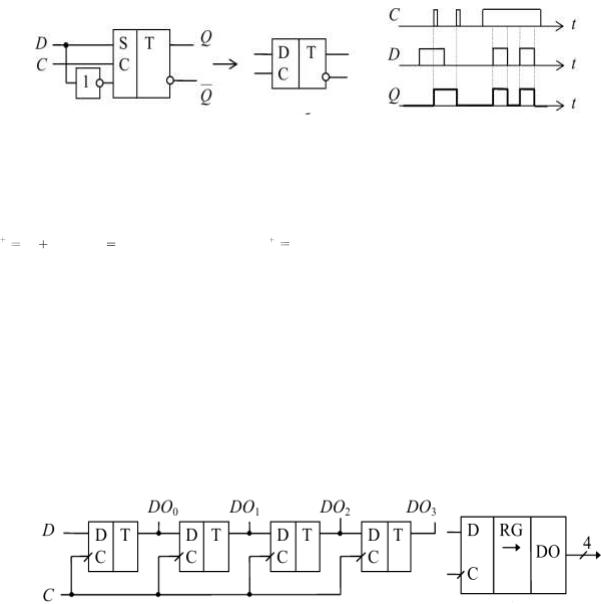

D-триггер (от английского Delay – задержка) имеет один информационный (D – Data – данные) и один тактируемый ( С – Clock – тактовая последовательность) входы. Такой триггер можно получить из RS-триггера, подав на R-вход инвертированный сигнал с S-входа. Из временных диаграмм можно увидеть, что при С=1 триггер работает как повторитель (Q=D), а при переходе сигнала на входе С от логической единицы к логическому нулю триггер запирается и переходит в режим хранения (защелкивает информацию со входа D). В отличие от RS-триггера, D-триггер не имеет запрещенного состояния.

Работу синхронных триггеров можно также описать функциями переходов. Функции переходов синхронных триггеров описывают состояние триггера Q+ после прихода очередного тактового импульса как логическую функцию входных сигналов и исходного состояния триггера Q до прихода тактового импульса.

|

Так функции переходов RS-триггеров выглядят следующим образом: |

|||

|

|

|

|

|

Q |

S Q R , R S 0 . Для D-триггеров Q |

D . |

||

3.14.5.2 Регистры.

Регистры представляют собой цепочки триггеров и предназначены для записи, хранения, сдвига и считывания из них двоичной информации (полубайта, байта и т. д.). Различают регистры сдвиговые (со сдвигом вправо, влево и реверсивные), с параллельной загрузкой, универсальные, кольцевые и файловые.

Регистры содержатся в различных вычислительных узлах компьютера – процессоре, периферийных устройствах и т.д.

Регистры сдвига строятся на D-триггерах с динамическим управлением. Тактовые входы объединяются, вход D первого триггера служит для приема информации, а входы D последующих подключаются к прямым выходам предыдущих.

За четыре такта по входу C последовательную информацию с входа D можно преобразовать в параллельную на выходах DO0 – DO3.

Регистры памяти с параллельной загрузкой также чаще строят на D-триггерах, объединяя их тактовые входы. Совокупность регистров, используемых ЭВМ для запоминания программы работы, исходных и промежуточных результатов называется оператив-

ной памятью.

3.14.6.Технологии производства цифровых микросхем.

Все современные ЭВМ строятся на микропроцессорных наборах, основу которых составляют большие и сверхбольшие интегральные схемы (ИС). Технологический принцип разработки и производства интегральных схем действует уже более четверти века. Он заключается в циклическом послойном изготовлении частей электронных схем по циклу программа-рисунок-схема. По программам на напыленный фоторезисторный слой наносится рисунок будущего слоя микросхемы. Затем рисунок протравливается, фиксируется, закрепляется и изолируется от новых слоев. На основе этого создается пространственная твердотельная структура.

Степень микроминиатюризации, размер кристалла ИС, производительность и стоимость технологии напрямую определяются типом литографии. До настоящего времени до-

минирующей оставалась оптическая литография, т.е. послойные рисунки на фоторезисторе микросхем наносились световым лучом. Дальнейшие достижения в микроэлектронике связываются с электронной (лазерной), ионной и рентгеновской литографией. Это позволяет выйти на размеры 0,25, 0,18 и даже 0,08мкм.

В настоящее время основой построения всех микросхем является КМОП-техноло- гия (комплиментарные схемы, т.е. совместно использующие n- и р-переходы в транзисторах со структурой металл-окисел-полупроводник). Кроме того широко распространена технология ТТЛ (транзисторно-транзисторная логика, где транзисторы используются как для выполнения логических функций (например, И, ИЛИ), так и для усиления выходного сигнала).

У ТТЛ уровень нуля равен 0,4 В, уровень единицы – 2,4 В. У логики КМОП, уровень нуля очень близок к нулю вольт, уровень единицы – примерно равен напряжению питания. Кроме различий в уровнях сигнала, типы логики различаются также по энергопотреблению, по скорости (предельной частоте), нагрузочной способности, и т.д.

Цифровые схемы рекомендуется строить, используя микросхемы только одного типа логики. Это связано именно с различиями в логических уровнях цифровых сигналов. Тип логики выбирают, в основном по параметрам скорости (рабочей частоты), энергопотребления и стоимости.

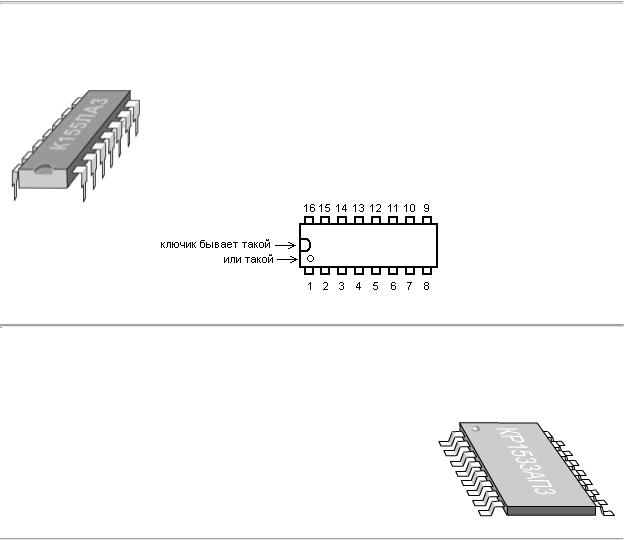

Микросхемы выпускаются в различных корпусах. Наиболее распространены следующие виды корпусов:

DIP

(Dual Inline Package )

Обычный «тараканчик». Ножек в корпусе может быть 8, 14, 16, 20, 24, 28, 32, 40, 48 или 56. Расстояние между выводами (шаг) – 2,5 мм (отечественный стандарт) или 2,54 мм (зарубежный). Ширина выводов около 0,5 мм Нумерация выводов – на рисунке (вид сверху). Чтобы определить нахождение первой ножки, нужно найти на корпусе «ключик».

SOIC

(Small Outline Integral Circuit)

Планарная микросхема – то есть ножки припаиваются с той же стороны платы, где находится корпус. При этом, микросхема лежит брюхом на плате. Количество ножек и их нумерация – такие же как у DIP. Шаг выводов – 1,25 мм (отечественный) или 1,27 мм (зарубежный). Ширина выводов

– 0,33...0,51

PLCC

(Plastic J-leaded Chip Carrier)

Квадратный (реже – прямоугольный) корпус. Ножки расположены по всем четырем сторонам, и имеют J -образную форму (концы ножек загнуты под брюшко).

Микросхемы либо запаиваются непосредственно на плату (планарно), либо вставляются в панельку. Количество ножек – 20, 28, 32, 44, 52, 68, 84. Шаг ножек – 1,27 мм Ширина выводов – 0,66...0,82 Нумерация выводов – первая

ножка возле ключа, увеличение номера против часовой стрелки:

TQFP

(Thin Quad Flat Package)

Нечто среднее между SOIC и PLCC. Квадратный корпус толщиной около 1мм, выводы расположены по всем сторонам. Количество ножек – от 32 до 144. Шаг – 0,8 мм. Ширина вывода – 0,3...0,45 мм. Нумерация – от скошенного угла (верхний левый) против часовой стрелки.