Лекции

.pdf

x 0 x1 x 0 x 2 x1 x 2 ( x 0 x1 ) ( x 0 x 2 ) ( x1 x 2 ) ( x 0 x1 ) ( x 0 x 2 ) ( x1 x 2 )

( x 0 x1 ) ( x 0 x 2 ) ( x1 x 2 ) (( x 0 x1 ) ( x 0 x 2 )) ( x1 x 2 )

( ( x 0 x1 ) ( x 0 x 2 ) ) ( x1 x 2 ) ( x 0 x1 ) ( x 0 x 2 ) ( x1 x 2 )( x 0 x1 ) ( x 0 x 2 ) ( x 0 x1 ) ( x 0 x 2 ) ( x1 x 2 ).

3.11. Типы цифровых устройств.

Одно цифровое устройство может состоять из нескольких более простых цифровых устройств. Часто эти составные элементы называют блоками, модулями, узлами, частями. Если объединяются несколько сложных цифровых устройств, то говорят уже о цифровых системах, комплексах, установках. Связь между входными и выходными сигналами может быть различной.

Под комбинационным цифровым устройством (КЦУ) понимается цифровое уст-

ройство, обеспечивающее преобразование совокупности N входных цифровых сигналов в M выходных, при этом состояние выходных сигналов в данный момент времени определяется состоянием входных сигналов в этот же момент времени. Иными словами, КЦУ «не помнит» предыстории поступления сигналов на его входы. Правила функционирования КЦУ определяются реализуемыми ими функциями алгебры логики.

Цифровое устройство называется последовательностным (ПЦУ), если его выходные сигналы Y зависят не только от значений входных сигналов X в данный момент времени, но и от значений входных сигналов, поступивших в предшествующие моменты времени. Иными словами, ПЦУ должно отслеживать последовательность поступления входных сигналов для формирования результата на своем выходе. Отсюда очевиден термин «последовательностное».

3.12. Анализ и синтез комбинационных вычислительных схем.

3.12.1.Задача синтеза. Этапы конструирования логического устройства.

Синтез (конструирование) КЦУ предусматривает построение структурной схемы устройства, т.е. определение состава необходимых логических элементов и соединений между ними, при которых обеспечивается преобразование входных цифровых сигналов в выходные в соответствии с заданными условиями работы устройства. В процессе синтеза обычно подразумевается необходимость минимизации аппаратных затрат на реализацию устройства. Рассмотрим синтез КЦУ с одним выходом. Задача синтеза логического устройства состоит из следующих этапов:

1.Построение таблицы истинности по заданным условиям работы проектируемого узла (т.е. по соответствию его входных и выходных сигналов).

2.Запись логической функции в виде СДНФ по таблице истинности.

3.Построение минимизированной логической формулы и при необходимости ее преобразование с помощью законов и тождеств алгебры логики в заданном базисе.

4.Составление функциональной схемы проектируемого узла по формуле логической функции.

Впроцессе реализации ЛФ на элементах, входящих в состав определенной серии микросхем, часто приходится решать задачу преобразования ЛФ с целью представления

еев функциях другой функционально полной системы. Для построения современных ЭВМ обычно применяются системы интегральных элементов, у которых с целью большей

унификации в качестве базовой логической схемы используется одна из схем: {И–НЕ}, {ИЛИ–НЕ} или {И, ИЛИ, НЕ}.

Для построения логической схемы в базисе {И, ИЛИ, НЕ} рекомендуется сначала реализовать операции над отдельными переменными (отрицание), затем конъюнкции и в последнюю очередь – дизъюнкции. Логические элементы, предназначенные для выполнения логических операций, указанных в логической функции, нужно располагать, начиная от входа в порядке, указанном в булевом выражении.

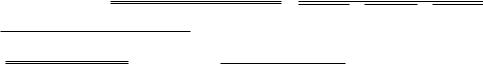

Рис.4.12.1. Синтез устройства в базисе {И, ИЛИ, НЕ}

На практике широко применяются КЦУ, имеющие несколько выходов. Функционирование КЦУ с M выходами описывается аналогичным количеством переключательных функций, над каждой из которых в процессе синтеза выполняются действия, описанные выше. Задача синтеза схемы с M выходами отличается от задачи синтеза M схем с одним выходом тем, что при решении необходимо исключить дублирование и уменьшить количество синтезируемых функций.

3.13.Задача анализа. Переход от логической схемы к логической функции.

Задача анализа требует по заданной схеме определить функцию f, реализованную данной схемой. При решении задачи анализа следует придерживаться следующей последовательности действий:

1.Заданная схема разбивается по ярусам.

2.Начиная с последнего, выходы каждого элемента обозначаются проиндексированными функциями в зависимости от яруса, к которому относится элемент.

3.Записываются выходные функции каждого элемента в виде формул в соответствии с введенными обозначениями.

4.Производится подстановка одних выходных функций через другие, используя входные переменные.

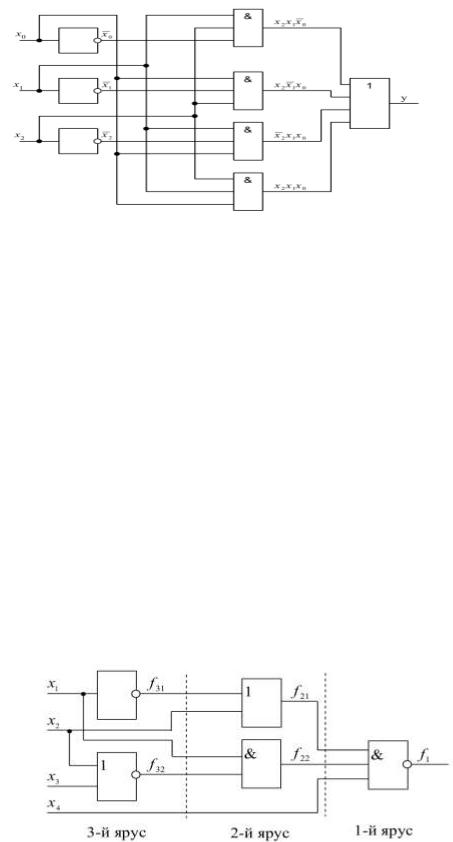

5.Записывается получившаяся булева функция через входные переменные. Пример: По заданной логической схеме (рис. 4.13.1) составить булеву функцию.

Рис.4.13.1. Переход от логической схемы к логической функции

Согласно приведенной выше последовательности действий, произведем разбиение схемы на ярусы. Пронумеровав получившиеся ярусы, введем обозначения для каждой выходной функции (рис. 4.13.1). Запишем все функции, начиная с 1-го яруса:

|

|

|

1. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f1 |

f 2 1 f 2 2 x 4 . |

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

2. |

f 2 1 |

|

f 3 1 |

x 2 , |

|

f 2 2 |

f 3 2 x1 . |

|

|

|

|

||||||

|

|

|

3. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f 3 1 |

|

x1 , |

f 3 2 |

|

x 2 |

x3 . |

|

|

|

|

|||||||

|

Теперь |

запишем |

все |

функции, |

подставляя входные |

переменные |

x1 , ..., x 4 : |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

В |

итоге, |

получим |

выходную |

функцию: |

|||

f 2 1 |

x1 |

x 2 , |

f 2 2 |

|

x1 ( x 2 |

x3 ). |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f |

x1 ( x1 |

x 2 )( x 2 |

|

x3 ) x 4 . |

|

|

|

|

|

|

|

|

|

|||||||

3.14. Основные цифровые логические схемы.

Реализация цифровых устройств предполагает выбор определенных логических элементов из заданного набора и их соединение таким образом, чтобы обеспечивалась зависимость цифровых выходных сигналов от входных с заданными правилами функционирования. При этом широко используются интегральные комбинационные логические микросхемы малой степени интеграции, образующие основу элементной базы цифровой электроники.

3.14.1. Цифровые компараторы.

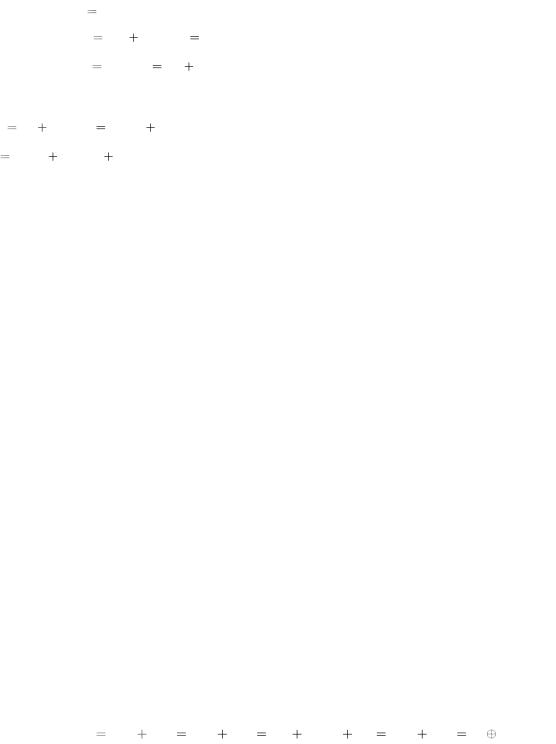

Цифровые компараторы выполняют сравнение двух чисел, заданных в двоичном коде. Они могут определять равенство двух двоичных чисел a и b с одинаковым количеством разрядов либо вид неравенства a>b, или a<b. Цифровые компараторы имеют три выхода. Компараторы обычно строятся как поразрядные, т.е. на основе поразрядных операций над одноименными разрядами обоих слов.

Цифровые компараторы применяются для выявления нужного числа (слова) в цифровых последовательностях, для выполнения условных переходов. Таблица истинности отражает логику работы одноразрядногого компаратора при сравнении двух векторов a и b. Функция Y1 – есть результат сравнения ai>bi, Y2 – ai=bi и Y3 – ai<bi.

|

|

|

ai |

|

bi |

|

Y1= fai<bi |

|

Y2= fai=bi |

|

Y3= fai>bi |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

0 |

|

0 |

|

1 |

|

|

|

0 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

1 |

|

0 |

|

|

|

0 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

0 |

|

0 |

|

0 |

|

|

|

1 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

0 |

|

1 |

|

|

|

0 |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Так как Y2 ai bi ai bi |

ai bi |

a i bi ( a i |

bi )( a i bi ) |

a i bi a i bi a i bi , то схема од- |

||||||||||||||||||||||

норазрядного компаратора представляет собой структуру логического элемента «исключающее ИЛИ–НЕ».

Рис.4.14.1. Одноразрядный компаратор и его обозначение

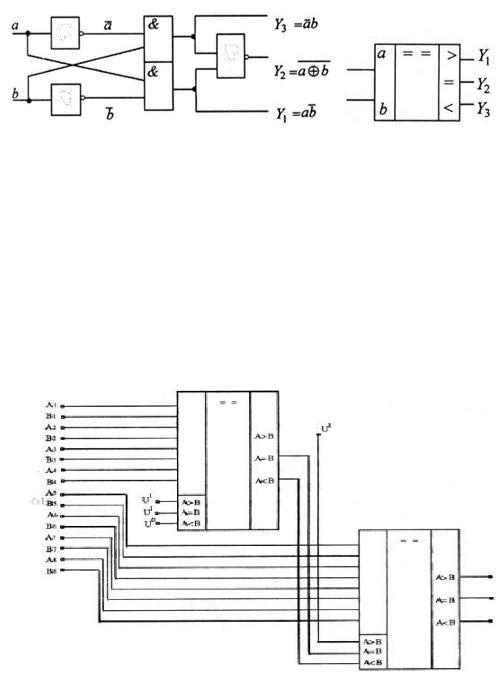

Если попарно равны между собой все разряды двух n-разрядных двоичных чисел, то равны и эти два числа a и b. Неравенство a>b обеспечивается (например, для четырехраз-

рядного числа) в четырех случаях: (a4 >b4) ИЛИ (a4=b4 И a3 >b3) ИЛИ (a4=b4 И a3=b3 И a2 > b2) ИЛИ (a4=b4 И a3=b3 И a2=b2 И a1 > b1), где ai и bi – разряды чисел a и b. Очевидно, что если поменять местами ai и bi то будет выполняться неравенство a< b.

Для наращивания входов в компаратор добавляют расширяющие входы a<b, a=b, a>b, что позволяет наращивать разрядность обоих чисел. Для этого компараторы соединяют каскадно (последовательно) (рис. 4.14.2). При этом соединении выходы a=b и a<b предыдущей микросхемы (младшие разряды) подключают к соответствующим входам последующей. На входы a<b, a=b, a>b микросхемы младших разрядов подают соответственно потенциалы U0, U1 и U1. В последующих микросхемах на входах a>b поддерживают потенциал логической единицы U1.

Рис. 4.14.2. Каскадное соединение компараторов

3.14.2. Сумматоры.

Как мы уже знаем, любая арифметическая операция в ЭВМ сводится к операции сложения и сдвига. Сумматором называют устройство, выполняющее операцию сложения цифровых кодов двух чисел. Сумматоры входят в состав АЛУ (арифметико-логичес- кого устройства). Пусть нам необходимо сложить двоичные числа А и В. Через P и S обозначим первую и вторую цифру суммы: A + B = PS. Вспомнив таблицу сложения двоичных чисел получим таблицу истинности для функций P и S:

Слагаемые |

Перенос |

Сумма |

|

|

|

|

|

A |

B |

P |

S |

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

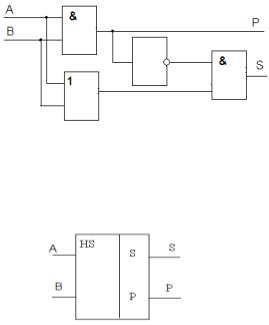

Эта таблица позволяет построить схему:

Рис. 4.14.3.Схема одноразрядного полусумматора

Синтезированное цифровое устройство называется одноразрядным полусумматором. Это устройство служит для сложения разрядов двух чисел без учета переноса из предыдущего разряда и имеет два входа (два суммируемых разряда) и два выхода (суммы и переноса). Условное обозначение одноразрядного полусумматора:

Рис. 4.14.4.Условное обозначение одноразрядного полусумматора

Логика работы одноразрядного сумматора на три входа или полного сумматора приведена в таблице, где А, В – суммируемые двоичные цифры , P0 – перенос из младшего разряда, S – образующаяся сумма данного разряда и осуществляет перенос P в следующий старший разряд. Одноразрядный двоичный сумматор на три входа и два выхода называ-

ется полным одноразрядным сумматором.

|

|

Перенос |

|

|

Слагаемые |

из младшего |

Сумма |

Перенос |

|

|

|

разряда |

|

|

|

|

|

|

|

A |

B |

P0 |

S |

P |

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

0 |

0 |

1 |

1 |

0 |

|

|

|

|

|

0 |

1 |

0 |

1 |

0 |

|

|

|

|

|

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

1 |

0 |

0 |

1 |

0 |

|

|

|

|

|

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

1 |

1 |

0 |

0 |

1 |

|

|

|

|

|

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

Теперь можно построить схему полного одноразрядного сумматора с учетом переноса из младшего разряда.

Полный одноразрядный сумматор можно построить из двух полусумматоров HS и логического элемента ИЛИ :

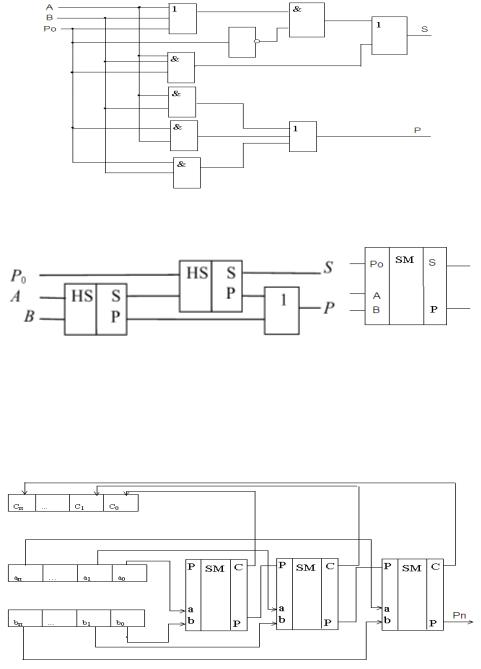

Сумматор выполняет сложение многозначных двоичных чисел. Он представляет собой последовательное соединение одноразрядных двоичных сумматоров, каждый из которых осуществляет сложение в одном разряде. Если при этом возникает переполнение разряда, то перенос суммируется с содержимым старшего соседнего разряда.

На рисунке показано, как из N сумматоров можно составить устройство для сложения двух N-разрядных двоичных кодов, это схема многоразрядного сумматора.

3.14.3. Дешифраторы и шифраторы.

Процесс обработки сигналов с помощью электронных устройств чаще всего начинается с кодирования этих сигналов. В цифровых устройствах, в том числе в ЭВМ, используются различные двоичные и двоично-десятичные коды. Шифраторы и дешифраторы применяются в устройствах, преобразующих один вид кода в другой.

3.14.3.1 Дешифраторы.

Микросхема дешифратора часто предназначена для активизации одного из нескольких устройств, присоединенных к ее выходам. Дешифраторы широко используются в ЭВМ для выбора информации по определенному адресу, для расшифровки кода операции, для перевода двоичных цифр в десятичные.

Унитарным (позиционным) кодом (unitary code) называется двоичный код фиксированной длины, содержащий только одну 1 – прямой (только один 0 – инверсный) уни-

тарный код. Длина кода определяется количеством кодируемых объектов, а значение кода положением 1 или 0 в кодовом слове.

Пример: Кодирование цифр 0-5.

Цифра |

Прямой |

Инверсный |

|

код |

код |

||

|

|||

0 |

000001 |

111110 |

|

1 |

000010 |

111101 |

|

2 |

000100 |

111011 |

|

3 |

001000 |

110111 |

|

4 |

010000 |

101111 |

|

5 |

100000 |

011111 |

Дешифратором (декодером) называется цифровое устройство комбинационного типа, осуществляющее преобразование n-разрядного двоичного кода в m-разрядный унитарный код (или иной).

Размерностью дешифратора называется условная запись n×m, где n – количество входов дешифратора, m – количество его выходов. Если количество выходов дешифратора равно m=2n, т.е. количеству возможных кодовых комбинаций, то такой дешифратор называется полным. Дешифратор, у которого при n входах число выходов меньше 2n, называется неполным. Другое название дешифратора – декодер. Принцип работы полного двухразрядного дешифратора рассмотрим на примере его таблицы истинности.

|

Входы |

|

|

|

Выходы |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

B |

|

Y0 |

Y1 |

Y2 |

Y3 |

|

|

|

||

|

0 |

0 |

1 |

|

0 |

0 |

0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

0 |

1 |

0 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

0 |

0 |

1 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

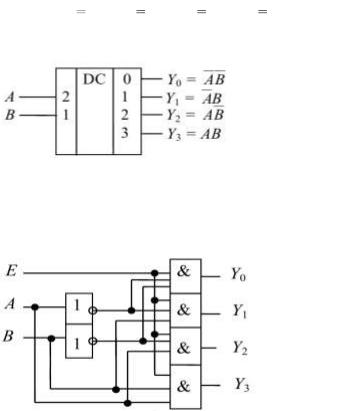

Соответствующие ЛФ имеют вид:Y0 |

|

A B , Y1 |

AB , Y2 A B , Y3 A B . Условное обоз- |

|||||||||

начение двухразрядного дешифратора приведено на рис. 4.14.5.

Рис.4.14.5. Условное графическое обозначение полного дешифратора «2x4»

Часто схему дешифратора дополняют разрешающим (стробирующим) входом E. Работа дешифратора запрещена (на всех выходах устройства логический 0) при E=0. Схема такого дешифратора приведена на рис. 4.14.6.

Рис.4.14.6. Схема полного дешифратора «2x4» со стробирующим сигналом

В интегральном исполнении выпускаются различные структуры дешифраторов, в которых имеются 2, 3 или 4 входа. В одном корпусе может быть несколько дешифраторов.

При объединении (каскадировании) информационных и стробирующих входов, как это показано на рис. 4.14.7, получают дешифратор 3-х разрядного двоичного кода. Входные сигналы дешифрируются первым дешифратором (при V1=0 и V2=1, т.е. при х3=0, или вторым (при V1=1 и V2=0, т.е. при х3=1) дешифратором.

Рис.4.14.7. Схема каскадирования дешифраторов «2x4»

Распространенным выходным устройством, отображающим десятичные числа, является семисегментный индикатор. Его работой управляет дешифратор, преобразующий BCD-код в семисегментный код. Семь сегментов индикатора обозначены буквами от а до g (рисунок 4.14.8). Способ изображения десятичных цифр от 0 до 9 показан на рисунке

4.14.8 б.

Рис.4.14.8. Семисегментный индикатор

Семисегментный код необходим для отображения на цифровых индикаторах значений цифр от 0 до 9.

Цифра |

Двоичный код |

|

Семисегментный код |

|

|

|

||||||

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

2 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

1 |

3 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

0 |

0 |

1 |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

5 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

6 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

1 |

1 |

9 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

0 |

1 |

1 |

Ниже показано изображение такого дешифратора на логических схемах и его подключение к семисегментному светодиодному индикатору.

Рис.4.14.9. Дешифратор семисегментного кода и его подключение к индикатору

Дешифратор кроме своего основного функционального назначения – преобразователя двоичного кода в унитарный, может быть использован для реализации логических функций. Поясним сказанное на следующем примере. Пусть требуется получить некото-

рую логическую функцию: y x3 x 2 x1 x3 x 2 x1 x3 x 2 x1 .

Каждое из слагаемых представляет собой минтерм заданной логической функции 3-х двоичных переменных. В то же время трехбуквенные минтермы реализуются на выходах дешифратора «3x8». Следовательно, реализация функции сводится к объединению соответствующих выходов дешифратора.

Аналогичным образом на базе дешифратора «3x8» может быть реализована любая иная логическая функция трех аргументов. Для реализации произвольного вида логических функций четырех аргументов требуется дешифратор «4x16» и т.д. По этой причине дешифратор может рассматриваться как универсальный логический элемент.

3.14.3.2 Шифраторы.

Шифраторы выполняют задачу обратную той, которую выполняют дешифраторы: появление логической единицы (логического нуля) на определенном входе приводит к появлению соответствующей кодовой комбинации на выходе. Другое название шифра-

тора – кодер.

Шифраторы широко применяются в устройствах автоматики, особенно в устройствах ввода/вывода информации. Например, клавиатура ввода содержит клавиши с десятичными цифрами, буквенный алфавит, а при нажатии клавиши позиционный код должен преобразоваться в двоичный. Также как и дешифраторы, шифраторы бывают полными и неполными. Работа полного шифратора на четыре входа задается следующей таблицей истинности:

|

Входы |

|

Выходы |

||

|

|

|

|

|

|

x1 |

x2 |

x3 |

x4 |

y0 |

y1 |

1 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

0 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

0 |

0 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

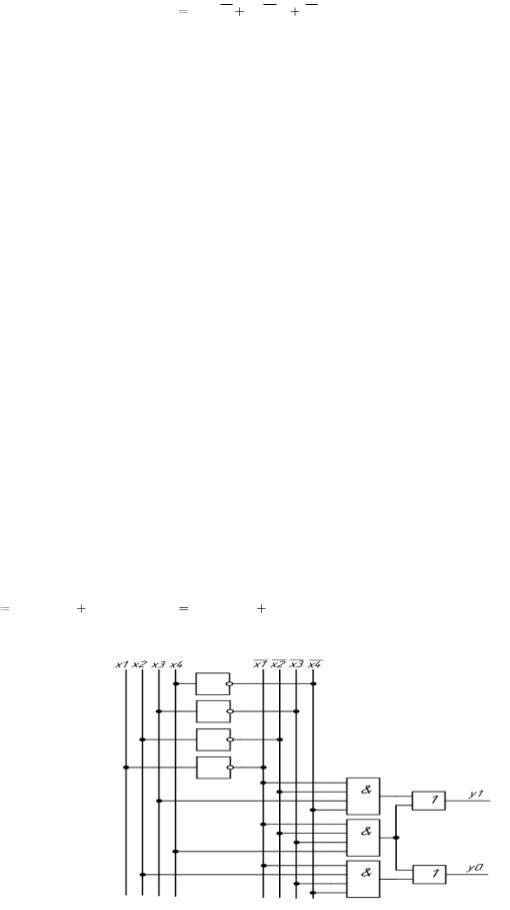

Состояния входов таблицы истинности содержат только по одному единичному элементу. Другие комбинации входов недопустимы. Соответствующие ЛФ имеют вид:

|

|

|

|

|

|

|

|

|

|

|

|

|

y 0 |

x 1 x 2 x 3 x 4 x 1 x 2 x 3 x 4 , y1 |

x 1 x 2 x 3 x 4 x 1 x 2 x 3 x 4 . Схема такого шифратора приведена |

||||||||||

на рис. 4.14.10. Эта схема может быть упрощена.

Рис.4.14.10. Схема полного шифратора «4x2»

Условное обозначение двухразрядного шифратора приведено на рис. 4.14.11.

Рис.4.14.11. Условное обозначение полного шифратора «4x2»

3.14.4. Мультиплексоры и демультиплексоры.

Термином «мультиплексирование» называют процесс передачи данных от нескольких источников по общему каналу, а устройство, осуществляющее на передающей стороне операцию сведения данных в один канал, принято называть мультиплексором. Подобное устройство способно осуществлять временное разделение сигналов, поступающих от нескольких источников, и передавать их в канал (линию) связи друг за другом в соответствии со сменой кодов на своих адресных входах.

На приемной стороне обычно требуется выполнить обратную операцию – демультиплексирование, т.е. распределение порций данных, поступивших по каналу связи в последовательные моменты времени, по своим приемникам. Эту операцию выполняет демультиплексор. Совместное использование мультиплексора и демультиплексора для передачи данных от n источников к n приемникам по общей линии.

Параллельные данные одного из цифровых устройств с помощью мультиплексора преобразуются в последовательные информационные сигналы, которые передаются по одному проводу. На выходе демультиплексора эти последовательные сигналы снова группируются в параллельные данные.

3.14.4.1 Мультиплексоры.

Мультиплексор – это комбинационное цифровое устройство, которое соединяет (коммутирует) один из нескольких информационных входных сигналов с одним общим выходом. Входы мультиплексора делятся на две группы: информационные и управляющие (адресующие).

Так, например мультиплексор восьми каналов содержит восемь информационных

входов: D0, D1, D2, D3, D4, D5, D6, D7. Три адресных входа: А0, А1, А2 и один синхронизирующий (стробирующий) вход V. Пример обозначения мультиплексора на схемах показан

на рисунке.

В зависимости от комбинации адресных сигналов А0, А1, А2 он обеспечивает коммутацию одного из восьми информационных входных сигналов Di на общий выход F. Ну-