Методические указания к выполнению лабораторной работы № 1

На практике при обмене информацией между микроконтроллером и внешними устройствами часто возникает задача преобразования параллельного кода в последовательный и обратно. Задача преобразования, например, параллельного кода в последовательный возникает в случае передачи информации по каналу связи к удаленному объекту. Решать задачу обратного преобразования требуется при обработке информации. Часто встречаются ситуации, когда установка дополнительных аппаратных преобразователей типа мультиплексоров или демультиплексоров неоправданна. В этом случае задачи преобразования кодов может выполнять и сам микроконтроллер.

В рамках данной лабораторной

работы предстоит составить программу для преобразования формата данных.

Важно заметить, что в случае преобразования параллельного кода в последовательный исходный параллельный байт считывается из внутренней памяти данных по адресу регистра, указанного в задании, и передается в последовательном виде разрядом одного из портов. В случае преобразования последовательного кода в параллельный исходный последовательный код поступает на один из входов счета внешних событий (Т0 или Т1) и после преобразования записывается во внутреннюю память данных по адресу регистра, указанного в задании.

При передаче информации в последовательном коде, часто пользуются стартстопным (асинхронным) режимом обмена данными. Суть стартстопного режима обмена данными заключается в том, что передача последовательного байта предваряется посылкой старт-бита, а завершается выдачей стоп-бита. Эти биты при последующей обработке не используются, а служат только метками начала и окончания передачи.

Формат данных при передаче и приеме в последовательном коде представлен на рисунке 1, формат данных в параллельном коде представлен на рис.2.

Как

следует из рисунка 1, передача байта в

последовательном коде осуществляется

следующим образом. Сначала передается

сигнал уровня «лог.0», который является

стартовым битом. После передачи стартового

бита начинает передаваться последовательный

байт. Когда все 8 бит последовательного

байта переданы, осуществляется передача

сигнала «лог.1», который является стоповым

битом. Каждый бит последовательного

кода передается в течение времени

![]() .

.

Считывание

битов осуществляется в середине их

передачи, поэтому когда начинается

передача стартового бита осуществляется

выдержка времени

![]() .

Считывание последующих битов осуществляется

через каждые

.

.

Считывание последующих битов осуществляется

через каждые

.

Как

следует из рисунка 2 при использовании

параллельного кода все биты передаются

одновременно. В этом случае каждый бит

передается по специально выделенному

разряду (![]() ).

Каждый разряд имеет свой вес.

).

Каждый разряд имеет свой вес.

Рассмотрим способ преобразования формата данных.

Одним

из вариантов преобразования параллельного

кода в последовательный и обратно

является способ, реализованный в таких

устройствах преобразования кодов, как

сдвиговые регистры. Разрядность сдвиговых

регистров при преобразовании кодов

подбирается равной длине преобразуемого

кодового слова. Операция преобразования

параллельного кода в последовательный

(последовательного кода в параллельный)

осуществляется сдвиговыми регистрами

в течение числа тактов

![]() ,

равного длине преобразуемого кода.

,

равного длине преобразуемого кода.

Так

как большинство логических и арифметических

операций микроконтроллер выполняет в

АЛУ, то наиболее просто осуществить

преобразование именно там. АЛУ

микроконтроллера содержит регистр-аккумулятор

![]() ,

вспомогательный регистр

,

вспомогательный регистр

![]() ,

предназначенный для выполнения

двухоперандных действий, схему

формирования признаков слова состояния

программы

,

предназначенный для выполнения

двухоперандных действий, схему

формирования признаков слова состояния

программы

![]() и десятичный корректор

и десятичный корректор

![]() .

Программно доступными являются сам

регистр-аккумулятор

и триггер переноса

.

Программно доступными являются сам

регистр-аккумулятор

и триггер переноса

![]() из схемы формирования признаков.

из схемы формирования признаков.

Так как в рамках задачи преобразования кодов нас, в первую очередь, интересует возможность сдвига данных в аккумуляторе , то более подробно остановимся на ней.

Сдвиг данных регистр-аккумулятор может осуществлять вправо и влево. Кроме того, возможен циклический сдвиг данных вправо и влево через триггер переноса (смотри табл.4 и рис.3). Что касается триггера переноса , то его состояние можно программно анализировать, а также изменять.

Преобразование кодов в микроконтроллере можно организовать следующими способами:

Преобразование параллельного кода в последовательный можно осуществлять путем циклических сдвигов данных в регистре-аккумуляторе , причем сдвиг необходимо осуществлять с переносом . В каждом цикле сдвига необходимо производить анализ содержимого триггера переноса и в соответствии с его значением выдавать в требуемый разряд заданного порта копию содержимого триггера переноса.

Преобразование последовательного кода в параллельный можно осуществлять путем записи в триггер переноса копии сигнала, воспринимаемого счетным входом микроконтроллера. В каждом такте входного сигнала необходимо обеспечить сдвиг содержимого регистра-аккумулятора с участием переноса.

Преобразование кодов в обоих случаях будет занимать число циклов, равное разрядности аккумулятора.

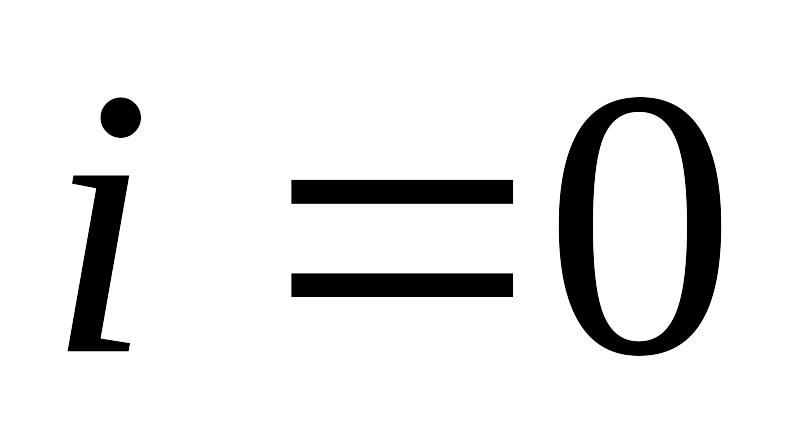

Учитывая

то, что при передаче (приеме) информации

используется асинхронный способ, такты

преобразования кодового слова должен

сформировать сам микроконтроллер. В

связи с этим наряду с рядом других

проблем возникает такая важная проблема

как определение длительности выдержки

уровней сигнала на выходах (входах)

микроконтроллера. Время выдержки

![]() должно быть достаточным для правильного

восприятия кода внешними устройствами

и при необходимости должно согласовываться.

Для микроконтроллера длительность

выдержки сигнала на входах (выходах) не

может быть меньше времени выполнения

одной команды

должно быть достаточным для правильного

восприятия кода внешними устройствами

и при необходимости должно согласовываться.

Для микроконтроллера длительность

выдержки сигнала на входах (выходах) не

может быть меньше времени выполнения

одной команды

![]() .

.

![]() (1)

(1)

Условие (1) является ограничением минимального времени выдержки сигнала на портах микроконтроллера.

Минимальная длительность выдержки сигнала не может быть меньше времени его восприятия самым медленным устройством канала. Так как зачастую микроконтроллер является наиболее быстродействующим устройством в системе, то длительность сигнала в канале связи обычно существенно больше времени выполнения команды. Последнее обстоятельство должно учитываться при формировании сигналов микроконтроллером для внешних устройств и при восприятии им внешних сигналов. В противном случае возникают искажения информации. Например, при приеме внешнего сигнала, длительность которого существенно больше длительности выполнения микроконтроллером команды, возникает многократное считывание одного и того же бита информации. Для того чтобы исключить подобные ситуации необходимо обеспечить необходимую периодичность опроса микроконтроллером портов, а также выдачи сигналов в порты.

Обеспечить необходимую периодичность обмена данными с внешними устройствами можно в случае, если частота синхронизации микроконтроллера выше частоты сигнала в канале связи.

Время выполнения отдельной операции микроконтроллером К1816ВЕ48 фиксировано и зависит от длительности синхронизирующего сигнала. Поэтому необходимую задержку времени можно обеспечить программным путем. Наиболее распространенный способ программной задержки, основан на задании в теле программы локальных циклов, заполненных пустыми операциями, либо операциями, выполняемыми за максимальное число циклов.

Примерный вид локального цикла представлен на рисунке 4. Цифрами 1 и 11 обозначены метки начала и окончания цикла, цифрой 3 обозначена метка условного перехода.

Работает

цикл следующим образом. Запуск цикла

происходит в тот момент, когда

микроконтроллер считывает команду,

размещенную в памяти программ в ячейке,

соответствующей началу цикла (1). Далее

из памяти данных считывается начальный

индекс цикла (2). После этого осуществляется

проверка превышения числом уже выполненных

циклов

заданного числа 0 (счет выполненных

циклов осуществляется в обратном

порядке). Так как начальный индекс цикла

больше заданного числа 0, то по ветке

«нет» начинается последовательное

выполнение (![]() )

команды, обеспечивающих заданное время

выполнения цикла. Предпоследней командой,

выполняемой в ветке «нет», (9) производится

декрементирование индекса цикла

(уменьшение индекса на единицу). После

этого следует команда безусловного

перехода по метке (3). Снова производится

проверка превышения уже выполненным

числом циклов заданного числа

,

и выполнение команд из ветки «нет»

(5)-(10). Так продолжается до тех пор, пока

очередная проверка (4) не обнаружит, что

условие

)

команды, обеспечивающих заданное время

выполнения цикла. Предпоследней командой,

выполняемой в ветке «нет», (9) производится

декрементирование индекса цикла

(уменьшение индекса на единицу). После

этого следует команда безусловного

перехода по метке (3). Снова производится

проверка превышения уже выполненным

числом циклов заданного числа

,

и выполнение команд из ветки «нет»

(5)-(10). Так продолжается до тех пор, пока

очередная проверка (4) не обнаружит, что

условие

![]() стало истинным. В этом случае происходит

условный переход по метке конца локального

цикла.

стало истинным. В этом случае происходит

условный переход по метке конца локального

цикла.

Приведенный на рисунке 4 алгоритм цикла изображен в общем виде, тогда как при написании программного кода число операций, в течение которых выполняется отдельный элемент алгоритма, может быть более одной. Это происходит потому, что помимо операций преобразования данных микроконтроллер выполняет также ряд вспомогательных операций, например, таких как операции пересылки данных между узлами, операции «очистки» регистров и т.д (число операций зависит от микроконтроллера). Как следует из анализа системы команд (см. табл.4) большинство операций преобразования данных, таких как присвоение значений переменным, декрементирование, инкрементирование выполняется в регистре-аккумуляторе. Так как в процессе выполнения программы регистр-аккумулятор должен хранить различные данные, которые зависят от операции, выполняемой АЛУ, то большинство переменных, хранится в регистрах памяти данных. Значит для выполнения, например операции условного перехода, требуется предварительно переслать в аккумулятор из памяти данных анализируемое число (команда MOV A, Rn), и только затем произвести сравнение содержимого аккумулятора с нулем и осуществить переход по метке (команда JZ add).

С учетом вспомогательных операций подробный алгоритм цикла задержки имеет вид, представленный на рисунке 5. Как видно из приведенного алгоритма один раз в начале цикла выполняются операции (2)-(4), затем раз операции (6)-(13) и при выходе из цикла еще раз команды (6), (7). Само тело цикла заполнено пустыми операциями NOP. Формула для определения длительности указанного цикла имеет вид:

![]() ,

мкс

,

мкс

где

![]() - число команд, расположенных вне цикла;

- число команд, расположенных вне цикла;

- число циклов;

![]() - число команд в цикле.

- число команд в цикле.

Если известно

необходимое время задержки

,

число f, n

и время выполнения команд цикла

![]() ,

тогда число циклов может быть определено

по формуле:

,

тогда число циклов может быть определено

по формуле:

.

.

В примере, приведенном на рисунке 5 число циклов определяется с учетом того, что:

требуемое время задержки составляет

;

;

-

команды (2)-(4), (6), (7);

-

команды (2)-(4), (6), (7); -

команды (6)-(13).

-

команды (6)-(13).

Поэтому формула для данного цикла имеет вид:

.

.

Чтобы воспользоваться приведенной формулой для расчета необходимо определить время выполнения команд.

Для определения времени выполнения команды необходимо учесть следующее. Работа микроконтроллера является циклической, поэтому в качестве временной характеристики, широко используемой для расчетов, является время машинного цикла. Микроконтроллер МК1816ВЕ48 имеет фиксированное время машинного цикла, длительность которого в 15 раз превышает длительность сигнала синхронизации. С учетом этого, длительность машинного цикла может быть определена из частоты синхронизации по следующей формуле:

![]() ,

мкс

,

мкс

где

![]() - частота синхронизации микроконтроллера

МК1816ВЕ48, МГц.

- частота синхронизации микроконтроллера

МК1816ВЕ48, МГц.

Команды микроконтроллеров могут выполняться за один либо несколько машинных циклов. Из таблицы 4 видно, что в системе команд микроконтроллера присутствуют команды, выполняемые за один и за два машинных такта. Тогда длительность выполнения команды может быть определена как:

![]() ,

мкс

,

мкс

где N – время выполнения команды (количество машинных циклов).

Так как микроконтроллер имеет стек, то локальный цикл, при необходимости его организации в нескольких местах программы, может быть реализован в виде подпрограммы, вызываемой по команде «CALL» (см. систему команд – табл. 4).

Подпрограмму следует заканчивать командой «RET».

При организации цикла в виде подпрограммы необходимо помнить, что стек выделяется в памяти данных из регистров под номерами 8-23. Поэтому необходимо исключить их использование при обмене данными и хранении переменных.

Алгоритм преобразования параллельного кода в последовательный приведен на рисунке 6. Номерами 1 и 17 обозначены соответственно метки начала и окончания алгоритма. Номерами 6 и 11 обозначены метки переходов.

Работает

алгоритм следующим образом. Сначала

производится передача из регистра

памяти данных

![]() в регистр-аккумулятор

преобразуемого кодового слова (2). Далее

в регистр хранения числа циклов

преобразования параллельного кода в

последовательный заносится число циклов

преобразования

(3).

После этого микроконтроллер формирует

в заданном разряде требуемого порта

в регистр-аккумулятор

преобразуемого кодового слова (2). Далее

в регистр хранения числа циклов

преобразования параллельного кода в

последовательный заносится число циклов

преобразования

(3).

После этого микроконтроллер формирует

в заданном разряде требуемого порта

![]() старт-бит «лог.0» и выдерживает его в

течение времени

(5).

Программная задержка (5) представляет

собой цикл и оформлена в виде подпрограммы.

После выполнения программной задержки

(5) производится сдвиг содержимого

аккумулятора вправо с переносом на один

разряд. В следующей операции (8)

осуществляется проверка состояния

триггера переноса. В случае, если триггер

находится в состоянии «лог.0», разряд

формирует сигнал «лог.0». В противном

случае разряд

старт-бит «лог.0» и выдерживает его в

течение времени

(5).

Программная задержка (5) представляет

собой цикл и оформлена в виде подпрограммы.

После выполнения программной задержки

(5) производится сдвиг содержимого

аккумулятора вправо с переносом на один

разряд. В следующей операции (8)

осуществляется проверка состояния

триггера переноса. В случае, если триггер

находится в состоянии «лог.0», разряд

формирует сигнал «лог.0». В противном

случае разряд

![]() формирует сигнал «лог.1».

формирует сигнал «лог.1».

После того, как на выходе порта микроконтроллера сформирован первый разряд последовательного кода, микроконтроллер осуществляет его выдержку в течение времени (12). Выдержка времени обеспечивается путем обращения микроконтроллера к подпрограмме задержки. Сразу после окончания программной задержки производится декрементирование содержимого регистра (вычитание единицы) (13) и проверка числа оставшихся циклов преобразования (14). Так как после выполнения первого цикла преобразования остается еще 7 циклов, то по ветке «нет» происходит условный переход микроконтроллера к строке начала цикла преобразования (3). Циклы преобразования продолжаются до тех пор, пока в результате проверки оставшегося числа циклов не окажется, что осталось 0 циклов. В этом случае микроконтроллер начинает выполнять программу по ветке «да». Соответственно, сразу же в порту формируется стоп-бит «лог.1» (15). Стоп-бит на выходе выдерживается в течение времени программной задержки , после чего микроконтроллер завершает выполнение программы.

Примечание: Сформировать логическую единицу в заданном разряде порта можно путем выполнения операции логического сложения содержимого порта с маской, содержащей единицу именно в этом разряде. Операцию сложения содержимого порта с маской проще всего реализовать командой ORL Pp, #d.

Сформировать логический ноль в заданном разряде порта можно путем выполнения операции логического умножения содержимого порта с маской, содержащей ноль именно в этом разряде. Операцию логического умножения содержимого порта с маской проще всего реализовать командой ANL Pp, #d

Алгоритм преобразования последовательного кода в параллельный приведен на рисунке 7. Номерами 1 и 18 обозначены соответственно метки начала и окончания алгоритма. Номерами 2, 8 и 13 обозначены метки переходов.

Работает алгоритм следующим образом. При запуске алгоритма начинает выполняться модуль задержки времени, организованный на элементах (3)-(5). Этот модуль необходим для того, чтобы распознать старт-бит, а также обеспечить считывание информации из счетного входа микроконтроллера в середине интервала выдержки на нем сигнала (см.рис.1). Пока на счетном входе микроконтроллера поддерживается сигнал «лог.1» цикл (3) замкнут по ветке «нет», соответственно микроконтроллер находится в ожидании начала передачи. Как только на входе порта появляется сигнал «лог.0», условие ветвления (3) становится истинным и начинается выполнение программной задержки (4) (способ выполнения программной задержки требуемой длительности рассмотрен ранее). По истечении времени программной задержки производится повторная проверка уровня сигнала на счетном входе. Если за произошла на счетном входе появился сигнал «лог.1», то считается, что принят не старт-бит и по ветке «нет» (5) происходит возврат микроконтроллера в режим ожидания начала приема. Если же по истечении на счетном входе сохранился уровень «лог.0», то считается - старт-бит принят и осуществляется переход к выполнению ветки «да» (5).

Сначала

в счетчик битов, организованный на

регистре

![]() ,

записывается длина принимаемого кодового

слова (по заданию длина кодового слова

равна 8). Преобразуемое кодовое слово

будет записываться в регистр-аккумулятор,

поэтому следующим шагом производится

его очистка (7) и подготовка к записи.

Далее устанавливается начальное значение

разряда переноса

.

Начальное значение принято равным

«лог.0». После выполнения перечисленных

команд запускается программная задержка

.

Данная задержка времени требуется для

того, чтобы завершилась передача на

счетный вход микроконтроллера текущего

бита и началась передача следующего.

По истечении

производится проверка состояния счетного

входа

,

записывается длина принимаемого кодового

слова (по заданию длина кодового слова

равна 8). Преобразуемое кодовое слово

будет записываться в регистр-аккумулятор,

поэтому следующим шагом производится

его очистка (7) и подготовка к записи.

Далее устанавливается начальное значение

разряда переноса

.

Начальное значение принято равным

«лог.0». После выполнения перечисленных

команд запускается программная задержка

.

Данная задержка времени требуется для

того, чтобы завершилась передача на

счетный вход микроконтроллера текущего

бита и началась передача следующего.

По истечении

производится проверка состояния счетного

входа

![]() (11). Если на вход поступает «лог.1» то

происходит переход «нет» (11) и в разряд

переноса также заносится «лог.1», в

противном случае происходит переход

«да» и содержимое разряда переноса не

меняется.

(11). Если на вход поступает «лог.1» то

происходит переход «нет» (11) и в разряд

переноса также заносится «лог.1», в

противном случае происходит переход

«да» и содержимое разряда переноса не

меняется.

После получения в разряде переноса копии сигнала, поступающего на счетный вход микроконтроллера, производится сдвиг содержимого регистра-аккумулятора с учетом переноса вправо (14). Первый бит последовательного кода оказывается преобразованным в младший разряд параллельного кода. Соответственно, число оставшихся преобразований, которое хранится в регистре , уменьшается на единицу (декрементируется) (15). После декрементирования осуществляется проверка числа оставшихся циклов преобразования (16). Так как после первого цикла преобразования число, хранящееся в регистре , отлично от нуля (хранится число 7), то осуществляется переход по ветке «нет» на метку (8) и начинается следующий цикл преобразования.

Преобразование последовательного кода в параллельный заканчивается, когда при очередной проверке (16) число оставшихся преобразований оказывается равным 0. В этом случае происходит переход по ветке «да» (16), что означает окончание преобразования кодов. При этом в аккумуляторе оказывается принятый байт в параллельном коде. По команде (17) этот параллельный код из аккумулятора пересылается в один из регистров памяти данных, где он будет храниться в параллельном коде. На этом алгоритм преобразования последовательного кода в параллельный заканчивается.

Примечание: В начале программы требуется активизировать счетный вход микроконтроллера командой STRT CNT.

В системе команд микроконтроллера К1816ВЕ48 нет команды установки в триггере переноса значения «лог.1», в то же время ему доступны операции установки «лог.0» и инверсии. Поэтому в случае, если требуется получить «лог.1» требуется указывать следующую последовательность команд (см. табл.4):

CLR C /запись в триггер переноса «лог.0»/

CPL C /инвертирование содержимого триггера переноса,

Перед выполнением работы, для исключения потери данных, необходимо составить вспомогательную таблицу, в которой каждому регистру памяти данных сопоставить хранимую им переменную (см. табл.2)

Все переменные должны быть представлены в двоичном формате, допускается сокращенная запись переменных в шестнадцатеричном формате.

Программа оформляется в виде таблицы, аналогичной таблице 3. (таблица 3 составлена по алгоритму рисунке 5.)

Таблица 2

Регистр памяти данных |

Хранимая переменная |

|

Число циклов преобразования |

|

Число циклов выполнения пустых операций в цикле задержки |

.. |

.. |

Таблица 3

Метки |

Команды |

Комментарии |

Время выполнения команды, циклы |

Начало |

|

/очистка аккумулятора/ |

1 |

|

|

/очистка регистра

|

1 |

|

|

/запись числа циклов преобразования/ |

2 |

5 |

|

/передача числа циклов преобразования из в аккумулятор |

1 |

tзад

Моменты опроса

входа Тi

t,мкс

t,мкс

t,мкс

t,мкс

t,мкс

t,мкс

t,мкс

t,мкс

t,мкс

1

1

0

1

0

0

1

0

1

1

0

1

0

0

1

0

i0

i1

i2

i3

i4

i5

i6

i7

tзад/2

Стартовый бит

Стоповый бит

tзад

tзад

tзад

tзад

tзад

tзад

tзад

tзад

tзад

Рис.1 - Формат данных

при передаче и приеме в последовательном

коде

tзад

Рис.2 - Формат данных в параллельном

коде

А7

А6

А5

А4

А3

А2

А1

А0

С

А7

А6

А5

А4

А3

А2

А1

А0

(а)

(б)

А7

А6

А5

А4

А3

А2

А1

А0

С

(в)

А7

А6

А5

А4

А3

А2

А1

А0

(г)

Рис. 3

(а) - сдвиг данных регистра-аккумулятора вправо с участием триггера переноса (б) - сдвиг данных регистра-аккумулятора вправо без участия триггера переноса

(г) - сдвиг данных регистра-аккумулятора влево с участием триггера переноса

(в) - сдвиг данных регистра-аккумулятора влево без участия триггера переноса

9

1

2

3

4

5

6

7

8

11

Рис. 4 - Алгоритм организации локального

цикла

да

нет

I

II

10

1

2

3

4

5

6

7

8

9

да

нет

10