- •Материалы для студента

- •Модуль 8. Цифровая промышленная электроника § 8.1. График выполнения задания Модуля 8

- •§ 8.2. Теоретические вопросы Модуля 8

- •§ 8.3. Задание Модуля 8

- •Сделать выводы. § 8.4. Варианты схем к заданию Модуля 8

- •§ 8.5. Компьютерное моделирование №1 к заданию Модуля 8

- •§ 8.6. Краткая теория и примеры Модуля 8

- •Транзисторно-транзисторная логика (ттл)

- •§ 8.7. Примеры тестов

§ 8.5. Компьютерное моделирование №1 к заданию Модуля 8

Цель компьютерного моделирования: Изучение элементной базы цифровой электроники и методов их анализа Изучение методов компьютерного моделирования и исследования логических элементов с помощью компьютерных моделей.

Содержание компьютерного эксперимента:

Моделирование является проверкой составленной таблицы истинности заданной вариантом схемы.

Исследуемая схема содержит источник постоянной ЭДС, поэтому измерительные приборы должны находиться в режиме измерения постоянных величин (DC).

Используемые в моделировании логические микросхемы, находятся в библиотеке элементов (Misc Digital) Элемент 2-И – в библиотеке элементов обозначается AND2, 2-И–НЕ – обозначается NAND2, 2-ИЛИ – обозначается OR2 и 2-ИЛИ–НЕ – обозначается NOR2.

Выполнение компьютерного моделирования:

Необходимо вынести элементы электрической цепи из библиотек Misc Digital

Собрать виртуальную электрическую схему с логическими элементами согласно заданию и подключить вольтметр к выходным зажимам схемы.

Активизировать схему с помощью ключа в верхнем правом углу. Снять экспериментально таблицу истинности схемы.

Сравнить результаты моделирования с данными расчёта п. 1 задания модуля.

Сделать выводы.

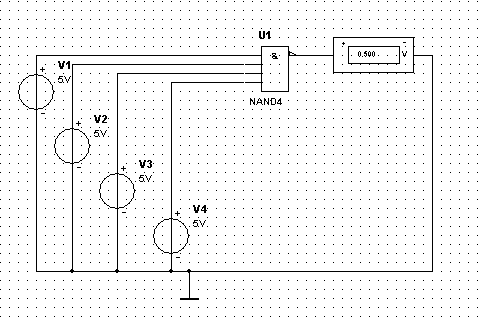

В качестве примера приведена модель схемы для определения таблицы истинности для элемента 4–И–НЕ. В модели используется минимальное количество измерительных приборов. Для определения всех напряжений в данной схеме достаточно одного вольтметра. Одна точка цепи должна быть обязательно заземлена.

Из компьютерной модели видно, что на все входа подано напряжение 5 В (Логическая единица). На выходе логического элемента 4–И–НЕ напряжение 0,5 В (напряжение логического нуля). Записываем данные в таблицу истинности.

Вход |

Выход |

|||

Х1 |

Х2 |

Х3 |

Х4 |

У1 |

1 |

1 |

1 |

1 |

0 |

Изменяем входные напряжения, получаем таблицу истинности:

Вход |

Выход |

|||

Х1 |

Х2 |

Х3 |

Х4 |

У1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |