Перечень заданий по вариантам:

Номер задания студент выбирает по последней цифре шифра. Цифре 1 соответствует задание 1, цифре 2 – задание 2 и т.д. Цифре 0 соответствует задание 10.

ЗАДАНИЕ 1

Разработать электрические структурную, функциональную и принципиальную схемы трехдиапазонного цифрового вольтметра постоянного напряжения с однополярными диапазонами входного напряжения (00,1) В, (01) В, (010) В, разрядностью десятичного индикатора – 2 разряда и классом точности 1. Обновление показаний – 0,5 с. При разработке выбрать однодиапазонный АЦП в интегральном исполнении с выходным двоичным кодом. Переключение диапазонов реализовать механическими переключателями. Внимание: микросхему К572ПВ2 и аналогичные, представляющие функционально законченные вольтметры с семисегментными выходными кодами, использовать нельзя.

Рекомендации по выполнению задания 1:

Для реализации требуемых функций и характеристик вольтметра очевидна следующая структура: входной нормирующий усилитель с переключаемым коэффициентом усиления АЦП в интегральном исполнении и выходным двоичном кодом преобразователь двоичного кода в двоично-десятичный преобразователь двоично-десятичного кода в семисегментный двухразрядный семисегментный индикатор. Для синхронизации работы АЦП в структуру устройства необходимо включить тактовый генератор.

Входной нормирующий усилитель удобнее всего реализовать на операционном усилителе по схеме неинвертирующего усилителя с переключаемыми путем механического переключателя сопротивлениями обратной связи. Расчеты номиналов резисторов обратной связи привести в пояснительной записке. Схема таких каскадов подробно рассматривалась в курсе «Электроника и микропроцессорная техника ч.1». [1: стр. 46-51]. Из заданных диапазонов входных напряжений очевидно, что коэффициенты усиления каскада нормирующего усилителя должны составить 1, 10 и 100 в случае использования АЦП с входным напряжением 10 В. В случае использования АЦП с другим входным напряжением, коэффициенты усиления необходимо пересчитать. К выбору операционного усилителя жесткие требования можно не предъявлять в силу невысокого класса точности согласно исходным данным.

В качестве АЦП следует выбрать микросхему с разрядностью выходного двоичного кода, достаточного для индикации на двухразрядном индикаторе десятичных цифр в диапазоне от 00 до 99. Можно использовать АЦП и большей разрядности, но в этом случае часть младших разрядов можно не использовать (например, микросхемы К572ПВ1, К1107ПВ2, К1108ПВ1, 1523ПВ2 [3: стр. 398-418]).

Для синхронизации работы микросхемы АЦП в схеме может потребоваться тактовый генератор, если это предусмотрено типовой схемой включения микросхемы АЦП (например, для АЦП последовательных приближений К572ПВ1). Частота тактового генератора выбирается согласно рекомендациям по типовой схеме включения выбранного АЦП. Также тактовый генератор может использоваться для инициализации начала цикла преобразования, когда на вход «запуск» АЦП необходимо подавать импульсы синхронизации с периодом 0,5 с согласно исходным данным. В качестве тактовых генераторов можно использовать схему мультивибратора на основе логических элементов и RC-цепи [1: стр. 73-82; 2: стр. 43-64].

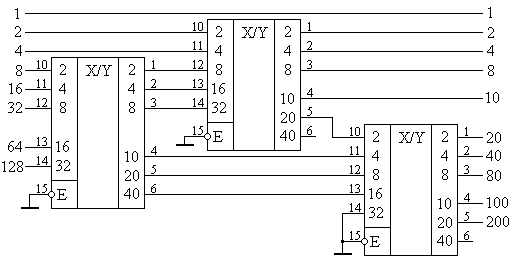

Преобразователь двоичного кода с выхода АЦП в двоично-десятичный удобно реализовать на микросхеме 155ПР7. На рис.1 приводится типовая схема включения микросхемы для реализации преобразователя двоичного кода в двоично-десятичный чисел до 255 [4: стр. 105-107].

В качестве преобразователя двоично-десятичного кода в семисегментный можно выбрать любую микросхему семисегментного преобразователя, например, из микросхем К155ПП5, К155ИД9, КР514ИД1, КР514ИД2 [4: стр. 90-92]. В зависимости от выбранной микросхемы преобразователя необходимо выбрать индикаторы с разъединенными анодами или разъединенными катодами. К размерам знакоместа индикатора требования не предъявляются. В случае использования полупроводниковых индикаторов в схему необходимо ввести резисторы, ограничивающие ток через сегменты. Расчеты номиналов резисторов привести в пояснительной записке.

Рис.1. Схема преобразователя двоичного кода в двоично-десятичный чисел до 255.

ЗАДАНИЕ 2

Разработать электрические структурную, функциональную и принципиальную схемы цифрового вольтметра постоянного напряжения с биполярным диапазоном входного напряжения (010) В, разрядностью десятичного индикатора – 2 разряда и классом точности 1. Обновление показаний – 0,5 с. При разработке использовать однополярный АЦП в интегральном исполнении, отрицательные значения входных напряжений выпрямлять в положительные при помощи схемы прецизионного двухполупериодного выпрямителя. На индикаторе отображать отрицательные значения напряжений с помощью знака «-». Внимание: микросхему К572ПВ2 и аналогичные, представляющие функционально законченные вольтметры с семисегментными выходными кодами, использовать нельзя.

Рекомендации по выполнению задания 2:

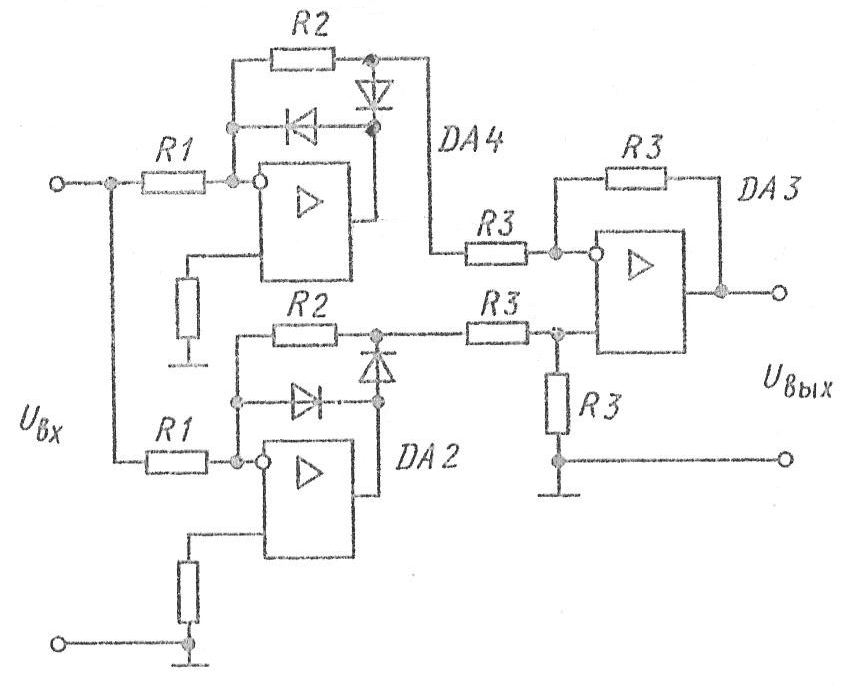

В качестве рекомендаций по выполнению данного задания можно предложить описанные выше рекомендации по выполнению задания 1. Отличие заключается в формировании аналоговой части схемы. Поскольку в данном задании диапазон входного напряжения один, то нет необходимости включения в схему нормирующего усилителя с переключаемым коэффициентом усиления. Однако по заданию диапазон входного напряжения биполярный, а при разработке требуется использовать однополярный АЦП. Для того, чтобы иметь возможность оцифровывать обе полярности входного напряжения, отрицательные значения нужно выпрямить. Для этой цели в схеме необходимо применить прецизионный двухполупериодный выпрямитель на базе операционного усилителя и нелинейной обратной связи (рис.2) [5: стр. ].

Рис.2. Схема прецизионного двухполупериодного выпрямителя.

Коэффициент усиления схемы рис.2 определяется как отношение R2/R1. Исходя из входного напряжения выбранного АЦП необходимо рассчитать коэффициент усиления схемы и выбрать соответствующие номиналы резисторов R2 и R1. Выбор номинала резистора R3 должен удовлетворять условию R3>>R2. Для определенности можно выбрать R3=10*R2. Так же как и в первом задании, к выбору операционных усилителей не следует предъявлять жесткие требования из-за невысокого класса точности проектируемого вольтметра.

Далее выпрямленное напряжение подается на вход однополярного АЦП. Остальная цифровая часть схемы ничем не отличается от схемы задания 1.

Для формирования знака входного напряжения нужно установить факт подачи на вход положительной или отрицательной амплитуды напряжения. Для этого достаточно входное напряжение сравнить с нулевым уровнем с помощью аналогового компаратора. С выхода компаратора сигнал необходимо подать на сегмент индикатора, отображающего знак «-» через ограничительный резистор при необходимости.

ЗАДАНИЕ 3

Разработать электрические структурную, функциональную и принципиальную схемы цифрового милливольтметра постоянного напряжения, работающего по методу аналого-цифрового преобразования последовательных приближений, с диапазоном входного напряжения (01) В, разрядностью десятичного индикатора – 2 разряда и классом точности 1. Обновление показаний – 0,5 с. При разработке АЦП реализовать на логических микросхемах.

Рекомендации по выполнению задания 3:

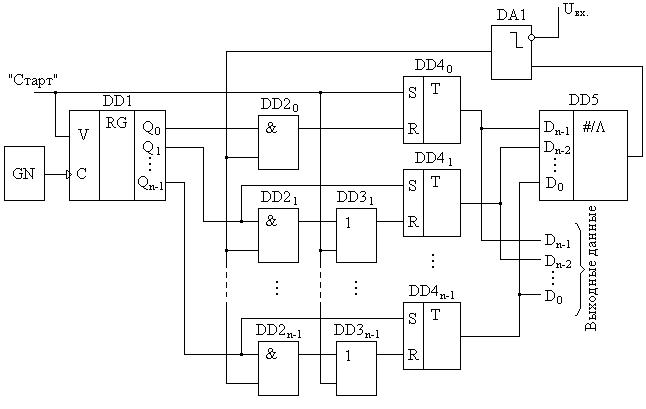

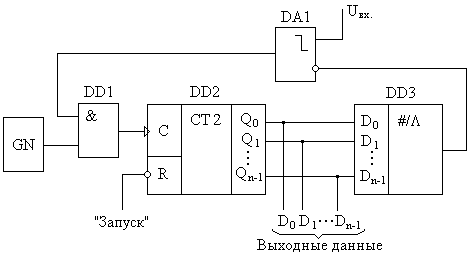

Функциональная схема, иллюстрирующая принцип аналого-цифрового преобразования последовательного приближения представлена на рис.3. Именно эту схему целесообразно заложить как основу блока аналого-цифрового преобразователя при проектировании вольтметра. Подробное описание схемы и временные диаграммы работы приводятся в [2: стр.203-207].

Рис.3. Схема АЦП последовательного приближения.

Для выбора элементной базы логических элементов АЦП можно воспользоваться [4: стр. 20-75]. ЦАП можно реализовать на основе интегральной микросхемы [3: стр. 398-418]. При выборе разрядности АЦП необходимо руководствоваться заданным классом точности и разрядностью выходного десятичного индикатора аналогично рекомендациям по выполнению задания 1. Дальнейшая структура цифровой части схемы повторяет структуру вольтметра задания 1 и содержит преобразователь двоичного кода в двоично-десятичный, преобразователь двоично-десятичного кода в семисегментный и узел индикаторов. Для синхронизации работы АЦП необходимо использовать генератор тактовых импульсов. Все рекомендации аналогичны рекомендациям по выполнению задания 1.

ЗАДАНИЕ 4

Разработать электрические структурную, функциональную и принципиальную схемы индикатора напряжения, работающего по методу аналого-цифрового преобразования параллельного действия, с диапазоном входного напряжения (010) В, разрядностью десятичного индикатора – 2 разряда и классом точности 5. Обновление показаний – 0,1 с. При разработке АЦП реализовать на логических микросхемах.

Рекомендации по выполнению задания 4:

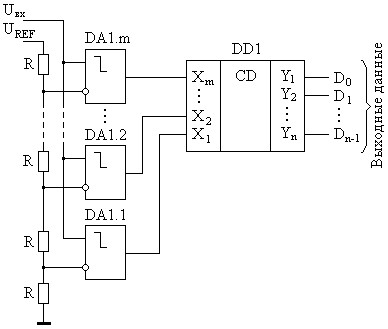

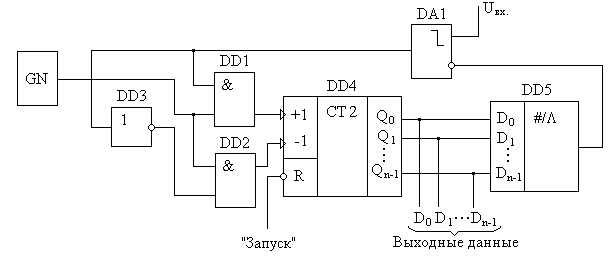

Функциональная схема, иллюстрирующая принцип аналого-цифрового преобразования последовательного приближения представлена на рис.4. Именно эту схему целесообразно заложить как основу блока аналого-цифрового преобразователя при проектировании вольтметра. Подробное описание схемы и временные диаграммы работы приводятся в [2: стр. 211-213].

Рис.4. Схема АЦП параллельного действия.

Для выбора элементной базы логических элементов АЦП можно воспользоваться [4: стр. 20-75]. Все рекомендации по проектированию индикатора напряжения аналогичны предыдущим вариантам. При невозможности подобрать микросхему шифратора на необходимое количество входов, шифратор необходимо реализовать на вентилях базовых логических элементов.

ЗАДАНИЕ 5

Разработать электрические структурную, функциональную и принципиальную схемы цифрового вольтметра постоянного напряжения, работающего по методу аналого-цифрового преобразования последовательного счета (развертывающего преобразования), с диапазоном входного напряжения (010) В, разрядностью десятичного индикатора – 3 разряда и классом точности 0,1. Обновление показаний – 0,5 с. При разработке АЦП реализовать на логических микросхемах.

Рекомендации по выполнению задания 5:

Функциональная схема, иллюстрирующая принцип аналого-цифрового преобразования последовательного счета представлена на рис.5. Именно эту схему целесообразно заложить как основу блока аналого-цифрового преобразователя при проектировании вольтметра. Подробное описание схемы и временные диаграммы работы приводятся в [2: стр. 197-200].

Рис.5. Схема АЦП последовательного счета.

Рекомендации по выполнению задания и выбора схемотехнических решений аналогичны рекомендациям по предыдущим заданиям. Отличие заключается в том, что по заданию требуется обеспечить достаточно высокий класс точности и трехразрядную десятичную индикацию показаний разрабатываемого вольтметра. Это влечет за собой организацию схемы АЦП большей разрядности, чем в предыдущих заданиях. Само по себе это трудностей не представляет. Однако большая разрядность двоичного кода потребует организации преобразователя двоичного кода в двоично-десятичный на большее количество разрядов. Следовательно, потребуется включение в пирамидальную структуру большего количества микросхем К155ПР7. Например, для организации преобразователя двоичного кода в двоично-десятичный чисел до 999 потребуется уже 6 микросхем К155ПР7. В данном случае можно избежать этого недостатка путем замены в структуре устройства двоично-десятичного преобразователя двоично-десятичным счетчиком, на вход которого будут поступать те же счетные импульсы, что и на двоичный счетчик DD2. Двоичный счетчик, таким образом, будет формировать двоичный код на ЦАП DD3 и будет иметь модуль счета 2n, а двоично-десятичный счетчик будет иметь модуль счета 10 в каждом десятичном разряде. Таким образом, выходы с двоично-десятичного счетчика можно будет подключить непосредственно на входы семисегментных преобразователей, к которым, в свою очередь, нужно будет подключить семисегментные индикаторы соответствующих десятичных разрядов. Быстродействие данного вольтметра не является высоким, поэтому для повышения разрядности двоичного и двоично-десятичного счетчиков можно организовать соединение отдельных микросхем счетчиков по последовательной схеме.

ЗАДАНИЕ 6

Разработать электрические структурную, функциональную и принципиальную схемы цифрового вольтметра постоянного напряжения, работающего по методу следящего аналого-цифрового преобразования, с диапазоном входного напряжения (010) В, разрядностью десятичного индикатора – 3 разряда и классом точности 0,1. Обновление показаний – 0,5 с. При разработке АЦП реализовать на логических микросхемах.

Рекомендации по выполнению задания 6:

Функциональная схема, иллюстрирующая принцип аналого-цифрового преобразования следящего типа представлена на рис.6. Именно эту схему целесообразно заложить как основу блока аналого-цифрового преобразователя при проектировании вольтметра. Подробное описание схемы и временные диаграммы работы приводятся в [2: стр. 200-203].

Рекомендации по выполнению задания и выбора схемотехнических решений аналогичны рекомендациям по заданию 5. Отличительной особенностью в данном случае является работа счетчиков в режиме как инкремента, так и декремента. Поэтому необходимо будет решить проблему наращивания разрядности реверсивных счетчиков. Сделать это можно путем соединения выходов «9», «0» двоично-десятичных счетчиков и «15», «0» двоичных счетчиков младших разрядов со счетными входами микросхем соответствующих счетчиков старших разрядов через стробирующие вентили И, аналогично подачи тактовых импульсов через вентили DD1 и DD2 рис.6.

Рис.6. Схема АЦП следящего преобразования.

ЗАДАНИЕ 7

Разработать электрические структурную, функциональную и принципиальную схемы восьмиканального коммутатора медленно менящихся аналоговых сигналов с индикацией номера канала на семисегментном индикаторе и с квазисенсорным управлением со следующими характеристиками: Uвх - 0…5 В, Rнагр – 5 кОм. Выбор номера коммутируемого канала осуществлять нажатием на одну из восьми кнопок. Номер коммутируемого канала на индикатор должен выводиться в диапазоне чисел от 1 до 8.

Рекомендации по выполнению задания 7:

Для реализации коммутатора предлагается следующая структура: клавиатура формирователь двоичного кода корректор двоичного кода восьмиканальный аналоговый коммутатор с цифровым управлением семисегментный преобразователь семисегментный индикатор.

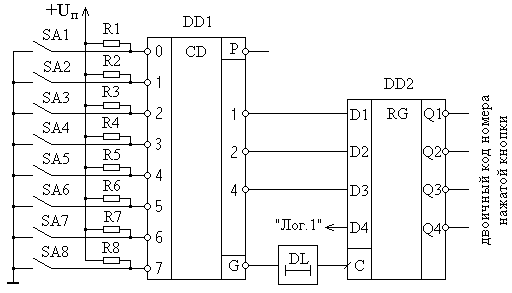

Узел клавиатуры по заданию должен содержать 8 кнопок, пронумерованных цифрами от 1 до 8. Формирователь двоичного кода номера канала должен обеспечить формирование двоичного кода, соответствующего номеру нажатой кнопки. Очевидно, что такой формирователь удобнее всего реализовать на основе восьмивходового шифратора. Двоичный код на выходах шифратора будет удерживаться до тех пор, пока будет нажата кнопка. Поскольку при выборе канала кнопки нажимаются кратковременно, а двоичный код должен удерживаться в течении всего времени работы устройства, его необходимо запомнить. Для этих целей в схему формирователя кода необходимо включить регистр, который будет запоминать двоичный код при каждом нажатии одной из восьми кнопок. Схема узла клавиатуры и формирователя двоичного кода, предлагаемая для реализации в данном задании, представлена на рис. 7.

Рис.7. Схема узла клавиатуры и формирователя двоичного кода.

Обычно шифраторы ТТЛ-типов имеют инверсные входы и выходы. Именно с такими входами и выходами он показан на схеме (элемент DD1). Поэтому, чтобы двоичный код с выхода всего узла был прямым, регистр DD2 в этой схеме также должен быть выбран с инверсными выходами. Выбрать микросхем шифраторов и регистров можно в [4: стр. 82-82, 57-75]. Для избежания эффекта дребезга контактов, двоичный код с выхода шифратора необходимо запомнить с некоторой задержкой после нажатия кнопки, когда все переходные процессы в схеме завершатся. Для этих целей можно использовать схему задержки DL, которую можно реализовать на RC-цепи и логических элементах [1: стр. 77-79; 2: стр. 43-52]. В качестве времени задержки можно задать интервал в 5 мс, что обычно достаточно для завершения переходных процессов по коммутации контактов. Следует учитывать особенности выхода «G» признака подачи входного сигнала шифратора DD1 и входа записи «C» регистра DD2 с тем, чтобы правильно согласовать уровни сигналов и правильно сформировать цепь задержки. В нашем случае выход «G» инверсный, а вход «C» - прямой динамический. Т.е. сигнал с выхода «G» необходимо подать на вход схемы задержки через инвертор.

Двоичный код с выхода узла формирователя кода необходимо подать на адресные входы микросхемы восьмиканального аналогового коммутатора. В качестве такого коммутатора можно выбрать КМОП-мультиплексор К561КП2, который успешно используется и для коммутации аналоговых сигналов [4: стр. 194-199]. Необходимо проверить согласование уровней сигналов ТТЛ и КМОП и необходимого напряжения источника питания микросхемы К561КП2 для возможности коммутации входного напряжения в указанном по заданию диапазоне. Также необходимо проверить возможность нагрузки микросхемы К561КП2 требуемым по заданию сопротивлением нагрузки.

По заданию требуется отобразить на индикаторе номер канала из ряда значений 1…8. Поскольку с выхода формирователя двоичного кода код будет формироваться в диапазоне значений от 0 до 7, то его нужно скорректировать путем прибавления единицы. Реализовать корректор кода можно с помощью четырехразрядного сумматора, на вход числа A которого будет подаваться двоичный код с выхода формирователя, а на вход числа B – логическая единица в самом младшем разряде. Полученный скорректированный код необходимо преобразовать в семисегментный и отобразить на семисегментном индикаторе. Реализация преобразователя двоичного кода в семисегментный и согласование его с семисегменым индикатором аналогична рекомендациям к заданию 1.

ЗАДАНИЕ 8

Разработать электрические структурную, функциональную и принципиальную схемы делителя частоты последовательности прямоугольных импульсов с выбираемым коэффициентом деления со следующими характеристиками: Уровни логических напряжений входа и выхода совместимы с ТТЛ, частота входных импульсов (01) МГц, скважность импульсов - 2, Rнагр - 2кОм, диапазон задаваемого коэффициента деления - 001 - 999 с шагом 1. Выбор коэффициента деления реализовать кнопочным управлением с индикацией на трехразрядном семисегментном индикаторе следующим образом: с помощью трех кнопок, удерживая каждую из них в нажатом положении в течении определенного времени, методом последовательного перебора цифр в каждом разряде выбирать нужное значения коэффициента деления.

Рекомендации по выполнению задания 8:

Для реализации заданных функций делитель частоты предлагается организовать по следующей структуре: формирователь кода коэффициента деления, состоящий из клавиатуры, тактового генератора, схемы передачи тактовых импульсов, счетчика для формирования кода коэффициента деления, делитель частоты семисегментный преобразователь семисегментные индикаторы.

Узел формирователя кода отвечает за формирование двоично-десятичного кода задаваемого с помощью кнопок коэффициента деления. По заданию требуется коэффициент деления формировать в диапазоне чисел от 001 до 999 с шагом 1. Каждый десятичный разряд этих чисел задается путем удержания одной из трех кнопок в течение определенного времени, пока цифры будут «перелистываться» в порядке возрастания. В момент совпадения с нужной цифрой кнопка будет отпускаться. Очевидно, поскольку коэффициент деления и его индикация должны быть представлены в десятичном формате, узел формирователя кода должен содержать три идентичных канала, построенных на двоично-десятичных счетчиках. Тактовые импульсы с выхода тактового генератора с частотой, достаточной для визуального контроля смены показаний на индикаторах (для конкретности можно выбрать 3 Гц), должны поступать на входы двоично-десятичных счетчиков только в том случае, если кнопка установки кода соответствующего разряда нажата. Для передачи импульсов на входы счетчиков только при нажатии кнопки можно использовать схему И, на один вход которой будет поступать последовательность тактовых импульсов, а на другой – логическая единица, формируемая нажатием кнопки. Для подавления эффекта дребезга узел клавиатуры можно построить на базе асинхронных RS-триггеров [4: стр.215].

Сформированный двоично-десятичный код необходимо отобразить на семисегментных индикаторах. Для этого он должен быть преобразован семисегментными преобразователями и в преобразованном виде подан на три семисегментных индикатора. Выбор семисегментных преобразователей и индикаторов аналогичен рекомендациям задания 1.

Для построения узла самого делителя частоты можно воспользоваться двоично-десятичными счетчиками со входами параллельной записи предварительного кода. Тогда, подав на входы параллельной записи двоично-десятичных счетчиков сформированный код коэффициента деления и подачей импульса с выхода переполнения со счетчика сотен на входы параллельной записи счетчиков всех трех разрядов, можно будет ограничить модуль счета в соответствии с выбранным - схема будет начинать счет не с нуля, а с заданного значения. Схема наращивания разрядности счетчиков организуется последовательная путем подачи выхода переполнения счетчика предыдущего десятичного разряда на счетный вход последующего разряда. Счетчики удобно включить в режим инкрементирования. Входные импульсы устройства необходимо подавать на счетный вход счетчика единиц, а выходные импульсы необходимо снимать с выхода переполнения счетчика сотен. Для выбора элементной базы можно воспользоваться источниками, указанными в предыдущих заданиях. При выборе необходимо обратить внимание на быстродействие микросхем счетчиков. Оно должно быть достаточным для восприятие входных импульсов с частотой, указанной в исходных данных.

ЗАДАНИЕ 9

Разработать электрические структурную, функциональную и принципиальную схемы сумматора двух двоичных восьмиразрядных чисел со знаком в диапазоне их десятичных эквивалентов 127. Признаком знака считать значение старшего восьмого разряда входных кодов: 1 в этом разряде соответствует отрицательному числу, а 0 – положительному. Логические уровни напряжений совместимы с ТТЛ. Выходной код результата индицировать в виде десятичного числа на трехразрядном семисегментном десятичном индикаторе, снабженном дополнительной индикацией знака в виде отдельного сегмента или светодиода. В структуре устройства использовать преобразователь прямых кодов в дополнительные и обратно, собранный на логических микросхемах.

Рекомендации по выполнению задания 9:

Для представления целых чисел фиксированной разрядности со знаком в двоичной системе счисления для отображения знака используется самый старший разряд. По заданию таким разрядом является восьмой разряд. Для выполнения арифметических операций над числами со знаком используются обычно дополнительные коды. Дополнительный код положительного числа совпадает с его прямым кодом с нулем в знаковом разряде. Дополнительный код отрицательного числа находится по следующему правилу:

инвертируются все значащие разряды;

прибавляется арифметически к полученному результату инвертирования единица;

в старшем знаковом разряде в качестве признака отрицательного числа записывается единица.

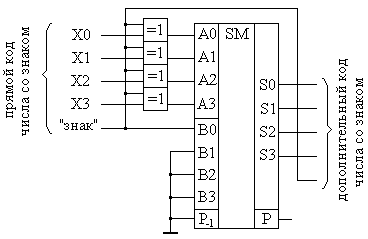

Исходя из приведенного правила должна строиться и схема преобразователя в дополнительный код. Учитывая, что знаковый разряд определяет, будет ли выполняться инверсия входных разрядов и прибавление единицы, то очевидно, что этот разряд должен быть управляющим для преобразователя. Если в нем ноль, то преобразование выполняться не будет, если единица, то будет. В схеме нужно применить управляемые инверторы. Такими элементами могут быть вентили «исключающее ИЛИ». При подаче знаковой единицы на один из входов элемента «исключающее ИЛИ», на его выходе будет формироваться инверсное значение уровня, подаваемого на второй вход. Для реализации суммирования с единицей в случае отрицательного числа можно использовать сумматор, на вход числа A которого подается код с выходов элементов «исключающее ИЛИ», а на самый младший разряд входа числа B – значение знакового разряда. Схема такого преобразователя для четырехразрядного числа со знаковым пятым разрядом приведена на рис.8. По заданию требуется обрабатывать числа в диапазоне 127, что явно не укладывается в пятиразрядный формат. Поэтому необходимо определить требуемую разрядность преобразователя и использовать соответствующий сумматор или повысить разрядность путем включения в схему необходимого количества сумматоров меньшей разрядности. Поскольку оба складываемых числа по заданию представлены в формате со знаком в одинаковом диапазоне значений, то таких преобразователей на входе устройства должно быть два по одному для каждого числа.

Далее необходимо выполнить суммирование дополнительных кодов, что не представляет трудностей. Студенту необходимо реализовать схему сумматора на необходимое количество разрядов.

Рис.8. Схема преобразователя в дополнительный код для четырехразрядного числа с пятым знаковым разрядом.

Код результата суммирования определяется следующим образом. Если в знаковом разряде результата получился ноль, то результат положителен и представлен в прямом коде. Если в знаковом разряде получилась единица, то результат отрицателен и представлен в дополнительном коде. Поскольку по заданию результат требуется отобразить на семисегментных индикаторах в виде десятичных чисел, то очевидно, что отрицательные значения результата необходимо из дополнительного кода перевести в прямой. Правило перевода из дополнительного кода в прямой такое же, как и из прямого кода в дополнительный. Т.е. преобразователь дополнительного кода в прямой будет иметь такую же схему, что и преобразователь прямого кода в дополнительный.

Далее полученный прямой код результата суммирования необходимо отобразить на семисегментном трехразрядном индикаторе. Для этого двоичный код результата необходимо преобразовать в двоично-десятичный с помощью двоично-десятичного преобразователя. А затем двоично-десятичный код единиц, десятков и сотен необходимо преобразовать в семисегментный с помощью семисегментных преобразователей. Рекомендации по организации схем двоично-десятичного и семисегментного преобразователей такие же, как и в задании 1. Самый старший знаковый разряд результата нужно вывести на сегмент индикатора «-». В качестве такого сегмента можно использовать сегмент «g» четвертого семисегментного индикатора или просто отобразить его светодиодом. Для выбора элементной базы можно воспользоваться [4].

ЗАДАНИЕ 10

Разработать электрические структурную, функциональную и принципиальную схемы арифметического перемножителя двух четырехразрядных двоичных кодов положительных целых чисел с индикацией результата на трехразрядном семисегментном десятичном индикаторе. Логические уровни напряжений совместимы с ТТЛ.

Рекомендации по выполнению задания 10:

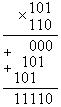

Правила выполнения арифметических действий в двоичной системе счисления наиболее просты. Умножение в двоичном коде выполняется аналогично умножению десятичных чисел – столбиком. Приведем в качестве примера выполнение умножения столбиком двух трехразрядных двоичных чисел:

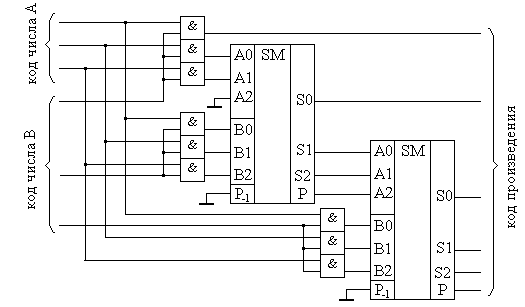

Из примера видно, что умножение реализуется операциями суммирования и сдвига. Существует несколько методов построения умножителей. Наиболее проста в схемотехнической реализации матричная организация перемножителя, показанная для трехразрядных положительных двоичных чисел на рис.9. Для формирования произведения трехразрядных двоичных чисел требуется вычислить три частичных произведения. Обратите внимание, что в двоичной арифметике требуется выполнять умножение только на числа 0 и 1. Поскольку в одном разряде правила выполнения арифметического и логического умножений совпадают, то для формирования частичного произведения можно воспользоваться логическими элементами «2И».

Для формирования частичного произведения, кроме операции умножения на один разряд, требуется осуществлять его сдвиг влево на число разрядов, соответствующее весу разряда множителя. Сдвиг можно осуществить простым соединением соответствующих разрядов частичных произведений к необходимым разрядам двоичных сумматоров. Первый сумматор суммирует первое и второе частные произведения. При этом самый младший разряд первого частного произведения согласно примеру не нуждается в суммировании. Поэтому он подаётся на выход умножителя непосредственно. А два остальных разряда первого частного произведения подаются на входы A первого сумматора со смещением вправо на один разряд. На свободный старший разряд входов A первого сумматора достаточно подать незначащий ноль (т.е. просто заземлить этот вход). Второе частное произведение подается на входы B первого сумматора без смещения. Точно таким же образом осуществляется суммирование третьего частного произведения. Отличие заключается только в том, что на старший разряд входов A второго сумматора подается сигнал переноса с выхода первого сумматора. Таким образом, сдвиг в схеме матричного перемножителя осуществляется за счет смещения на один разряд частных произведений и подачи их на входы сумматоров следующих разрядов с номерами, на единицу меньшими.

Рис.9. Схема матричного перемножителя трехразрядных двоичных положительных чисел.

По заданию требуется организовать перемножитель четырехразрядных двоичных кодов. Поэтому студенту необходимо повысить разрядность схемы, приведенной на рис9.

Для индикации результата умножения на индикаторе необходимо выходной двоичный код результата умножения преобразовать в двоично-десятичный и далее через семисегментные преобразователи вывести на семисегментные индикаторы. Организацию двоично-десятичных и семисегментных преобразователей можно выполнить по рекомендациям к заданию 1. Элементную базу можно подобрать согласно [4].

Рекомендуемая литература:

1. Электронная версия конспекта «Электроника и микропроцессорная техника. Ч1» каф.ИСИТ.

2. Электронная версия конспекта «Электроника и микропроцессорная техника. Ч2. каф. ИСИТ.

3. Микросхемы АЦП и ЦАП. Справочник. Изд-во Додека. 2005.

4. Бирюков С.А. Применение цифровых микросхем серий ТТЛ и КМОП. Справочник. Изд-во «ДМК», 2000.

5. Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. Учебник для вузов. М.: Высшая школа, 2005.

Приложение 1

Московский Государственный Открытый Университет

Факультет__________________ Кафедра______________________

Специальность_____________________________________________

Задание

На курсовой проект_____________________________________

(Ф.И.О.)

__________________________шифр_____________________

1.Тема работы_____________________________________________

__________________________________________________________

2.Исходные данные_________________________________________

__________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________________

3.Содержание пояснительной записки

________________________________________________________________________________________________________________________________________________________________________________________________________________________________________

4.Перечень графического материала

________________________________________________________________________________________________________________________________________________________________________________________________________________________________________

5.Дата выдачи задания_______________________________________

6.Срок сдачи проекта________________________________________

Задание выдал _____________________ _________________

(подпись)

Задание принял_____________________ _________________

(подпись)