- •Введение

- •1.1 Асинхронный счетчик

- •1.2 Синхронный счетчик

- •2 Разработка и обоснование функциональной схемы устройства

- •Функциональная схема устройства

- •2.2 Функциональная схема блока питания

- •3 Разработка полной принципиальной схемы устройства, расчет элементов и выходных параметров схемы

- •3.1 Выбор элементов устройства

- •3.2 Расчет однополярного блока питания для счетчика на 5 в

- •3.3 Расчет второго однополярного блока питания 15 в

- •Список литературы

Оглавление

Введение 4

4

1.1 Асинхронный счетчик 6

1.2 Синхронный счетчик 8

2 Разработка и обоснование функциональной схемы устройства 9

2.1 Функциональная схема устройства 9

2.2 Функциональная схема блока питания 11

3 Разработка полной принципиальной схемы устройства, расчет элементов и выходных параметров схемы 14

3.1 Выбор элементов устройства 14

3.2 Расчет однополярного блока питания для счетчика на 5 В 20

Напряжение не превышает 15 В – максимально возможного входного напряжения стабилизатора DA1. Кроме того, зная точно ,определяем тип конденсатора : выбираем алюминиевый конденсатор радиального типа марки К50-35, максимальное напряжение 16 В, 220 емкость мкФ. 24

3.3 Расчет второго однополярного блока питания 15 В 25

Напряжение не превышает 35 В – максимально возможного входного напряжения стабилизатора DA2. Кроме того, зная точно , определяем тип конденсатора C2: выбираем алюминиевый конденсатор радиального типа марки К50-35, максимальное напряжение 160 В, емкость 33 мкФ. Рассчитываем мощность, выделяемую на микросхеме DA2 по формуле (13): 27

Список литературы 29

Приложение А. Схема электрическая функциональная………………………30

Приложение Б. Схема электрическая принципиальная……………………….31

Приложение В. Перечень элементов принципиальной схемы….…………....32

Введение

Электроника представляет собой бурноразвивающуюся отрасль науки и техники. Она изучает физические основы и практическое применение различных электронных приборов.

Часто при использовании преобразовательных или измерительных устройств необходимо осуществить понижение частоты электрических сигналов в несколько раз. С этой задачей справляются делители частоты электрических сигналов. Делители частоты электрических сигналов в настоящее время получили очень широкое распространение в самых разнообразных видах радиоэлектронной аппаратуры, например в кварцевых и атомных часах, телевизионных устройствах синхронизации генераторов развёрток, частотомерах и других устройствах.

Основной параметр делителя частоты – коэффициент деления частоты Кд, определяемый как отношение частоты входного сигнала к частоте выходного:

(1)

(1)

где fвх – частота входного сигнала;

fвых – частота выходного сигнала делителя;

Кд – коэффициент деления.

Коэффициент деления Кд может иметь постоянное или переменное значение.

В данном курсовом проекте необходимо спроектировать делитель частоты цифровых сигналов с постоянным коэффициентом деления равным 2 и обеспечить его питание от сети 220 В, 50 Гц.

1 Принципы построения делителя частоты цифровых сигналов

Делителем частоты называется электронное устройство, предназначенное для деления частоты электрического сигнала в заданное число раз.

Для уменьшения частоты в 2, 4, 8, 16, … ,2n раз используют в качестве делителя двоичный счетчик. При появлении первого импульса произойдет переключение младшего разряда счетчика в противоположное состояние. При появлении второго импульса произойдет переключение младшего разряда в исходное состояние [4]. Таким образом, младший разряд счетчика обеспечивает деление частоты на 2. Аналогичным образом происходит деление частоты на 4, для этого надо лишь снимать нужный сигнал со 2-го разряда счетчика, который переключается в 2 раза реже, чем первый, то есть делит исходную частоту на 4. Таким же образом, 3-й разряд делит частоту на 23 = 8, 4-й на 24 = 16 и т. д. Таким образом, для деления частоты в 2n раз необходим n-разрядный счетчик.

1.1 Асинхронный счетчик

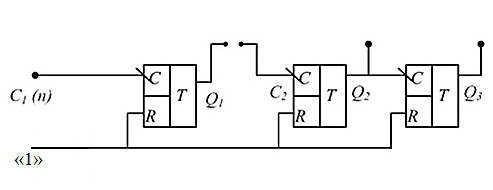

Двоичный асинхронный счетчик состоит из счетных триггеров, соединенных последовательно таким образом, чтобы выход каждого триггера был соединен со входом последующего. Пример схемы асинхронного двоичного счетчика на T-триггерах показана на рисунке 1.

Рисунок 1. Структурная схема асинхронного двоичного счетчика

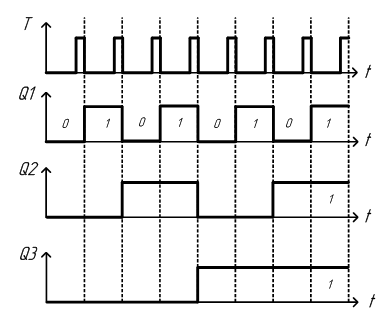

Асинхронным рассматриваемый счетчик называется потому, что в случаях прихода очередного счетного импульса срабатывает сразу несколько триггеров, их состояния изменяются не одновременно, а с некоторой задержкой относительно друг друга. Если, например, все три триггера в счетчике по схеме рисунка 1 имеют на своём выходе цифровой сигнал со значением выходного напряжения соответствующего логической единице, то очередной входной импульс изменит состояние первого триггера на противоположное. Изменение потенциала на выходе первого триггера приведет к изменению состояния второго триггера на противоположное. Выходной сигнал второго триггера в свою очередь изменит состояние третьего триггера на противоположное. Отсюда следует недостаток асинхронных счетчиков, выраженный во временной задержке между срабатываниями триггеров счетчика.

Рисунок 2. Временная диаграмма асинхронного двоичного счетчика